This is an old revision of the document!

Table of Contents

GraphGen-based Convolutional Neural Network for the ZedBoard

This page hosts a Convolutional Neural Network demo for the ZedBoard built using the GraphGen compiler.

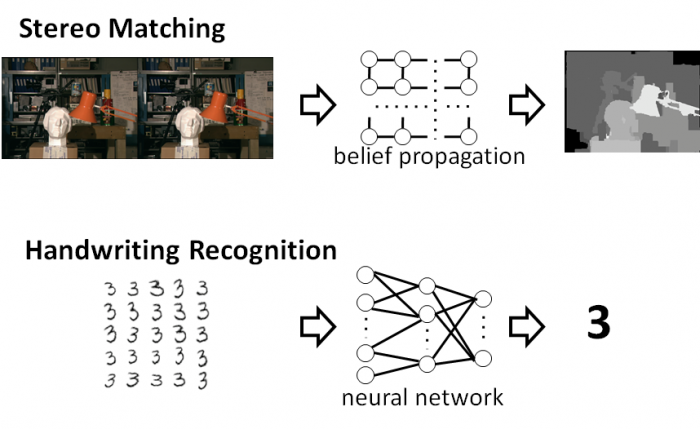

The GraphGen compiler generates complete, optimized FPGA implementations of graph computations from a high level specification. The paper (linked above) describes the operation of the GraphGen compiler in detail. Two examples of applications for the GraphGen compiler are depth reconstruction from stereo camera images through the Tree-ReWeighted message passing algorithm, and handwriting through a convolutional neural network.

In order to use the GraphGen compiler, the application developer provides:

- A description of the structure of the graph, including the types of data stored at each vertex and edge;

- An update function to apply to vertices of the graph to perform the computation. This function consists of calls to accelerator functions that are applied to the vertex, it's neighbors, and the edges connecting it to its neighbors;

- An RTL implementation of the accelerator functions used by the update function. This implementation may be generated by a C-to-gates tool

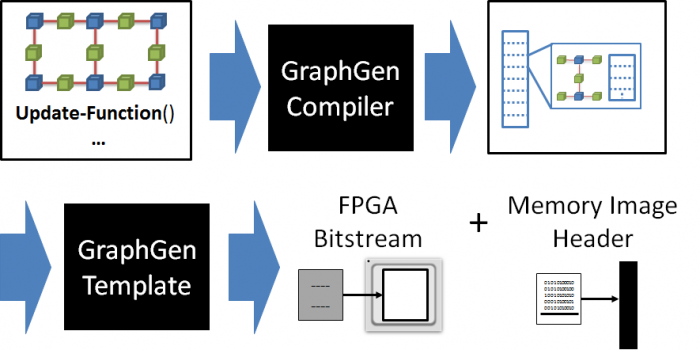

As illustrated in the image above, the GraphGen compiler partitions the graph into sub-graphs that will fit into the limited on-chip storage space of the FPGA, and generates an application that executes the graph application by fetching each sub-graph from DRAM and performing the update function on each of its vertices. The memory image header produced by the GraphGen compiler is combined with actual graph data for any instance of the computation, allowing the application to be used with any problem instance matching the graph description. Applications generated by the GraphGen compiler use the CoRAM FPGA memory abstraction to interact with DRAM and transfer data between the host computer and FPGA board.

As illustrated in the image above, the GraphGen compiler partitions the graph into sub-graphs that will fit into the limited on-chip storage space of the FPGA, and generates an application that executes the graph application by fetching each sub-graph from DRAM and performing the update function on each of its vertices. The memory image header produced by the GraphGen compiler is combined with actual graph data for any instance of the computation, allowing the application to be used with any problem instance matching the graph description. Applications generated by the GraphGen compiler use the CoRAM FPGA memory abstraction to interact with DRAM and transfer data between the host computer and FPGA board.

The Demo

This neural network demo is a handwriting recognition application that uses a publicly available neural network that recognizes handwritten digits from the MNIST data set. In our 2014 FCCM paper referenced above, we show results of accelerating this neural network on the Xilinx ML605 FPGA and Terasic DE4 FPGA using an Altera chip. This demo demonstrates the neural network on the ZedBoard, an inexpensive board that includes the Xilinx Zynq 7020 FPGA, a System-on-Chip that also includes two ARM cores. The demo uses software running on an ARM core to support host communications through the ZedBoard's ethernet interface, and communicate with the GraphGen-created processing system through an AXI slave interface. The processing system connects to the ZedBoard's DRAM through the Zynq chip's high performance AXI ports. This demo works on the original ZedBoard, and does not support the MicroZed, which uses a smaller FPGA. This demo runs through the 10,000 test images that come with the neural network on the CodeProject site.

Running the demo

All of the files needed to run the demo are located in zedboard_neural_network_demo.zip. This archive includes:

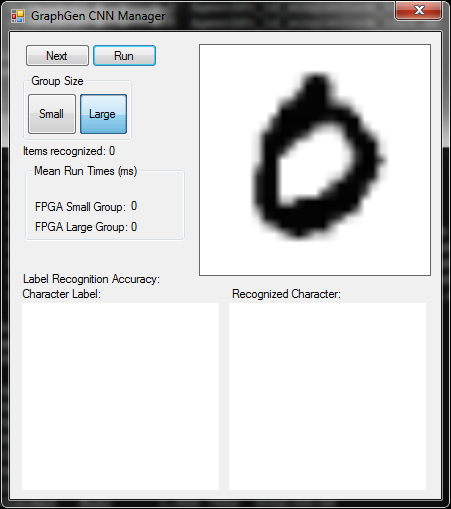

- GraphGenCNNManager.exe: A GUI program for managing the demo. This program runs on the host computer, and is written in Microsoft.net. It uses no special windows related features, and should run under Mono, although this has not been tested

- boot.bin: The system image for the ZedBoard. This file should be copied to an SD card which is then inserted into the ZedBoard's SD card reader.

- 4 data files, called dram-merge.bin, dram-merge-small.bin, t10k-images.idx3-ubyte, and t10k-labels.idx1-ubyte. These files must reside in the same directory as GraphGenCNNManager.exe.

Demo Instructions

- Configure the ZedBoard. Copy “boot.bin” from the archive onto an SD card, and put the card into the ZedBoard. Configure the ZedBoard to boot off of the SD card by setting jumpers M05 and M04 to 1, and M03 to 0, as shown in the picture below.

- Turn on the ZedBoard, and connect it to the host computer through an Ethernet cable. The ZedBoard will be configured to IP 192.168.1.10, so the host computer must be configured to be able to communicate with this IP

- Wait for the ZedBoard to finish booting. The ZedBoard has booted when the blue “done” LED to the left of the OLED display (near the bottom corner) comes on.

- Start the host control program. The host program will show the following screen: