This is an old revision of the document!

Table of Contents

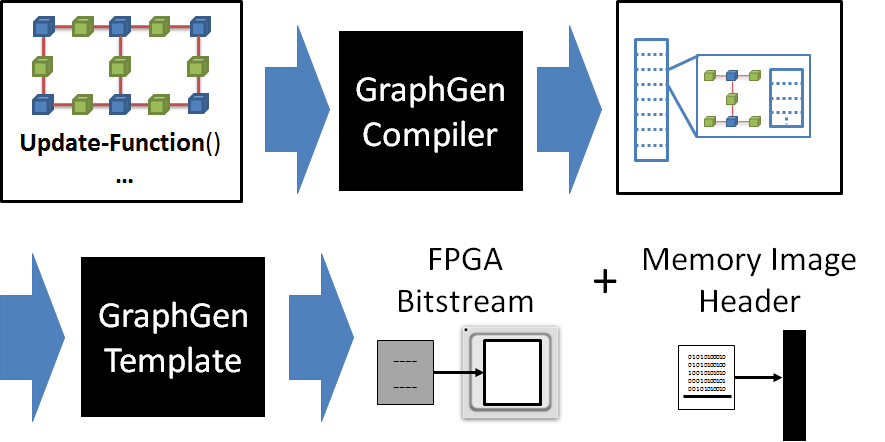

GraphGen-based Convolutional Neural Network for the ZedBoard

This page hosts a Convolutional Neural Network demo for the ZedBoard built using the GrapghGen compiler.

The GraphGen compiler generates complete, optimized FPGA implementations of graph computations from a high level specification. The paper (linked above) describes the operation of the GraphGen compiler in detail.

In order to use the GraphGen compiler, the application developer provides:

- A description of the structure of the graph, including the types of data stored at each vertex and edge;

- An update function to apply to vertices of the graph to perform the computation. This function consists of calls to accelerator functions that are applied to the vertex, it's neighbors, and the edges connecting it to its neighbors;

- An RTL implementation of the accelerator functions used by the update function. This implementation may be generated by a C-to-gates tool

As illustrated in the image above, the GraphGen compiler partitions the graph into sub-graphs that will fit into the limited on-chip storage space of the FPGA, and generates an application that executes the graph application by fetching each sub-graph from DRAM and performing the update function on each of its vertices.

As illustrated in the image above, the GraphGen compiler partitions the graph into sub-graphs that will fit into the limited on-chip storage space of the FPGA, and generates an application that executes the graph application by fetching each sub-graph from DRAM and performing the update function on each of its vertices.