### CarnegieMellor

### Today's Best Software Speech Recognizers

- Best-quality recognition is computationally *hard*

- ▼ For speaker-independent, large-vocabulary, continuous speech

- 1-10-100-1000 rule

- ▼ For **~1X** real-time recognition rate

- ▼ For ~10% word error rate (90% accuracy)

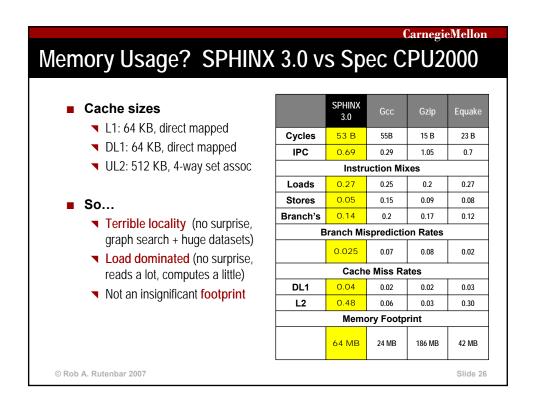

- Need ~100 MB memory footprint

- Need ~100 W power

- Need ~1000 MHz CPU

- This proves to be very *limiting* ...

© Rob A. Rutenbar 2007

© Rob A. Rutenbar 2007

Slide 3

CarnegieMellon

### The thesis: It's time to liberate speech recognition from the unreasonable limitations of software The solution: Speech recognition in silicon

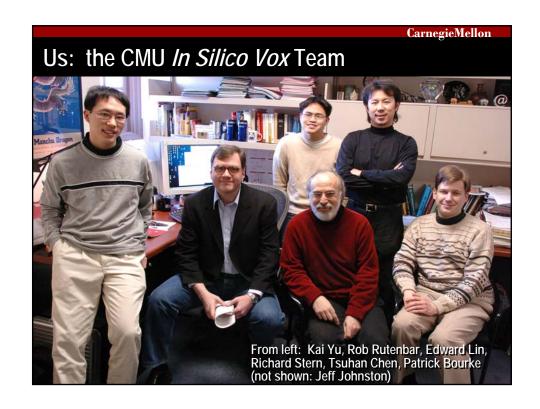

### Aside: About the Name "In Silico Vox" In Vivo Latin: an experiment done in a living organism Latin: an experiment done in an artificial lab environment Latin: an experiment done via computation only (Not real Latin): an experiment done via computation only Vox Latin: voice, or word

Slide 5

© Rob A. Rutenbar 2007

# About This Talk Some philosophy Why silicon? Why now? Why us (CMU)? A quick tour: How speech recognition works What happens in a recognizer An SoC architecture Stripping away all CPU stuff we don't need, focus on essentials Results ASIC version: Simulation results FPGA version: Live, running hardware-based recognizer

CarnegieMellon

### **About This Talk**

- Some philosophy

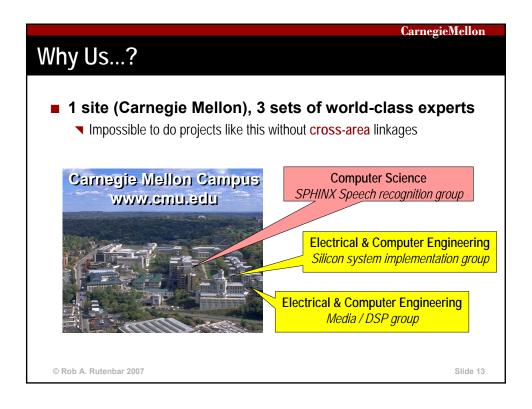

- Why silicon? Why now? Why us (CMU)?

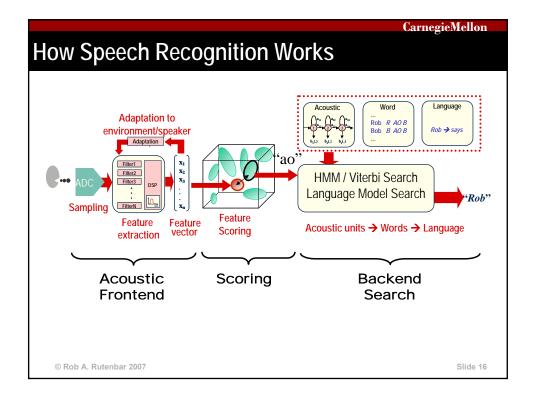

- A quick tour: How speech recognition works

- What happens in a recognizer

- An SoC architecture

- Stripping away all CPU stuff we don't need, focus on essentials

- Results

- ASIC version: Simulation results

- ▼ FPGA version: Live, running hardware-based recognizer

© Rob A. Rutenbar 2007

Slide 7

CarnegieMellon

### Why Silicon? Why Now?

### Why? Two reasons:

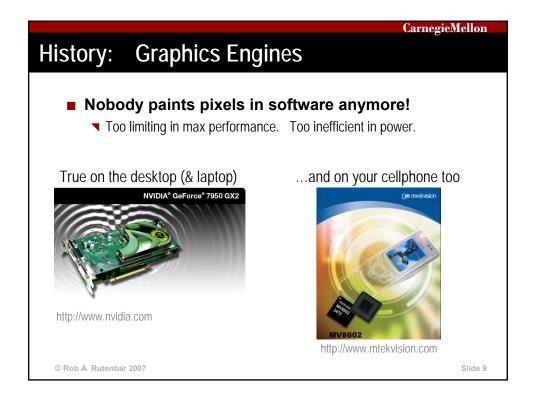

- History

- We have some successful **historical** examples of this migration

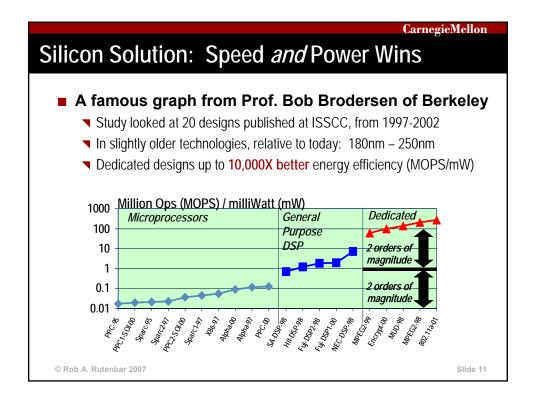

- **■** Performance

- **▼** Tomorrow's compelling apps need 100X 1000X more performance

- (Not going to happen in software)

© Rob A. Rutenbar 2007

Slide 8

## About This Talk Some philosophy Why silicon? Why now? Why us (CMU)? A quick tour: How speech recognition works What happens in a recognizer An SoC architecture Stripping away all CPU stuff we don't need, focus on essentials Results ASIC version: Simulation results FPGA version: Live, running hardware-based recognizer

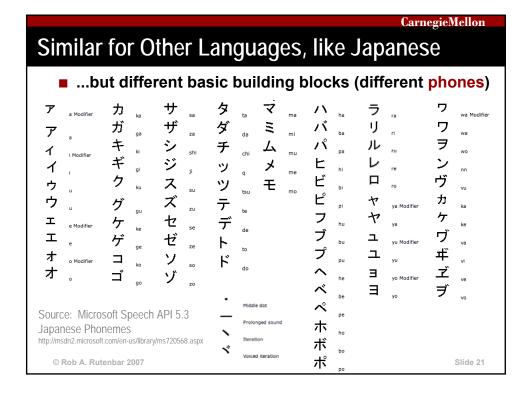

### CarnegieMellon **Example of Different Phone Building Blocks** Let's use my name as an example English: /r/ /00/ /t/ /n/ **/b/** /ar/ ルル 1111 /テ/ レン Japanese: Aside: ■ Japanese has some reputation as being an "easier" language for automatic recognition ■ Mapping from basic sounds (mora) to words is simpler than English © Rob A. Rutenbar 2007 Slide 22

CarnegieMellon

### **About This Talk**

- Some philosophy

- Why silicon? Why now? Why us (CMU)?

- A quick tour: How speech recognition works

- What happens in a recognizer

- An SoC architecture

- Stripping away all CPU stuff we don't need, focus on essentials

- Results

- ASIC version: Simulation results

- ▼ FPGA version: Live, running hardware-based recognizer

© Rob A. Rutenbar 2007

Slide 27

CarnegieMellon

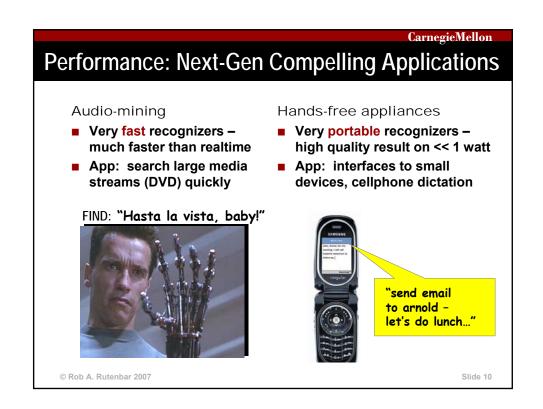

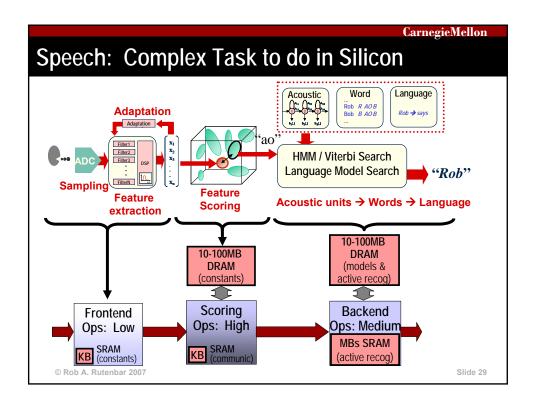

### This Talk: How to Get to Fast...

### Audio-mining

- Very fast recognizers much faster than realtime

- App: search large media streams (DVD) quickly

FIND: "Hasta la vista, baby!"

© Rob A. Rutenbar 2007

### Hands-free appliances

- Very portable recognizers high quality result on << 1 watt</li>

- App: interfaces to small devices, cellphone dictation

Slide 28

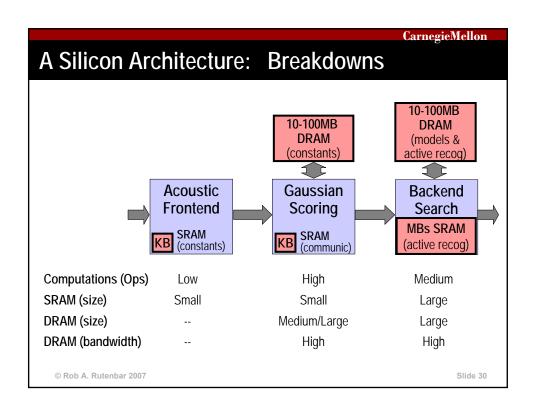

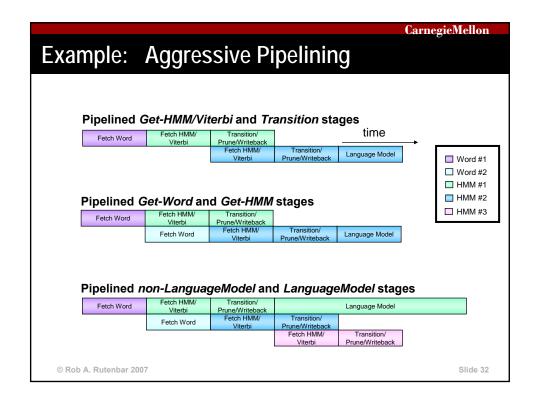

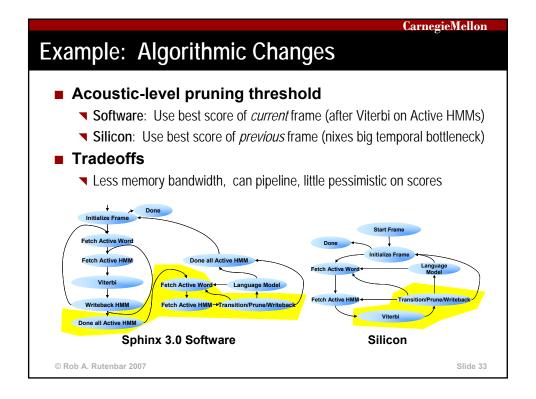

## Essential Implementation Ideas Custom precision, everywhere Every bit counts, no extras, no floating point – all fixed point (Almost) no caching Like graphics chips: fetch from SDRAM, do careful data placement (Little bit of caching for bandwidth filtering on big language models) Aggressive pipelining If we can possibly overlap computations – we try to do so Algorithm transformation Some software computations are just bad news for hardware Substitute some "deep computation" with hardware-friendly versions

### About This Talk Some philosophy Why silicon? Why now? Why us (CMU)? A quick tour: How speech recognition works What happens in a recognizer An SoC architecture Stripping away all CPU stuff we don't need, focus on essentials Results ASIC version: Simulation results FPGA version: Live, running hardware-based recognizer

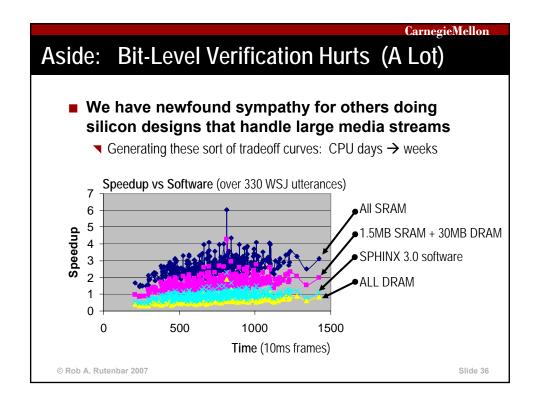

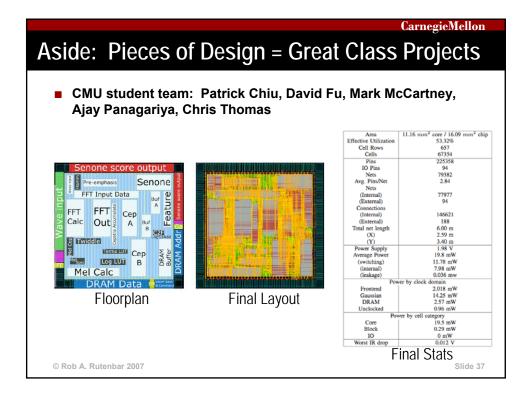

### Design Flow: C++ Cycle Simulator → Verilog 2006 benchmark: 5K-word "Wall Street Journal" task Cycle sim results: No accuracy loss; not quite 2X @ 125MHz ASIC clock ■ Backend search needs: ~1.5MB SRAM, ~30MB DRAM Speedup Over Real Time (bigger is better) 1 GHz 0.74X Software: Sphinx 3.3 (fast decoder) 7.32% Software: Sphinx 4 (single CPU) 6.97% 1 GHz 0.82X Software: Sphinx 4 (dual CPU) 6.97% 1 GHz 1.05X Software: Sphinx 3.0 (single CPU) 6.707% 2.8 GHz 0.59X Hardware: Our Proposed Recognizer 6.725% 0.125 GHz 1.67X © Rob A. Rutenbar 2007 Slide 35

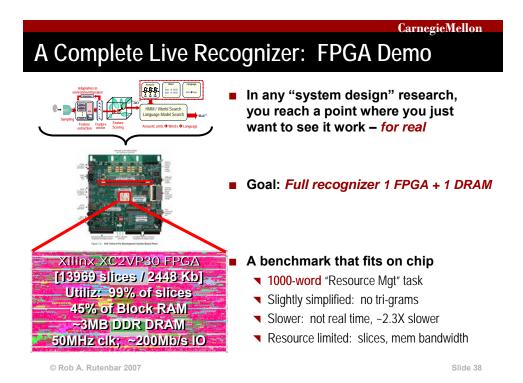

### **FPGA Experimental Results**

■ Aside: as far as we know, this is the *most complex* recognizer architecture ever fully mapped into a running, hardware-only form

© Rob A. Rutenbar 2007

Slide 39

CarnegieMellon

CarnegieMellon

### **Summary**

- Software is too constraining for speech recognition

- Evolution of graphics chips suggests alternative: **Do it in silicon**

- **▼**Compelling performance and power reasons for silicon speech recog

- Several "in silico vox" architectures in design

- **▼**SoC and FPGA versions

- ▼~10X realtime speedup architecture in progress at CMU

- Reflections

- Some of the most interesting experiences happen when you get people from very different backgrounds silicon + speech on same team

WHEN IS WINDOWS HUNILABLE

CarnegieMellon

### Acknowledgements

- **■** Work supported by

- US National Science Foundation (www.nsf.gov)

- Semiconductor Research Corporation (www.src.org)

- ▼ FCRP Focus Research Center for Circuit & System Solutions (www.fcrp.org, www.c2s2.org)

- We are grateful for the advice and speech recognition expertise shared with us by

- Richard M. Stern, CMU

- Arthur Chan, CMU

- Mosur K. Ravishankar, CMU

© Rob A. Rutenbar 2007

Slide 41