### Lecture #3

# Microcontroller Instruction Set

18-348 Embedded System Engineering Philip Koopman Wednesday, 20-Jan-2015

### April 2013: Traffic Light Heaven in L.A.

# Los Angeles syncs up all 4,500 of its traffic lights

Los Angeles is the first city in the world to synchronize all of its traffic lights, hoping to unclog its massive roadway congestion.

It has taken 30 years and \$400 million, but Los Angeles has finally synchronized its traffic lights in an effort to reduce traffic congestion, becoming the first city in the world to do so.

Mayor Antonio R. Villaraigosa said with the 4,500 lights now in sync, commuters will save 2.8 minutes driving five miles in Los Angeles, The New York Times reported. Villaraigosa also said that the average speed would rise more than two miles per hour on city streets and that carbon emissions would be greatly reduced as drivers spend less time starting and stopping. According to CBS News, less idling will mean a 1-ton reduction in carbon emissions every year.

| W1- # | Week of:       | Mon      | Tue      | Wed      | Thu      | Fri      | Lab Report Due                | II II             | Fri. Recitation |

|-------|----------------|----------|----------|----------|----------|----------|-------------------------------|-------------------|-----------------|

| W K # | WEEK OI.       | (Sec E)  | (Sec A)  | (Sec B)  | (Sec C)  | (Sec D)  | Wednesday                     | Friday            | Discusses Labs  |

| 111 1 | 11-Jan<br>2016 | No Lab   | No Lab   | Open Lab | Open Lab | Open Lab | None                          | 1                 | 1, 2            |

| 2     | 18-Jan         | MLK Day  | 1        | 1        | 1        | 1        | None                          | 2                 | 2, 3            |

| 3     | 25-Jan         | 1        | 2        | 2        | 2        | 2        | 1                             | 3                 | 3, 4            |

| 4     | 1-Feb          | 2        | 3        | 3        | 3        | 3        | 2                             | 4                 | 4, 5            |

| 5     | 8-Feb          | 3        | 4        | 4        | 4        | 4        | 3                             | 5                 | 5, 6            |

| 6     | 15-Feb         | 4        | 5        | 5        | 5        | 5        | 4                             | 6                 | 6, 7            |

| 7     | 22-Feb         | 5        | Open Lab | Open Lab | Open Lab | 6        | None                          | None              | 7, 8            |

| 8     | 29-Feb         | 6        | 6        | 6        | 6        | BREAK    | 5                             | 7 Due<br>Thursday | No Recitation   |

|       | 7-Mar          | SPRING   | BREAK    | SPRING   | BREAK    | BREAK    | None                          | None              | No Recitation   |

| 9     | 14-Mar         | Open Lab | Open Lab | 7        | 7        | 7        | 6                             | 8                 | 8, 9            |

| 10    | 21-Mar         | 7        | 7        | 8        | 8        | 8        | 7                             | 9                 | 9, 10           |

| 11    | 28-Mar         | 8        | 8        | 9        | 9        | 9        | 8                             | 10                | 10, 11          |

| 12    | 4-Apr          | 9        | 9        | 10       | 10       | 10       | 9                             | 11                | 11              |

| 13    | 11-Apr         | 10       | 10       | Open Lab | Carnival | Carnival | None                          | None              | No Recitation   |

| 14    | 18-Apr         | Open Lab | 10                            | None              | Optional/In-Lab |

| 15    | 25-Apr         | Open Lab | None                          | None              | Optional/In-Lab |

| 16    | 2-May Finals   | TBD      | TBD      | TBD      | TBD      | TBD      | 11 Due<br>( <u>Thursday</u> ) | None              | No Recitation   |

<sup>(\*</sup>See blackboard for Lab 11 prelab demo & writeup information)

### Where Are We Now?

#### Where we've been:

Embedded Hardware

### Where we're going today:

• Instruction set & Assembly Language

#### Where we're going next:

- More assembly language

- Engineering process

- Embedded C

- Coding tricks, bit hacking, extended-precision math

### **Preview**

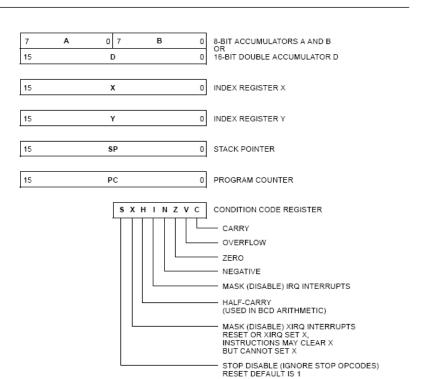

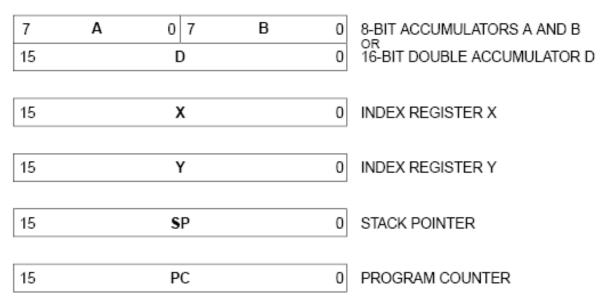

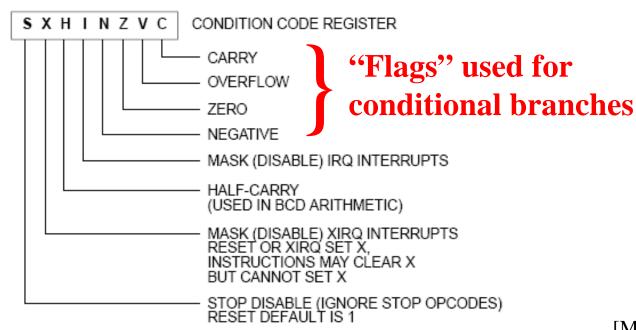

### **♦** Programmer-visible architecture

- Registers

- Addressing modes

### Branching

- Types of branches

- How condition codes are set

### Assembly/Disassembly

Review of how instructions are encoded

### Timing

How long does an instruction take to execute? (simple version)

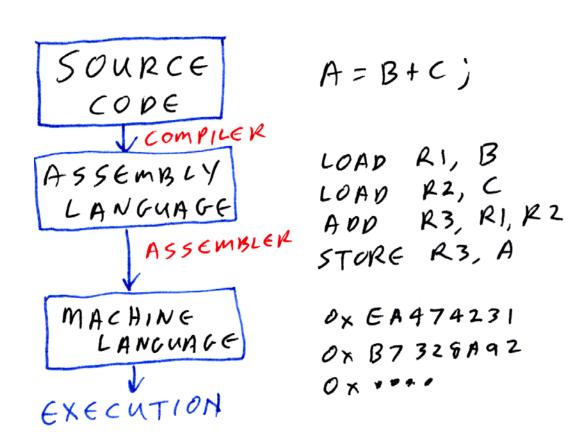

## Where Does Assembly Language Fit?

#### Source code

- High level language (C; Java)

- Variables and equations

- One-to-many mapping with assembly language

### Assembly language

- Different for each CPU architecture

- Registers and operations

- Usually one-to-one mapping to machine language

### Machine language

- Hex/binary bits

- Hardware interprets to execute program

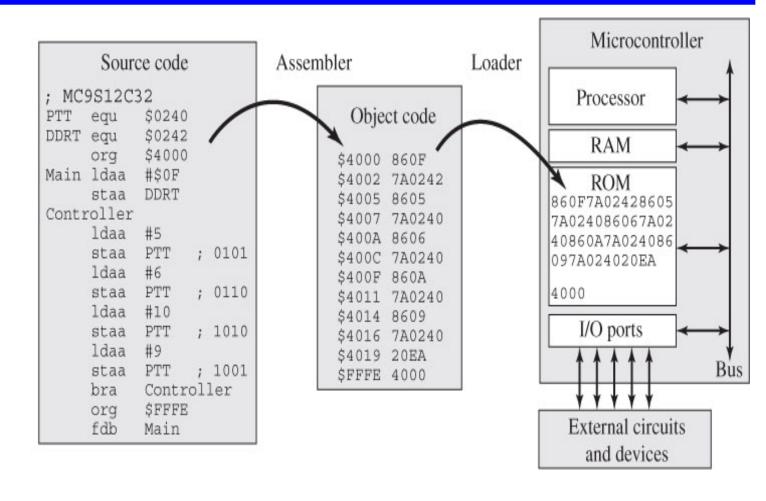

### **Assembler To ROM Process**

# Figure 2.1 Assembly language development process.

[Valvano]

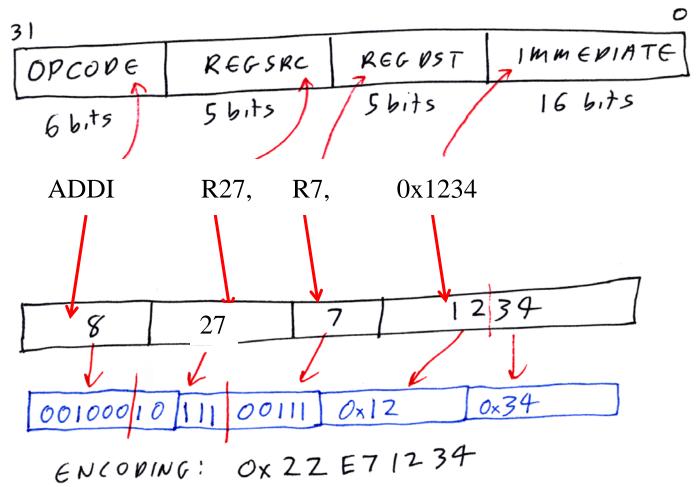

### **RISC Instruction Set Overview**

- **◆** Typically simple encoding format to make hardware simpler/faster

- Classical Example: MIPS R2000

- $R7 \le R27 + 0x1234$

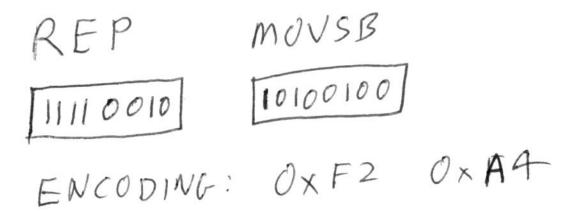

### **CISC Instruction Set Overview**

- Complex encoding for small programs

- Classical Example: VAX; Intel 8088

- REP MOVSB

(8088 String move)

- Up to 64K bytes moved; source in SI reg; dest in DI reg; count in CX

### **Accumulator-Based Microcontrollers**

- ♦ Usually one or two "main" registers "accumulators"

- Historically called register "A" or "Acc" or registers "A" and "B"

- This is where the Pentium architecture gets "AX, BX, CX, DX" from

- **♦** Usually one or more "index" registers for addressing modes

- Historically called register "X" or registers "X" and "Y"

- In the Pentium architecture these correspond to SI and DI registers

- $\bullet$  A typical "H = J + K" operation is usually accomplished via:

- Load "J" into accumulator

- Add "K" to "J", putting result into accumulator

- Store "H" into memory

- Reuse the accumulator for the next operation (no large register file)

- **♦** Usually microcontrollers are resource-poor

- E.g., No cache memory for most 16-bit micros!

### **CPU12 Resource – Long Version**

#### CPU12

Reference Manual

#### **DECA**

Decrement A

#### **DECA**

#### Operation:

$$(A) - \$01 \Rightarrow A$$

#### Description:

Subtract one from the content of accumulator A.

The N, Z, and V status bits are set or cleared according to the results of the operation. The C status bit is not affected by the operation, thus allowing the DEC instruction to be used as a loop counter in multiple-precision computations.

CCR Details:

| s | Х | Н |   | N | Z | ٧ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | Δ | Δ | Δ | - |

- N: Set if MSB of result is set; cleared otherwise

- Z: Set if result is \$00; cleared otherwise

- V: Set if there was a two's complement overflow as a result of the operation; cleared otherwise. Two's complement overflow occurs if and only if (A) was \$80 before the operation.

| Source Form | Address | Object Code | Access Detail |         |  |  |  |

|-------------|---------|-------------|---------------|---------|--|--|--|

| Source Form | Mode    | Object Code | HCS12         | M68HC12 |  |  |  |

| DECA        | INH     | 43          | 0             | 0       |  |  |  |

CPU12 Reference Manual, Rev. 4.0

## **CPU12 Resource – Summary Version**

CPU12RG/D

Reference Guide

CPU12RG/D Rev. 2, 11/2001

CPU12 Reference Guide (for HCS12 and original M68HC12)

Figure 1. Programming Model

#### Instruction Set Summary (Sheet 2 of 14)

| Source Form                         | Operation                                                                 | Addr.           | Machine                       |                  | Access Detail    | SXHI | NZVO |

|-------------------------------------|---------------------------------------------------------------------------|-----------------|-------------------------------|------------------|------------------|------|------|

| Source Forth                        | Operation                                                                 | Mode            | Coding (hex)                  | HCS12            | HC12             | SYHI | MZVC |

| ASL opr16a                          |                                                                           | EXT             | 78 hh 11                      | rPwO             | roPw             |      | ΔΔΔ  |

| ASL oprx0_xysp                      | I                                                                         | IDX             | 68 xb                         | rPw              | rDv              |      | 1    |

| ASL oprx9,xysp                      | \( \frac{1}{4} \frac{1}{1} \rm        | IDX1            | 68 xb ff                      | rPw0             | rPOw             |      | 1    |

| ASL oprx16,xysp                     | Arithmetic Shift Left                                                     | IDX2<br>ID.IDX1 | 68 xbeeff                     | frPwP            | frDDv            |      | 1    |

| ASL [D,xysp]<br>ASL [apax16.xvsp]   | Arithmetic Shift Left                                                     | (IDX2)          | 68 xb<br>68 xbeeff            | fifrDw           | fifrPv           |      | l    |

| ASLA                                | Arithmetic Shift Left Accumulator A                                       | INH             | 48                            | CIPERA           | LIDIM            |      | 1    |

| ASLB                                | Arithmetic Shift Left Accumulator B                                       | INH             | 58                            | o                | 0                |      |      |

| ASLD                                | C b7 A b0 b7 B b0  Arithmetic Shift Left Double                           | INH             | 59                            | 0                | ٥                |      | ΔΔΔ  |

| ASR opr16a                          | _                                                                         | EXT             | 77 hh 11                      | rPwO             | rOPw             |      | ΔΔΔ  |

| ASR oprx0_xysp                      |                                                                           | IDX             | 67 ado                        | rPw              | rPv              |      |      |

| ASR oprx9,xysp                      | <b>└→</b> []]]]                                                           | IDX1            | 67 xdb ff                     | rPw0             | rPOw             |      | l    |

| ASR oprx16,xysp                     | b7 b0 €                                                                   | IDX2            | 67 xbeeff                     | frPwP            | frDDv            |      | 1    |

| ASR [D,xysp]                        | Arithmetic Shift Right                                                    | [D,IDX]         | 67 xb<br>67 xb ee ff          | flfrDv           | fifrPv           |      | l    |

| ASR [apox16,xysp]<br>ASRA           | Arithmetic Shift Right Accumulator A                                      | [IDX2]          | 47                            | fiprpv           | fIPrPw           |      |      |

| ASRB                                | Arithmetic Shift Right Accumulator B                                      | INH             | 57                            | o                |                  |      |      |

| BCC rei8                            | Branch if Carry Clear (if C = 0)                                          | REL             | 24 rr                         | ppp/pl           | ppp/pl           |      |      |

| BCLR opr8a, msk8                    | (M) + (mm) ⇒ M                                                            | DIR             | 4D dd mn                      | rPw0             | rPOw             |      | ΔΔ0- |

| BCLR opr16a, msk8                   | Clear Bit(s) in Memory                                                    | EXT             | 1D hh 11 mm                   | rPwD             | rPPw             |      | 1    |

| BCLR oprx0_xysp, msk8               |                                                                           | DX              | OD sdb mm                     | rPw0             | rPOw             |      | l    |

| BCLR oprx9,xysp, msk8               |                                                                           | IDX1            | OD xb ff mm<br>OD xb ee ff mm | rPwD             | rDwD             |      | 1    |

| BCLR oprx16,xysp, msk8<br>BCS rei8  | Branch if Carry Set (if C = 1)                                            | IDX2<br>REL     | 25 rr                         | frPwPO<br>ppp/pl | frPwOP<br>ppp/pl |      |      |

| BEO rei8                            | Branch if Equal (if Z = 1)                                                | REL             | 25 rr<br>27 rr                | DDD/D1           |                  |      |      |

| BGE rei8                            | Branch if Greater Than or Equal                                           | REL             | 20 rr                         | DDD/D1           | DDD/D1<br>DDD/D1 |      |      |

| DGE 780                             | (if N ⊕ V = 0) (signed)                                                   | KEL             | 20 11                         | 200/0-           | 220/2            |      |      |

| BGND                                | Place CPU in Background Mode<br>see CPU12 Reference Manual                | INH             | 00                            | Vfppp            | VIDDD            |      |      |

| BGT rei®                            | Branch if Greater Than<br>(if Z + (N ⊕ V) = 0) (signed)                   | REL             | 2E rr                         | DDD/D1           | DDD/D1           |      |      |

| BHI rel8                            | Branch if Higher<br>(if C + Z = 0) (unsigned)                             | REL             | 22 rr                         | DDD/D1           | DDD/D1           |      |      |

| BHS rei®                            | Branch if Higher or Same<br>(if C = 0) (unsigned)<br>same function as BCC | REL             | 24 rr                         | DDD/D1           | ppp/pl           |      |      |

| BITA #opr∂i                         | (A) * (M)                                                                 | IMM             | 85 ii                         | p                | p                |      | ΔΔ0- |

| BITA o pr8a                         | Logical AND A with Memory                                                 | DIR             | 95 dd                         | rPf              | rfD              | l    |      |

| BITA opr16a                         | Does not change Accumulator or Memory                                     | EXT             | B5 hh 11                      | rPO              | rop              | l    |      |

| BITA opnx0_xysp                     |                                                                           | IDX<br>IDX1     | A5 xb<br>A5 xb ff             | rPf<br>rPO       | rfP<br>rPO       | l    |      |

| BITA oprx9,xysp<br>BITA oprx16,xysp |                                                                           | IDX1            | A5 xb ee ff                   | frpp             | frpp             | l    |      |

| BITA [D,xysp]                       |                                                                           | ID,IDX1         | A5 xb ee 11                   | flfrpf           | flfrfp           | l    |      |

| BITA [oprx16,xysp]                  |                                                                           | [IDX2]          | A5 xbeeff                     | fiprof           | fiprfp           |      |      |

| BITB #opr8i                         | (B) • (M)                                                                 | IMM             | CS ii                         | D                | D                |      | ΔΔ0  |

| BITB opr8a                          | Logical AND B with Memory                                                 | DIR             | DS dd                         | rPf              | rfD              | l    |      |

| BITB opr16a                         | Does not change Accumulator or Memory                                     | EXT<br>IDX      | F5 hh 11<br>E5 xb             | rPO<br>rPf       | rop              | l    |      |

| BITB opnx0_xysp<br>BITB opnx9,xysp  |                                                                           | IDX1            | ES ab ff                      | rPf              | rfP<br>rPO       | l    |      |

| BITB opex 16 xysp                   |                                                                           | IDX2            | E5 xbeeff                     | frpp             | frDD             | l    |      |

| BITB [D,xysp]                       |                                                                           | [D,IDX]         | E5 xb                         | flfrpf           | flfrfD           | l    |      |

| BITB [aprx16,xysp]                  |                                                                           | [IDX2]          | E5 xbeeff                     | fiprof           | fiPrfP           | l    |      |

| BLE reiß                            | Branch if Less Than or Equal<br>(if Z + (N ⊕ V) = 1) (signed)             | REL             | 2F rr                         | PPP/P1           | DDD/D1           |      |      |

| BLO rel8                            | Branch if Lower                                                           | REL             | 25 rr                         | ppp/pl           | DDD/D1           |      |      |

|                                     | (if C = 1) (unsigned)<br>same function as BCS                             |                 |                               |                  |                  |      |      |

Note 1, PPP/P indicates this instruction takes three cycles to refill the instruction queue if the branch is taken and one program fetch cycle if the branch is not taken.

# "CPU12" Programming Model – (MC9S12C128)

D is really just A:B

NOT a separate register!

### **The CPU12 Reference Guide**

### **♦** Summarizes assembly language programming info

• Lots of info there .... This lecture is an intro to that material

| Source Form        | Operation                                 | Addr.<br>Mode | Machine<br>Coding (hex) | Access Detail<br>HCS12 | HC12            | SXHI       | NZVC |

|--------------------|-------------------------------------------|---------------|-------------------------|------------------------|-----------------|------------|------|

| ABA                | (A) + (B) ⇒ A<br>Add Accumulators A and B | INH           | 18 06                   | ∞                      | 00              | Δ-         | ΔΔΔΔ |

| ABX                | (B) + (X) ⇒ X<br>Translates to LEAX B,X   | IDX           | 1A E5                   | Pf                     | PP <sup>1</sup> |            |      |

| ABY                | (B) + (Y) ⇒ Y<br>Translates to LEAY B,Y   | IDX           | 19 ED                   | Pf                     | PP <sup>1</sup> |            |      |

| ADCA #opr8i        | $(A) + (M) + C \Rightarrow A$             | IMM           | 89 ii                   | P                      | P               | A -        | ΔΔΔΔ |

| ADCA opr8a         | Add with Carry to A                       | DIR           | 99 dd                   | rPf                    | rfP             |            |      |

| ADCA opr16a        |                                           | EXT           | B9 hh 11                | rPO                    | rop             |            |      |

| ADCA oprx0_xysp    |                                           | IDX           | A9 xb                   | rPf                    | rfP             |            |      |

| ADCA oprx9,xysp    |                                           | IDX1          | A9 xb ff                | rPO                    | rPO             |            |      |

| ADCA oprx16,xysp   |                                           | IDX2          | A9 xb ee ff             | frPP                   | frPP            |            |      |

| ADCA [D,xysp]      |                                           | [D,IDX]       | A9 xb                   | fIfrPf f               | lPrfP           |            |      |

| ADCA [oprx16,xysp] |                                           | [IDX2]        | A9 xb ee ff             | fIPrPf f               | IPrfP           |            |      |

| ADCB #opr8i        | $(B) + (M) + C \Rightarrow B$             | IMM           | C9 ii                   | P                      | P               | <u>-</u> - | ΔΔΔΔ |

| ADCB opr8a         | Add with Carry to B                       | DIR           | D9 dd                   | rPf                    | rfP             |            |      |

| ADCB opr16a        |                                           | EXT           | F9 hh 11                | rPO                    | rOP             |            |      |

# **ALU Operations – Addition as an Example**

#### "Inherent" address modes:

ABA

(B) + (A) => A

$\underline{\mathbf{A}}$ dd accumulator  $\underline{\mathbf{B}}$  to  $\underline{\mathbf{A}}$

- Encoding: 18 06

- ABX

- (B) + (X) => X

$\underline{\mathbf{A}}$ dd accumulator  $\underline{\mathbf{B}}$  to  $\underline{\mathbf{X}}$

- Encoding: 1A E5

### **Immediate Operand:**

- ADDD #value (D) + ij:kk => D Add to **D**

- Add constant value to D (example:  $D \le D + 1234$ )

- Encoding: C3 jj kk

- Example: ADDD #\$534

Adds hex 534 (0x534) to D reg

### "Extended" operand – location in memory at 16-bit address:

- ADDD address (D) + [HH:LL] => D

- Add to D

- Fetch a memory location and add to D

- Encoding: F3 HH LL

- Example: ADDD \$5910

- Adds 16-bit value at \$5910 to D

- NOTE: "[xyz]" notation means "Fetch from address xyz"

### **Address Modes**

#### Address Modes

```

IMM

Immediate

IDX

— Indexed (no extension bytes) includes:

5-bit constant offset

Pre/post increment/decrement by 1 . . . 8

Accumulator A, B, or D offset

IDX1

9-bit signed offset (1 extension byte)

IDX2

— 16-bit signed offset (2 extension bytes)

[D, IDX] — Indexed indirect (accumulator D offset)

[IDX2]

Indexed indirect (16-bit offset)

INH

Inherent (no operands in object code)

REL

2's complement relative offset (branches)

Direct (8-bit memory address with zero high bits)

DIR

EXT

Extended (16-bit memory address)

```

### **Instruction Description Notation**

```

abc — A or B or CCR

abcdxys — A or B or CCR or D or X or Y or SP. Some assemblers also allow T2 or T3.

abd — A or B or D

abdxys — A or B or D or X or Y or SP

dxvs — D or X or Y or SP

msk8 — 8-bit mask, some assemblers require # symbol before value

opr8i — 8-bit immediate value

opr16i — 16-bit immediate value

opr8a — 8-bit address used with direct address mode

opr16a — 16-bit address value

oprx0_xysp — Indexed addressing postbyte code:

oprx3,-xys Predecrement X or Y or SP by 1 . . . 8

oprx3,+xys Preincrement X or Y or SP by 1 . . . 8

oprx3,xys- Postdecrement X or Y or SP by 1 . . . 8

oprx3,xys+ Postincrement X or Y or SP by 1 . . . 8

oprx5,xysp 5-bit constant offset from X or Y or SP or PC

abd,xysp Accumulator A or B or D offset from X or Y or SP or PC

oprx3 — Any positive integer 1 . . . 8 for pre/post increment/decrement

oprx5 — Any value in the range -16 . . . +15

oprx9 — Any value in the range -256 . . . +255

oprx16 — Any value in the range -32,768 . . . 65,535

page — 8-bit value for PPAGE, some assemblers require # symbol before this value

rel8 — Label of branch destination within -256 to +255 locations

rel9 — Label of branch destination within -512 to +511 locations

rel16 — Any label within 64K memory space

trapnum — Any 8-bit value in the range $30-$39 or $40-$FF

xys — X or Y or SP

xvsp — X or Y or SP or PC

```

### **Notation for Encoding of Instruction Bytes**

#### **Machine Coding**

- dd 8-bit direct address \$0000 to \$00FF. (High byte assumed to be \$00).

- ee High-order byte of a 16-bit constant offset for indexed addressing.

- eb Exchange/Transfer post-byte. See Table 3 on page 23.

- ff Low-order eight bits of a 9-bit signed constant offset for indexed addressing, or low-order byte of a 16-bit constant offset for indexed addressing.

- hh High-order byte of a 16-bit extended address.

- ii 8-bit immediate data value.

jj — High-order byte of a 16-bit immediate data value.

- kk Low-order byte of a 16-bit immediate data value.

- 1b Loop primitive (DBNE) post-byte. See Table 4 on page 24.

- 11 Low-order byte of a 16-bit extended address.

- mm 8-bit immediate mask value for bit manipulation instructions. Set bits indicate bits to be affected.

- pg Program page (bank) number used in CALL instruction.

- qq High-order byte of a 16-bit relative offset for long branches.

- tn Trap number \$30–\$39 or \$40–\$FF.

- Signed relative offset \$80 (-128) to \$7F (+127).

Offset relative to the byte following the relative offset byte, or low-order byte of a 16-bit relative offset for long branches.

- xb Indexed addressing post-byte. See Table 1 on page 21 and Table 2 on page 22.

# **ALU Operations – Addition Example Revisited**

#### "Inherent" address modes:

ABA

(B) + (A) => A

$\underline{\mathbf{A}}$ dd accumulator  $\underline{\mathbf{B}}$  to  $\underline{\mathbf{A}}$

- Encoding: 18 06

- ABX

- (B) + (X) => X

$\underline{\mathbf{A}}$ dd accumulator  $\underline{\mathbf{B}}$  to  $\underline{\mathbf{X}}$

- Encoding: 1A E5

### **Immediate Operand:**

- ADDD #opr16i (D) + jj:kk => D Add to **D**

- Add constant value to D (example:  $D \le D + 1234$ )

- − Encoding:C3 jj kk

- Example: ADDD #\$534

Adds hex 534 (0x534) to D reg

### "Extended" operand – location in memory at 16-bit address:

- ADDD opr16a (D) + [HH:LL] => D

- Add to D

- Fetch a memory location and add to D

- Encoding: F3 HH LL

- Example: ADDD \$5910

Adds 16-bit value at \$5910 to D

### Immediate Operand:

- ADDD #opr16i (D) + jj:kk => D Add to **D**

- Add constant value to D (example:  $D \le D + 1234$ )

- Encoding: C3 jj kk

- Example: ADDD #\$534 Adds hex 534 (0x534) to D reg

- What C code would result in this instruction?

register int16 T; // assume that X is kept in machine register D T = T + 0x534;

### "Extended" operand – location in memory at 16-bit address:

- ADDD opr16a (D) + [HH:LL] => D  $\underline{\mathbf{Add}}$  to  $\underline{\mathbf{D}}$

- Fetch a memory location and add to D

- Encoding: F3 HH LL

- Example: ADDD \$5910 Adds 16-bit value at \$5910 to D

- What C code would result in this instruction?

static int16 B; // B is a variable that happens to be at address \$5910

$$T = T + B$$

;

- "Direct" operand location in memory at 8-bit address:

- ADDD opr8a (D) +  $[00:LL] \Rightarrow D$  Add to **D**

- Fetch a memory location and add to D; address is 0..FF ("page zero" of memory)

- Encoding: D3 LL

- Example: ADDD \$0038

- Special optimized mode for smaller code size and faster execution

- Especially for earlier 8-bit processors, but still can be useful

- Gives you 256 bytes of memory halfway between "memory" and "register" in terms of ease & speed of access

- Assembler knows to use this mode automatically based on address being \$00xx

- Result programs often optimized to store variables in first 256 bytes of RAM

- If you have very limited RAM, this is worth doing to save time & space!

- But it also promotes use of shared RAM for variables, which is bug prone

- What C code would result in this instruction?

static int16 B; // B is a variable that happens to be at address \$0038

T = T + B;

- "Indexed" operand memory indexed; pre/post increment/decrement

- ADDD oprx,xysp (D) + [EE:FF+XYSP] => D

- Add oprx to X, Y, SP or PC; use address to fetch from memory; add value into D

- Encoding: E3 xb // E3 xb ff // E3 xb ee ff

(Signed offset value; encoding varies 5 bits, 9 bits; 16 bits)

- Example: ADDD \$FFF0, X add value at (X-16<sub>10</sub>) to D

Encoding: E3 10 (5 bit signed constant ... "\$10")

(see Table 1 of CPU12 reference guide for xb byte encoding)

- Special optimized mode for smaller code size and faster execution

- "xb" can do many tricks, including support for post/pre-increment/decrement to access arrays

- What C code would result in this instruction?

static int16 B[100];

register int16 \*p = &B[50]; // assume "p" is stored in register X

T = T + \*(p-8); // adds B[42] to T

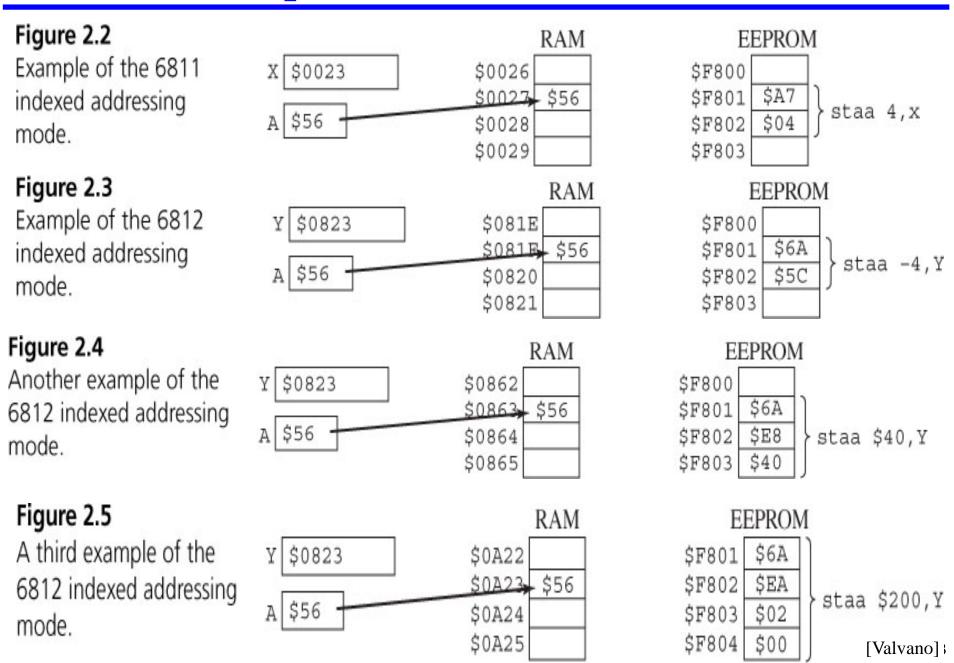

### **Indexed Examples**

- "Indexed Indirect" operand use memory value as address, with offset

- ADDD [oprx16,xysp]

$$(D) + [[EE:FF+XYSP]] \Rightarrow D$$

Add oprx to X, Y, SP or PC; use address to fetch from memory; use the value fetched from memory to fetch from a different memory location; add value into D

- Encoding: E3 xb ee ff

Example: ADDD [\$8, X] add value at [(X+8)] to D

Encoding: E3 E3 00 08 16-bit constant offset

(see Table 1 of CPU12 reference guide for xb byte encoding)

• What C code would result in this instruction?

```

static int16 vart;

register int16 *p;

static int16 *B[100]; // B is a variable that happens to be at address $38

```

```

B[4] = \&vart;

p = \&B[0]; // assume "p" is stored in register X

T = T + *(*(p+4)); // adds vart to T

```

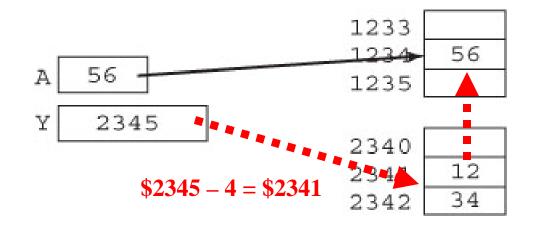

### **Indexed Indirect Example**

**LDAA #\$56**

LDY #\$2345

STAA [-4,Y]; Fetch 16-bit address from \$2341, store A at \$1234

### Figure 2.6

Example of the 6812 indexed-indirect addressing mode.

[Valvano]

# **Had Enough Yet?**

- Really, all these modes get used in real programs

- You've already seen very similar stuff in 18-240, but that's more RISC-like

- We expect you to be able to tell us what a short, simple program we've written does if it uses any of the modes described during lecture

- There are even trickier modes seldom used but nice to have

- See Valvano Section 2.2 for more discussion

### Other Math & Load/Store Instructions

#### Math

- ADD integer addition (2's complement)

- SBD integer subtraction (2's complement)

- CMP compare (do a subtraction to set flags but don't store result)

### Logic

- AND logical bit-wise and

- ORA logical bit-wise or

- EOR bit-wise exclusive or (xor)

- ASL, ASR arithmetic shift left and right (shift right sign-extends)

- LSR logical shift right

#### Data movement

- LDA, LDX, ... load from memory to a register

- STA, STX, ... store from register to memory

- MOV memory to memory movement

### Bit operations and other instructions

• Later...

### **Control Flow Instructions**

### Used to go somewhere other than the next sequential instruction

- Unconditional branch always changes flow ("goto instruction x")

- Conditional branch change flow sometimes, depending on some condition

#### Addressing modes

- REL: Relative to PC "go forward or backward N bytes"

- Uses an 8-bit offset rr for the branch target

- Most branches are short, so only need a few bits for the offset

- Works the same even if segment of code is moved in memory

- EXT: Extended hh:ll "go to 16-bit address hh:ll"

- Takes more bits to specify

- No limit on how far away the branch can be

### **Relative Addressing**

#### Relative address computed as:

- Address of next in-line instruction <u>after</u> the branch instruction

- Because the PC already points to the next in-line instruction at execution time

- Plus relative byte rr treated as a *signed* value

- rr of 0..\$7F is a forward relative branch

- rr of \$80..\$FF is a backward relative branch

#### Example: BCC cy\_clr

- Next instruction is at \$0009; rr = \$03

- $\$0009 + \$03 = \$000C \text{ (cy\_clr)}$

\$0006 (asm\_loop)

#### asm\_main: 000000 180B 01xx MOVB #1, temp byte Example: BRA asm\_loop 000004 xx 000005 87 CLRA Next instruction is at \$000F; asm\_loop: 000006 INCB rr=\$F7 000007 2403 cy\_clr BCC \$000F + \$F7 =000009 43 DECA DECA 00000A 43 \$000F + \$FFF7 =00000B 43 DECA \$000F - \$0009 = cy\_clr: 00000C A7 NOP

00000D 20F7

BRA

asm\_loop

### **Unconditional Branch**

### JMP instruction – Jump

- JMP \$1256 -- jump to address \$1256 JMP Target\_Name

- JMP also supports indexed addressing modes why are they useful?

- BRA \$12 -- jump to \$12 past current instruction

- Relative addressing ("rr") to save a byte and make code relocatable

### **♦** JSR instruction – Jump to Subroutine

- JSR \$7614 -- jump to address \$7614, saving return address

- JSR Subr\_Name

- Supports DIRect (8 bit offset to page 0) and EXTended, as well as indexed addressing

- More about how this instruction works in the next lecture

### **Conditional Branch**

#### Branch on some condition

- Always with RELative (rr 8-bit offset) addressing

- Look at detailed instruction set description for specifics of exactly what address the offset is added to

- Condition determines instruction name

- BCC \$08 branch 8 bytes ahead if carry bit clear

- BCS Loop branch to label "Loop" if carry bit set

- BEQ / BNE branch based on Z bit ("Equal" after compare instruction)

- BMI / BPL branch based on N bit (sign bit)

### Other complex conditions that can be used after a CMP instruction

- BGT branch if greater than

- BLE branch if less than or equal

- •

### **Condition Codes**

### **♦** Status bits inside CPU that indicate results of operations

- C = carry-out bit

- Z = whether last result was zero

- N = whether last result was "negative" (highest bit set)

- V = whether last result resulted in an arithmetic overflow

#### Set by some (but not all instructions)

- CMP subtracts but doesn't store result; sets CC bits for later "BGE, BGT" etc

- ADD and most arithmetic operations sets CC bits

- MOV instructions generally do <u>NOT</u> set CC bits on this CPU

- − But, on a few other CPUs they do − so be careful of this!

### C & V flags

- Carry: did the previous operation result in a carry out bit?

- FFFF + 1 = \$0000 + Carry out

- \$7FFF + \$8000 = \$FFFF + No Carry out

- Carry-in bit, if set, adds 1 to sum for ADC

- we'll do multi-precision arithmetic later

- Carry bit is set if there is an *unsigned* add or subtract overflow

- Result is on other side of \$0000/\$FFFF boundary

- Overflow (V): did the previous operation result in a signed overflow?

- FFFF + 1 = \$0000 no signed overflow (-1 + 1 = 0)

- \$7FFF + 1 = \$8000 has signed overflow  $(32767 + 1 \rightarrow -32768)$

- This is overflow in the normal signed arithmetic sense that you are used to

- Result is on other side of \$8000/\$7FFF boundary

- ♦ Note that the idea of "overflow" depends on signed vs. unsigned

- Hardware itself is sign agnostic software has to keep track of data types

- Carry flag indicates unsigned overflow

- V flag indicates signed overflow

## **Look For Annotations Showing CC Bits Set**

Instruction Set Summary (Sheet 5 of 14)

|                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                     | . / \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation                                                                                                                                                                  | Addr.<br>Mode                                                                                                                                                                                                                                                                                                                                                          | Machine<br>Coding (hex)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Access Detail HCS12 HC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SXHI                                                                                                                                                                                                                                                                                                                                                                                                | N Z V d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (cntr) - 1 ⇒ cntr  If (cntr) not = 0, then Branch; else Continue to next instruction  Decrement Counter and Branch if ≠ 0 (cntr = A, B, D, X, Y, or SP)                    | REL<br>(9-bit)                                                                                                                                                                                                                                                                                                                                                         | 04 lb rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PPP (branch) PPO (no branch)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $(M) \cdot \$01 \Rightarrow M$ Decrement Memory Location $(A) \cdot \$01 \Rightarrow A \qquad \text{Decrement A}$ $(B) \cdot \$01 \Rightarrow B \qquad \text{Decrement B}$ | EXT<br>IDX<br>IDX1<br>IDX2<br>[D,IDX]<br>[IDX2]<br>INH<br>INH                                                                                                                                                                                                                                                                                                          | 73 hh 11<br>63 xb<br>63 xb ff<br>63 xb ee ff<br>63 xb<br>63 xb ee ff<br>43<br>53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rPw re rPw rPw rPw frpw fifrpw fifrpw fiprpw o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | w<br>w<br>w<br>w                                                                                                                                                                                                                                                                                                                                                                                    | ΔΔΔ-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (SP) - \$0001 ⇒ SP<br>Translates to LEAS -1,SP                                                                                                                             | IDX                                                                                                                                                                                                                                                                                                                                                                    | 1B 9F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pf PI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | p <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (X) - \$0001 ⇒ X<br>Decrement Index Register X                                                                                                                             | INH                                                                                                                                                                                                                                                                                                                                                                    | 09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                   | Δ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (Y) -\$0001 ⇒ Y<br>Decrement Index Register Y                                                                                                                              | INH                                                                                                                                                                                                                                                                                                                                                                    | 03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                   | Δ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                            | (cntr) - 1 ⇒ cntr  If (cntr) not = 0, then Branch; else Continue to next instruction  Decrement Counter and Branch if ≠ 0 (cntr = A, B, D, X, Y, or SP)  (M) - \$01 ⇒ M  Decrement Memory Location  (A) - \$01 ⇒ A Decrement A (B) - \$01 ⇒ B Decrement B  (SP) - \$0001 ⇒ SP  Translates to LEAS -1,SP  (X) - \$0001 ⇒ X  Decrement Index Register X (Y) - \$0001 ⇒ Y | Operation       Mode         (cntr) - 1 ⇒ cntr       REL         If (cntr) not = 0, then Branch;<br>else Continue to next instruction       (9-bit)         Decrement Counter and Branch if ≠ 0<br>(cntr = A, B, D, X, Y, or SP)       EXT         (M) - \$01 ⇒ M       EXT         Decrement Memory Location       IDX         IDX1<br>IDX2<br>[IDX2]       IDX1<br>[IDX2]         (A) - \$01 ⇒ A       Decrement A       INH         (B) - \$01 ⇒ B       Decrement B       INH         (SP) - \$0001 ⇒ SP       IDX         Translates to LEAS -1,SP       INH         (X) - \$0001 ⇒ X       INH         Decrement Index Register X       INH | Coperation       Mode       Coding (hex)         (cntr) - 1 ⇒ cntr<br>If (cntr) not = 0, then Branch;<br>else Continue to next instruction       REL<br>(9-bit)       04 1b rr         Decrement Counter and Branch if ≠ 0<br>(cntr = A, B, D, X, Y, or SP)       EXT<br>(Duby 100 multiple of the continue | Operation       Mode       Coding (hex)       HCS12       HC1         (cntr) - 1 ⇒ cntr       REL If (cntr) not = 0, then Branch; else Continue to next instruction       (9-bit)       04 1b rr       PPP (branch) PPP (no branch)       PPP (no branch)         Decrement Counter and Branch if ≠ 0 (cntr = A, B, D, X, Y, or SP)       EXT 73 hh 11 rPwO rPW | Operation         Mode         Coding (hex)         HCS12         HC12         SX H I           (cntr) - 1 ⇒ cntr<br>If (cntr) not = 0, then Branch;<br>else Continue to next instruction         REL<br>(9-bit)         04 lb rr         PPP (branch)<br>PPO (no branch)         PPP           Decrement Counter and Branch if ≠ 0<br>(cntr = A, B, D, X, Y, or SP)         EXT 73 lh ll 1<br>IDX 63 xb rpw rpw<br>IDX1 63 xb ff rpw0 rpw<br>IDX2 63 xb ee ff frewP frepw<br>IDX2 63 xb ee ff frepw frepw<br>IDX3 be eff frepw frepw<br>IDX4 be so o o         TPWO rpw           (A) -\$01 ⇒ A Decrement A (B) -\$01 ⇒ B Decrement B         INH 43 o o o         O o           (SP) -\$0001 ⇒ SP Translates to LEAS -1,SP         IDX 1B 9F         Pf         Pp1           (X) -\$0001 ⇒ X Decrement Index Register X         INH 09         O o o         O           (Y) -\$0001 ⇒ Y         INH 03         O o o         O |

### **Assembler to Hex**

Sometimes (less often these days, but sometimes) you have to write your own assembler!

- **♦** In this course, we want you to do just a little by hand to get a feel

- LDAB #254

| LDAB #opr8i        | $(M) \Rightarrow B$ | IMM     | C6 ii       | P        | Р -   | <br>ΔΔ0- |

|--------------------|---------------------|---------|-------------|----------|-------|----------|

| LDAB opr8a         | Load Accumulator B  | DIR     | D6 dd       | rPf      | rfP   |          |

| LDAB opr16a        |                     | EXT     | F6 hh ll    | rPO      | rop   |          |

| LDAB oprx0_xysp    |                     | IDX     | E6 xb       | rPf      | rfP   |          |

| LDAB oprx9,xysp    |                     | IDX1    | E6 xb ff    | rPO      | rPO   |          |

| LDAB oprx16,xysp   |                     | IDX2    | E6 xb ee ff | frPP     | frPP  |          |

| LDAB [D,xysp]      |                     | [D,IDX] | E6 xb       | fIfrPf f | IfrfP |          |

| LDAB [oprx16,xysp] |                     | [IDX2]  | E6 xb ee ff | fIPrPf f | IPrfP |          |

- Addressing mode is:\_\_\_\_\_

- Opcode is:

- Operand is:

- Full encoding is:\_\_\_\_\_

### **Hex to Assembler (Dis-Assembly)**

- ♦ If all you have is an image of a program in memory, what does it do?

- Important for debugging

- Important for reverse engineering (competitive analysis; legacy components)

- Start with Hex, and figure out what instruction is

- AA E2 23 CC

| ORAA #opr8i        | $(A) + (M) \Rightarrow A$ | IMM     | 8A ii       | P      | P      |   | ΔΔ0-           |

|--------------------|---------------------------|---------|-------------|--------|--------|---|----------------|

| ORAA opr8a         | Logical OR A with Memory  | DIR     | 9A dd       | rPf    | rfP    | 1 | <b>       </b> |

| ORAA opr16a        |                           |         | BA hh 11    | rPO    | rop    | 1 |                |

| ORAA oprx0_xysp    |                           | IDX     | AA xb       | rPf    | rfP    | 1 |                |

| ORAA oprx9,xysp    |                           | IDX1    | AA xb ff    | rPO    | rPO    | 1 | 1 1            |

| ORAA oprx16,xysp   |                           | IDX2    | AA xb ee ff | frPP   | frPP   | 1 | 1              |

| ORAA [D,xysp]      |                           | [D,IDX] | AA xb       | fIfrPf | fIfrfP | 1 | 1              |

| ORAA [oprx16,xysp] |                           | [IDX2]  | AA xb ee ff | fIPrPf | fIPrfP |   |                |

ORAA – one of the indexed versions

[Motorola01]

• Need to look up XB value => \_\_\_\_\_

#### Table 1. Indexed Addressing Mode Postbyte Encoding (xb)

| 00       | 10       | 20      | 30       | 40       | 50       | 60      | 70       | 80       | 90       | A0      | B0       | CO       | D0       | E0        | F0        |

|----------|----------|---------|----------|----------|----------|---------|----------|----------|----------|---------|----------|----------|----------|-----------|-----------|

| 0,X      | -16,X    | 1,+X    | 1,X+     | 0,Y      | -16,Y    | 1,+Y    | 1,Y+     | 0,SP     | -16,SP   | 1,+SP   | 1,SP+    | 0,PC     | -16,PC   | n,X       | n,SP      |