#### **FET Amplifiers** $\frac{20}{1}v$ <u>20</u>v $6.6k\Omega$ $6.6k\Omega$ $V_{GS} = 5v$ $V_{GS} = 5v$ $V_{DS}$ 10 20 0 3 $V_{T0} = 1.0V$ $K_p = 2e-5 [A/V^2]$ W=100 microns $V_{GS}=5.0V$ L=10 microns 2 $I_{DS}\left( mA\right)$ $V_{GS}=4.0V$ $V_{GS}=3.0V$ $V_{GS}=2.0V$ $V_{GS}=1.0V$ 0

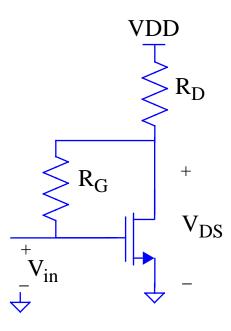

## **FET Amplifiers**

- A 200mv peak ac input voltage will cause more than a 1v peak ac output voltage

- What would we change to make the voltage gain even larger?

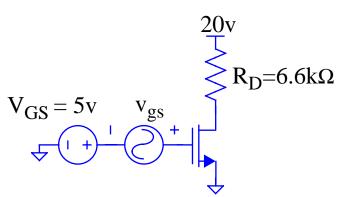

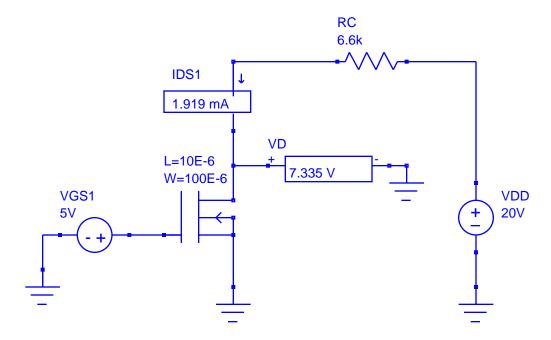

## dc Solution of FET Amplifier

- Set the ac source to zero and analyze the dc bias point

- Solution should agree with that from load line approximation

# dc Solution of FET Amplifier

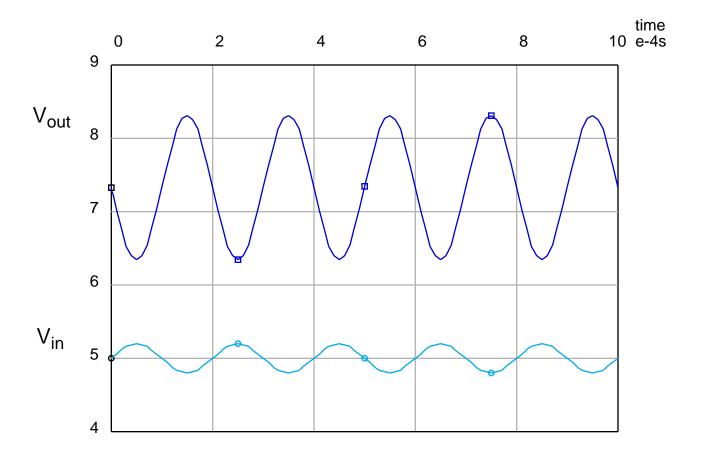

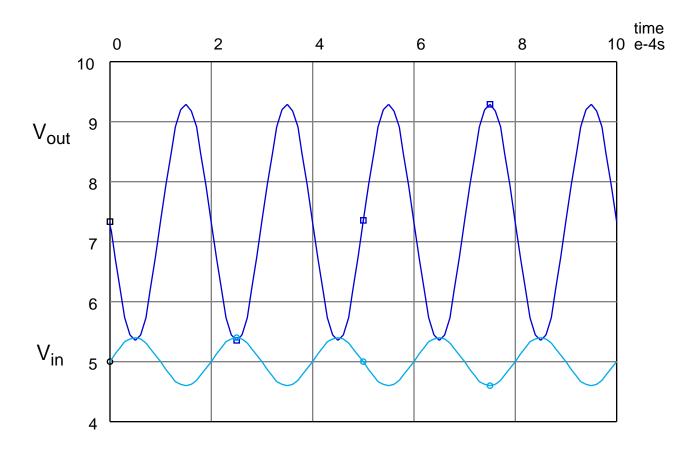

• Response for a 5kHz, 0.2v peak ac input signal

# dc Solution of FET Amplifier

• The output signal is somewhat distorted for a 0.4v peak ac input

## **Small Signal Assumption**

$\bullet$  The distortion is due to the nonlinear effects when the ac  $v_{gs}$  is too large:

bias point equations:

$$I_D = K(V_{GS} - V_t)^2$$

$V_D = V_{DD} - R_D I_D$

ac & dc equations:

$$v_{GS} = V_{GS} + v_{gS}$$

$i_D = K(v_{GS} - V_t)^2$

#### **Transconductance -- Gain**

• The transconductance, g<sub>m</sub>, for a MOSFET is much smaller than that for a BJT which uses the same silicon area (BJT approx. 100 times better)

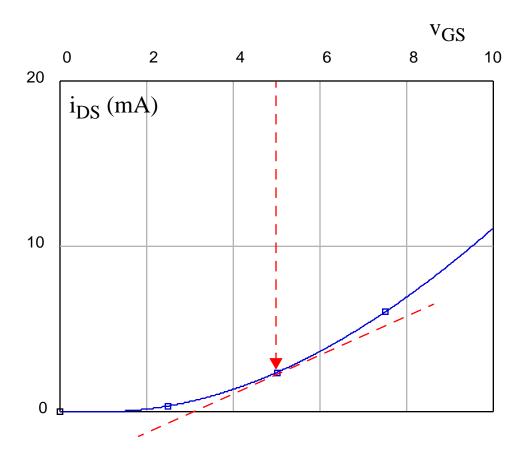

$$g_m = \frac{\partial i_D}{\partial v_{GS}} \bigg|_{v_{GS} = V_{GS}}$$

#### **Transconductance -- Gain**

- BJT g<sub>m</sub>'s are independent of area dimensions

- FET g<sub>m</sub>'s are dependent on channel W and L dimensions

$$g_m = \frac{\partial i_D}{\partial v_{GS}}\bigg|_{v_{GS} = V_{GS}} = 2K(V_{GS} - V_t) = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_t)$$

## **Small Signal Voltage Gain**

$$v_D = V_{DD} - R_D i_D = V_{DD} - R_D (I_D + i_d)$$

• Under the small signal assumption:

$$v_d = -R_D i_d = -g_m R_D v_{gs}$$

$$\frac{v_d}{v_{gs}} = -g_m R_D$$

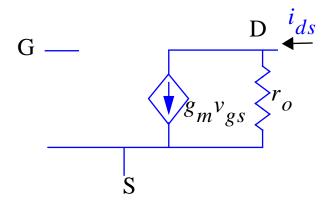

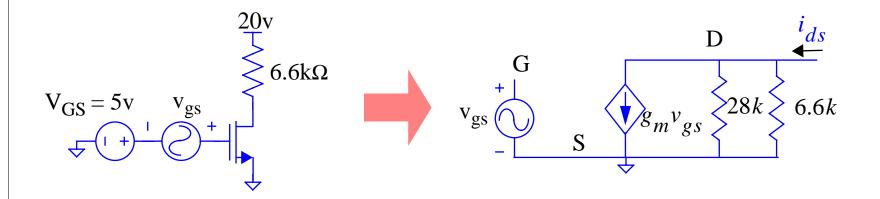

## **Small Signal Model**

• The small signal model is very similar to that for the BJT amplifier:

• r<sub>o</sub> is the drain-source voltage change with change in i<sub>ds</sub> due to channel length modulation.

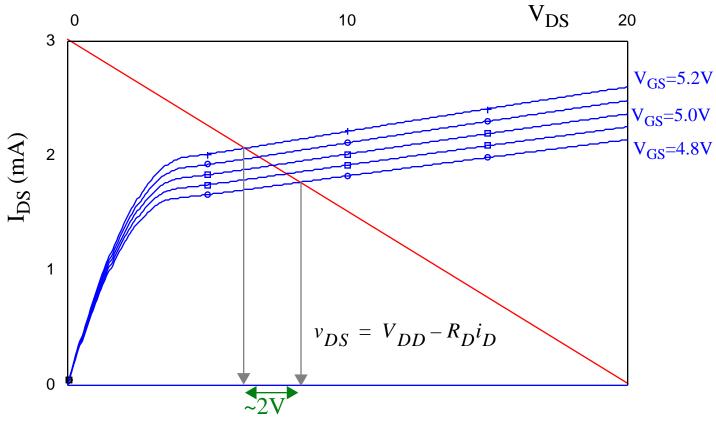

## **Channel Length Modulation**

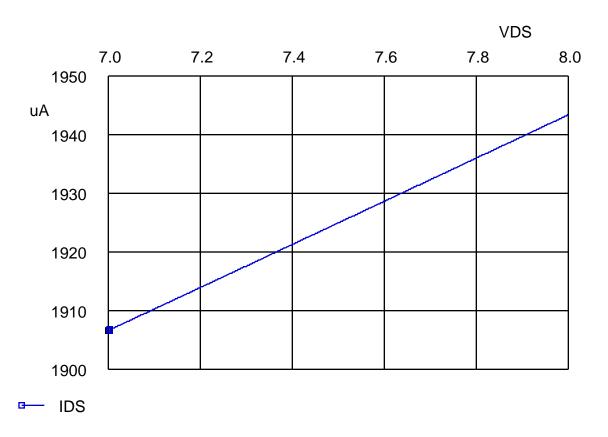

- Given lambda and the bias point, we can calculate r<sub>o</sub>

- For our example, we can estimate  $r_o$  from an enlarged view of  $I_{DS}$  vs.  $V_{DS}$  at the bias point (with  $V_{GS}$ =5v)

## **Small Signal Model**

• Short the dc supplies and analyze the small signal equivalent ckt:

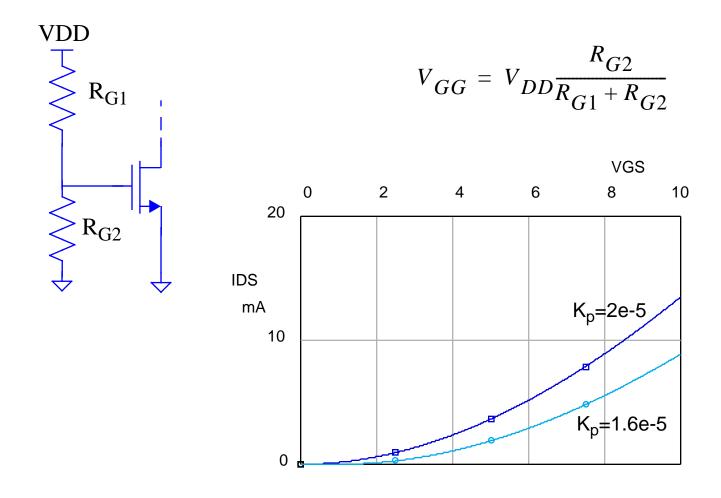

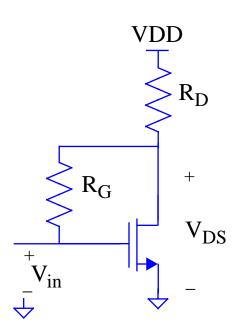

## **Biasing**

• Since  $I_D$  determines  $g_m$  we'd like to bias the transistor so that the small signal gain remains as stable as possible with variations in temperature and process

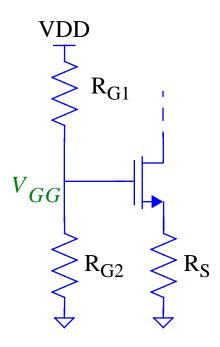

## **Negative Feedback Resistor**

ullet R<sub>S</sub> provides negative feedback for unwanted changes in I<sub>DS</sub> due to process variations or temperature fluctuations

#### **Negative Feedback Resistor**

- We can get a similar negative feedback effect with a drain to gate bias resistor

- This resistor guarantees that the transistor is biased in the saturation region -- why?

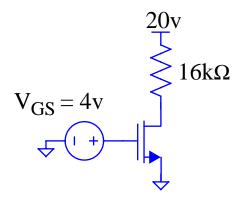

Find the R<sub>D</sub> which establishes a 1mA I<sub>D</sub>

$$K=0.25 \text{mA/V}^2$$

$VDD=20V$   $V_t=2V$

## **No negative Feedback Resistor**

• What is the change in  $I_D$  for the circuit below if the threshold voltage changes from 2V to 3V?

# **Negative Feedback Resistor**

• But this change is much less with negative feedback control