# Where Are We Now?

# Where we've been:

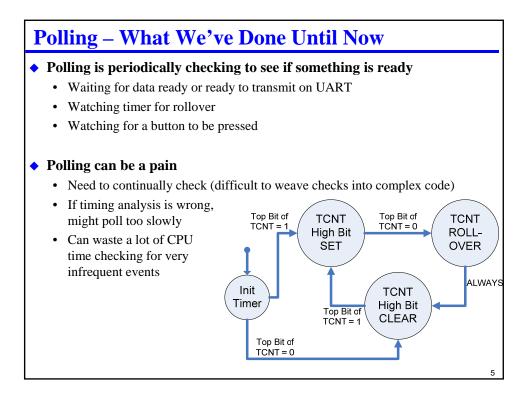

- Time and counters a bit more nitty-gritty

- Keeping track of timer rollovers was painful, wasn't it?

- Better approach use interrupts!

# Where we're going today:

• Interrupts

### Where we're going next:

- Concurrency, scheduling

- Analog and other I/O

- Test #2

# **Preview**

- Really "getting" interrupts is an essential embedded system skill

- If I had to pick one job interview question to ask, this would be the topic

#### Hardware interrupts

• Asynchronous, hardware-triggered cousin to SWI

### • What happens in a HW interrupt?

- Trigger interrupt

- Save state

- Execute an Interrupt Service Routine

- Acknowledge the interrupt (so it doesn't retrigger)

- Resume execution of main program

#### Timer example

- Real time clock from last lecture but done with interrupts

- Complete example in both assembler and C

#### SWI as a system call

# **Interrupts To The Rescue**

# • Big idea:

Wouldn't it be nice to be notified when something happens (interrupted) instead of having to check continually (polling)?

## In daily life:

- Wristwatch:

- Polling is checking watch every 5 minutes to see if class is over yet

- Interrupt is having an alarm ring at end of class

### • Cell phone:

- Polling is checking your phone to see if text message icon is displayed

- Interrupt is having an audible alarm (or vibration) if text message is received

- Making tea:

- Polling is checking the kettle every minute to see if it is boiling

- Interrupt is having a the tea kettle whistle

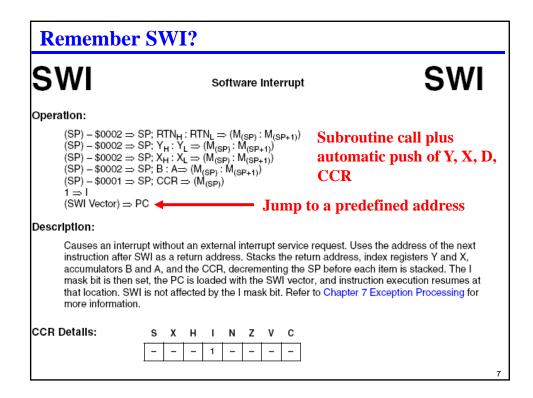

| SWI Is A "Software Interrupt"                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Sort of like a subroutine call (JSR), but with some differences</li> </ul>                                                                                           |

| <ul> <li>Interrupts flow of program control</li> </ul>                                                                                                                        |

| • Jumps to a location specified by a "vector" instead of an address in the instruction                                                                                        |

| <ul> <li>That makes it an Inherent operand ("INH") – the address is <u>not</u> in the instruction</li> <li>We'll get back to the idea of a vector shortly</li> </ul>          |

| • Always the same address for any SWI invocation, regardless of how many                                                                                                      |

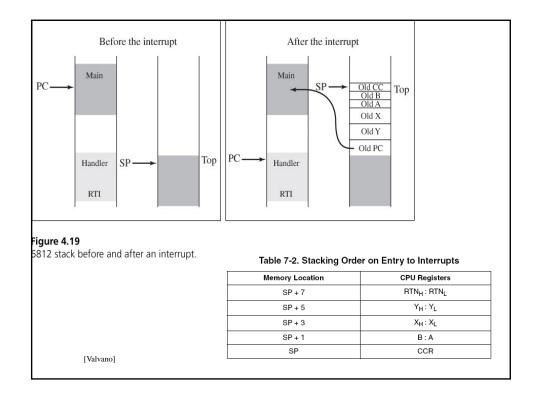

| Saves state                                                                                                                                                                   |

| • Pushes the programmer visible register state on the stack                                                                                                                   |

| Including the condition code register                                                                                                                                         |

| • As long as SWI-processing routine doesn't mess with stack or memory, return<br>from SWI leaves CPU in exactly the same state as before the SWI<br>(see the RTI instruction) |

| RTI is like RTS                                                                                                                                                               |

| • BUT with differences to corresponding to SWI placement of stack items                                                                                                       |

|                                                                                                                                                                               |

| RTI                                                                                                                                                           |                                                                                                                                                                                                                    | Return fro                                                           | om Interrup                  | t                    | RTI                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------|----------------------|-----------------------------------------------------------------------------|

| Operation:                                                                                                                                                    |                                                                                                                                                                                                                    |                                                                      |                              |                      |                                                                             |

| $\begin{array}{l} (M_{(SP)}) \Rightarrow CCF \\ (M_{(SP)}: M_{(SP+1)} \\ (M_{(SP)}: M_{(SP+1)} \\ (M_{(SP)}: M_{(SP+1)} \\ (M_{(SP)}: M_{(SP+1)} \end{array}$ | $\begin{array}{l} (SP) + \$0001 \Rightarrow \\ ) \Rightarrow B : A; (SP) + \\ ) \Rightarrow X_H : X_L; (SP) + \\ ) \Rightarrow PC_H : PC_L; (SP) + PC_H : PC_L; (SP) \\ ) \Rightarrow Y_H : Y_L; (SP) \end{array}$ | > SP<br>- \$0002 ⇒ \$<br>) + \$0004 =<br>SP) - \$000<br>) + \$0004 = | SP<br>⇒ SP<br>2 ⇒ SP<br>⇒ SP |                      |                                                                             |

| Description:                                                                                                                                                  |                                                                                                                                                                                                                    |                                                                      |                              |                      |                                                                             |

| accumulators E<br>from the stack.                                                                                                                             | and A, index regi                                                                                                                                                                                                  | ister X, the l<br>ay be clear                                        | PC, and inde<br>ed as a resu | x register Y are res | he condition codes,<br>stored to a state pulled<br>ion, but cannot be set   |

| adjusted to pre                                                                                                                                               | serve stack conte                                                                                                                                                                                                  | ent, and the                                                         | new vector                   | s fetched. This ope  | m the stack, the SP is<br>eration is functionally<br>are re-stacked, but is |

| CCR Details:                                                                                                                                                  | sхн                                                                                                                                                                                                                | INZ                                                                  | v c                          |                      |                                                                             |

|                                                                                                                                                               | $\Delta  \Downarrow  \Delta$                                                                                                                                                                                       | ΔΔΔ                                                                  | ΔΔ                           |                      |                                                                             |

| • Inverse oper                                                                                                                                                | ation of SW                                                                                                                                                                                                        | /I – puts                                                            | s everytł                    | ning back on         | the stack                                                                   |

# What Do We Need Beyond An SWI?

#### Want to generate an interrupt based on when, not where

- SWI has to be placed as an explicit instruction at a specific location ... a synchronous interrupt happens synchronized to program flow

- What we want are interrupts that occur without an actual instruction... <u>asynchronous interrupt</u> – happens without regard to program flow

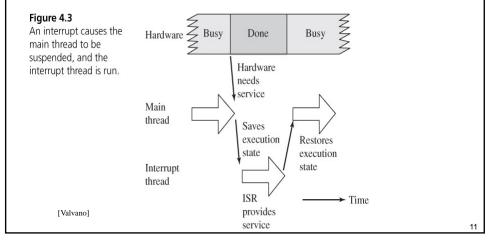

# **Simplified Execution Of A Hardware Interrupt**

(More concrete example with details coming soon...)

#### Some piece of hardware generates an interrupt

- Not an SWI instruction happens asynchronously with and independent from the program execution

- So this means it can happen <u>any time</u> (with exceptions we'll get to soon)

- You can think of this as hardware shoving an SWI into the instruction fetch queue ... even though the SWI wasn't actually in memory

#### • CPU executes an interrupt handling process

- That interrupt causes CPU to execute a virtual interrupt opcode (same effects of SWI, but without that instruction coming from memory)

- CPU jumps to a particular handling routine via a vector

#### Interrupt handling software executes

- An Interrupt Sub-Routine (ISR) executes (subroutine to handle the interrupt)

- When completed, the ISR executes an RTI instruction

This is a real RTI instruction, just like we saw with SWI

- This is a real KTT instruction, just like we saw with S

### Normal program resumes operation

• CPU registers unchanged – program has no idea it was interrupted

# What Can Generate An Interrupt?

# • General categories on any CPU – each has a different vector location

- Interrupt jumps to address at vector (e.g., SWI jumps to [\$FFF6])

- Various types of resets

- Various types of illegal situations (e.g., undefined opcode executed)

- Hardware signals from devices

| • SWI | Tab            | Table 7-1. CPU12 Exception Vector Map       |  |  |

|-------|----------------|---------------------------------------------|--|--|

|       | Vector Address | Source                                      |  |  |

|       | \$FFFE-\$FFFF  | System Reset                                |  |  |

|       | \$FFFC-\$FFFD  | Clock Monitor Reset                         |  |  |

|       | \$FFFA-\$FFFB  | COP Reset                                   |  |  |

|       | \$FFF8-\$FFF9  | Unimplemented Opcode Trap                   |  |  |

|       | \$FFF6-\$FFF7  | Software Interrupt Instruction (SWI)        |  |  |

|       | \$FFF4-\$FFF5  | XIRQ Signal                                 |  |  |

|       | \$FFF2-\$FFF3  | IRQ Signal                                  |  |  |

|       | \$FF00-\$FFF1  | Device-Specific Interrupt Sources (HCS12)   |  |  |

|       | \$FFC0-\$FFF1  | Device-Specific Interrupt Sources (M68HC12) |  |  |

|       |                | ······                                      |  |  |

|       | 0xFFDE, 0xFFDF | Standard timer overflow I bit TMSK2 (TOI)   |  |  |

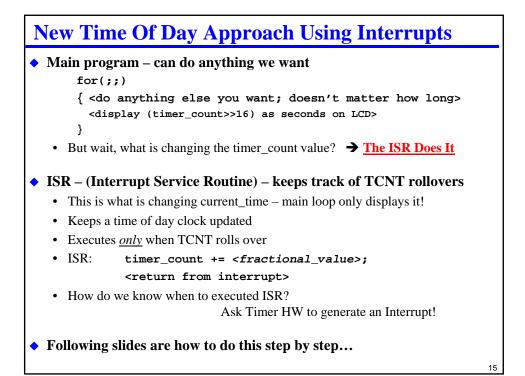

# **More Specific Example – Time Of Day**

# • Remember the time of day example? (statechart in an earlier slide)

- Needed to tightly loop monitoring the TCNT value, watching for zero crossing

- Better way use an interrupt

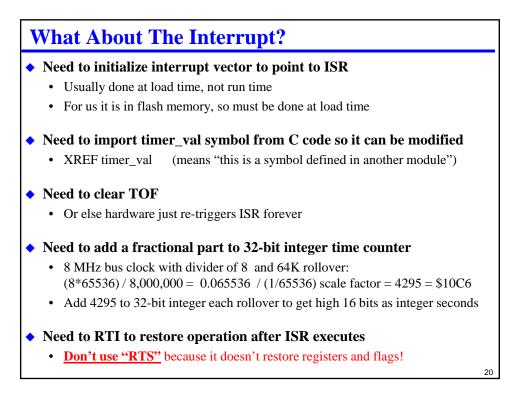

### • Recap of program at a high level:

- TCNT is the current timer value; assume bus clock divided by 8

- Current\_time is a uint32

- Add <*fractional\_value*> to 32-bit value every TCNT rollover

- High 16 bits are current time in seconds

### • Algorithm for the old approach (polled version):

```

for(;;)

{ <wait for TCNT roll-over (TCNT changes from $FFFF to $0000)>

timer_count += <fraction_value>;

<display (timer_count>>16) as seconds on LCD>

}

```

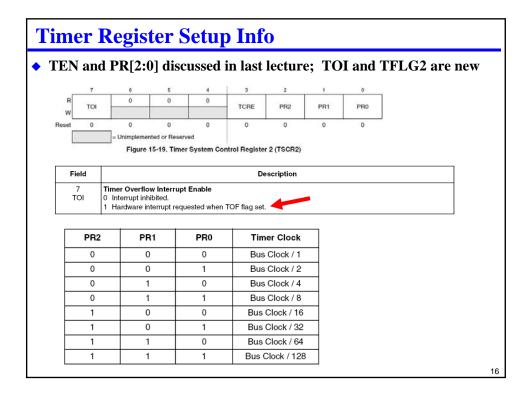

| Timer Register Setup                                                               |   |

|------------------------------------------------------------------------------------|---|

| <ul> <li>TEN – Timer enable</li> <li>Bit 7 of TSCR1 set to enable timer</li> </ul> |   |

| TSCR1  = 0x80;                                                                     |   |

| ♦ PR[2:0] – Timer prescale                                                         |   |

| • Bits 20 of TSCR2 set prescale – set to bus clock / 8                             |   |

| • From last lecture, TCNT rollover every 0.167772 seconds                          |   |

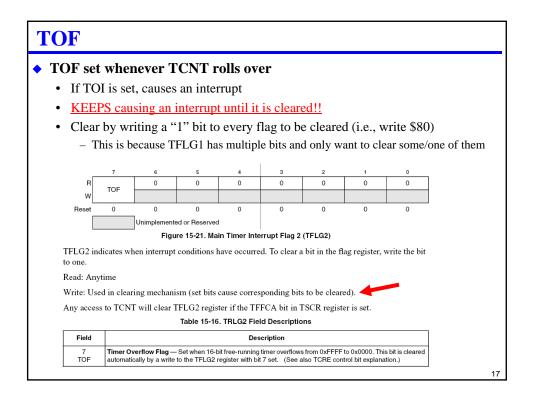

| ◆ TOI                                                                              |   |

| • Bit 7 of TSCR2 set to one – generates interrupt every time TCNT rolls            |   |

| <ul> <li>TCNT rollover is caught by the TOF – Timer Overflow Flag</li> </ul>       |   |

| <pre>// TSCR2[2:0] binary 011=bus clock/8</pre>                                    |   |

| // TSCR2[7] TOI set to interrupt on TOF (TCNT rollover)                            |   |

| TSCR2 = (TSCR2 & 0x78)   0x03   0x80;                                              |   |

|                                                                                    |   |

| 1                                                                                  | 8 |

# **Timer Main Program**

```

volatile uint32 timer_val=0;

void main(void)

{

// set TN = 1 Timer Enable TSCR1 bit 7

TSCR1 |= 0x80;

// TSCR2[2:0] binary 011=bus clock/8

// TSCR2[7] TOI set to interrupt on TOF (TCNT rollover)

TSCR2 = (TSCR2&0x78)|0x03|0x80;

EnableInterrupts;

for(;;)

{ // code goes here to copy (timer_val>>16) to display

} /* loop forever */

}

```

```

XREF timer_val

; import symbol from C code

MyCode:

SECTION

count_isr:

; this is the ISR routine

LDAA #$80 ; Clear TOF; top bit in TFLG2

STAA TFLG2 ; This acknowledges the rollover intrpt

; 32-bit add $10C6 to increment fractional second

LDAA timer_val+3

; byte-wise 32-bit add

ADDA #$C6

STAA timer_val+3

LDAA timer_val+2

ADCA #$10

STAA timer_val+2

LDAA timer_val+1

ADCA #$00

STAA timer_val+1

LDAA timer_val

; why isn't this a loop here?

ADCA #$00

; (what if infinite loop here?)

STAA timer_val

RTI

; return to interrupted program

ORG $FFDE

; set interrupt vector for timer

DC.W count_isr

```

| Hardware Interrupt Recap                                                          |

|-----------------------------------------------------------------------------------|

| <ul> <li>Some piece of hardware generates an interrupt</li> </ul>                 |

| Happens asynchronously with and independent from the program execution            |

| • So this means it can happen <u>any time</u> (with exceptions we'll get to soon) |

| <ul> <li>CPU executes an interrupt handling process</li> </ul>                    |

| • That interrupt causes CPU to execute a virtual interrupt instruction            |

| - Happens between instructions, but anywhere in program                           |

| • CPU jumps to a particular handling routine via a vector                         |

| – Something has to set that vector to point to the ISR!                           |

| <ul> <li>Interrupt handling software executes</li> </ul>                          |

| • An Interrupt Sub-Routine (ISR) executes (subroutine to handle the interrupt)    |

| <ul> <li>Hardware saves registers</li> </ul>                                      |

| • When completed, the ISR executes an RTI instruction                             |

| <ul> <li>RTI restores the registers</li> </ul>                                    |

| <ul> <li>Normal program resumes operation</li> </ul>                              |

| • CPU registers unchanged – program has no idea it was interrupted                |

|                                                                                   |

| 22                                                                                |

| You can handle inter                                                                                                     | rupts in C/C++ as we                                                                                             | ell!                                                                         |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Syntax:                                                                                                                  |                                                                                                                  |                                                                              |

| void interrupt <                                                                                                         | <n> <fn>(void)</fn></n>                                                                                          |                                                                              |

| { }                                                                                                                      |                                                                                                                  | upt 0 ResetFunction(void)<br>mandler */                                      |

| • "2" is second entry,                                                                                                   | <b>nber in the interrupt</b><br>etc it's the entry num<br>mbers count <i>opposite</i> to a                       | ber, not byte address                                                        |

| • "2" is second entry,                                                                                                   | -                                                                                                                | ber, not byte address                                                        |

| <ul><li>"2" is second entry,</li><li>Be careful, these nur</li></ul>                                                     | etc it's the entry num<br>mbers count <i>opposite</i> to a                                                       | ber, not byte address<br>address direction!                                  |

| <ul> <li>"2" is second entry,</li> <li>Be careful, these nur</li> </ul> Vector Number                                    | etc it's the entry num<br>mbers count <i>opposite</i> to a<br>Vector Address                                     | ber, not byte address<br>address direction!<br>Vector Address Size           |

| <ul> <li>"2" is second entry,</li> <li>Be careful, these nur</li> </ul> Vector Number                                    | etc it's the entry num<br>mbers count <i>opposite</i> to a<br>Vector Address<br>0xFFFE, 0xFFFF                   | ber, not byte address<br>address direction!<br>Vector Address Size<br>2      |

| <ul> <li>"2" is second entry, .</li> <li>Be careful, these nur</li> </ul> Vector Number <ul> <li>0</li> <li>1</li> </ul> | etc it's the entry num<br>mbers count <i>opposite</i> to a<br>Vector Address<br>0xFFFE, 0xFFFF<br>0xFFFC, 0xFFFD | ber, not byte address<br>address direction!<br>Vector Address Size<br>2<br>2 |

# Same Timer Example, In C

```

extern volatile unsigned long timer_val = 0;

void main(void)

{ // set TEN = 1 Timer Enable TSCR1 bit 7

TSCR1 = TSCR1 | 0x80;

// TSCR2[2:0] binary 0=bus clock/8

// TSCR2[7] TOI set to interrupt on TOF (TCNT rollover)

TSCR2 = (TSCR2 \& 0x78) | 0x03 | 0x80;

EnableInterrupts;

for(;;) {

// code goes here to copy (timer_val>>16) to display

} /* loop forever */

}

void interrupt 16 timer_handler(void) //-(16*2)-2 = $FFDE for TOI

\{ TFLG2 = 0x80; \}

timer_val += 0x10C6;

25

```

| 128 interrupt                      |                | Table 1-9. Interrupt Ve                                                                                          | ector Loc   | ations            |

|------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------|-------------|-------------------|

| vectors                            | Vector Address | Interrupt Source                                                                                                 | CCR<br>Mask | Local Enable      |

| supported by course MCU            | 0xFFFE, 0xFFFF | External reset, power on reset,<br>or low voltage reset<br>(see CRG flags register to determine<br>reset source) | None        | None              |

| <ul> <li>Most or all of</li> </ul> | 0xFFFC, 0xFFFD | Clock monitor fail reset                                                                                         | None        | COPCTL (CME, FCME |

| them can be                        | 0xFFFA, 0xFFFB | COP failure reset                                                                                                | None        | COP rate select   |

| used in the                        | 0xFFF8, 0xFFF9 | Unimplemented instruction trap                                                                                   | None        | None              |

| same program!                      | 0xFFF6, 0xFFF7 | SWI                                                                                                              | None        | None              |

| 1 0                                | 0xFFF4, 0xFFF5 | XIRQ                                                                                                             | X-Bit       | None              |

| <ul> <li>Each vector</li> </ul>    | 0xFFF2, 0xFFF3 | IRQ                                                                                                              | I bit       | INTCR (IRQEN)     |

| gets its own                       | 0xFFF0, 0xFFF1 | Real time Interrupt                                                                                              | I bit       | CRGINT (RTIE)     |

| ISR                                | 0xFFEE, 0xFFEF | Standard timer channel 0                                                                                         | I bit       | TIE (COI)         |

| Higher vectors                     | 0xFFEC, 0xFFED | Standard timer channel 1                                                                                         | I bit       | TIE (C1I)         |

| •                                  | 0xFFEA, 0xFFEB | Standard timer channel 2                                                                                         | I bit       | TIE (C2I)         |

| get higher                         | 0xFFE8, 0xFFE9 | Standard timer channel 3                                                                                         | I bit       | TIE (C3I)         |

| priority (pick                     | 0xFFE6, 0xFFE7 | Standard timer channel 4                                                                                         | I bit       | TIE (C4I)         |

| one with                           | 0xFFE4, 0xFFE5 | Standard timer channel 5                                                                                         | Ibit        | TIE (C5I)         |

| highest address                    | 0xFFE2, 0xFFE3 | Standard timer channel 6                                                                                         | I bit       | TIE (C6I)         |

| to service next)                   | 0xFFE0, 0xFFE1 | Standard timer channel 7                                                                                         | I bit       | TIE (C7I)         |

|                                    | 0xFFDE, 0xFFDF | Standard timer overflow                                                                                          | l bit       | TMSK2 (TOI)       |

| -                                  | 0xFFDC, 0xFFDD | Pulse accumulator A overflow                                                                                     | I bit       | PACTL (PAOVI)     |

| Vector Address   | Interrupt Source             | CCR<br>Mask | Local Enable                     |  |  |

|------------------|------------------------------|-------------|----------------------------------|--|--|

| 0xFFDA, 0xFFDB   | Pulse accumulator input edge | I bit       | PACTL (PAI)                      |  |  |

| 0xFFD8, 0xFFD9   | SPI                          |             | SPICR1 (SPIE, SPTIE)             |  |  |

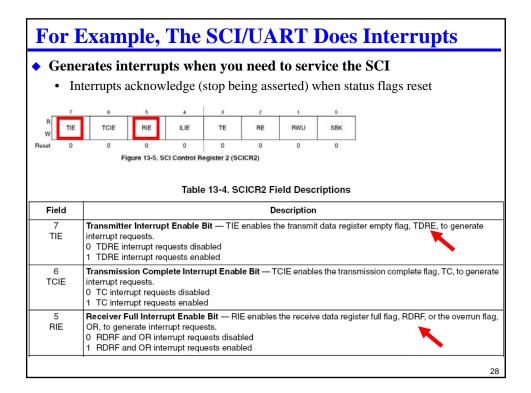

| 0xFFD6, 0xFFD7   | SCI                          | l bit       | SCICR2<br>(TIE, TCIE, RIE, ILIE) |  |  |

| 0xFFD4, 0xFFD5   | Reserved                     |             |                                  |  |  |

| 0xFFD2, 0xFFD3   | ATD                          |             | ATDCTL2 (ASCIE)                  |  |  |

| 0xFFD0, 0xFFD1   | Reserved                     |             |                                  |  |  |

| 0xFFCE, 0xFFCF   | Port J                       | I bit       | PIEP (PIEP7-6)                   |  |  |

| 0xFFCC, 0xFFCD   | Reserved                     |             |                                  |  |  |

| 0xFFCA, 0xFFCB   |                              | Reser       | ved                              |  |  |

| 0xFFC8, 0xFFC9   |                              | Reser       | ved                              |  |  |

| 0xFFC6, 0xFFC7   | CRG PLL lock                 |             | PLLCR (LOCKIE)                   |  |  |

| 0xFFC4, 0xFFC5   | CRG self clock mode          |             | PLLCR (SCMIE)                    |  |  |

| 0xFFBA to 0xFFC3 | Reserved                     |             |                                  |  |  |

| 0xFFB8, 0xFFB9   | FLASH                        | I bit       | FCNFG (CCIE, CBEIE)              |  |  |

| 0xFFB6, 0xFFB7   | CAN wake-up <sup>(1)</sup>   | I bit       | CANRIER (WUPIE)                  |  |  |

| 0xFFB4, 0xFFB5   | CAN errors <sup>1</sup>      | I bit       | CANRIER (CSCIE, OVRIE)           |  |  |

| 0xFFB2, 0xFFB3   | CAN receive <sup>1</sup>     | I bit       | CANRIER (RXFIE)                  |  |  |

| 0xFFB0, 0xFFB1   | CAN transmit <sup>1</sup>    | I bit       | CANTIER (TXEIE[2:0])             |  |  |

| 0xFF90 to 0xFFAF | Reserved                     |             |                                  |  |  |

| 0xFF8E, 0xFF8F   | Port P                       | I bit       | PIEP (PIEP7-0)                   |  |  |

| 0xFF8C, 0xFF8D   | PWM Emergency Shutdown       | I bit       | PWMSDN(PWMIE)                    |  |  |

| 0xFF8A, 0xFF8B   | VREG LVI                     | I bit       | CTRL0 (LVIE)                     |  |  |

| 0xFF80 to 0xFF89 | Reserved                     |             |                                  |  |  |

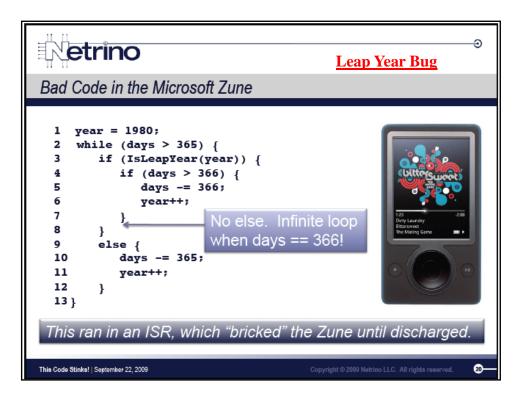

# **Some Notes On Saving State**

## Many processors don't automatically save state!

- For example, a RISC with 32 registers usually doesn't save them

- It is the ISR's responsibility to save things it changes, then restore them

#### In most systems, the flags are automatically saved

- Interrupt can happen after any instruction so need to save the flags

- What if you get an interrupt partway through a multi-precision add?

- What if you get an interrupt between a TST and BEQ?

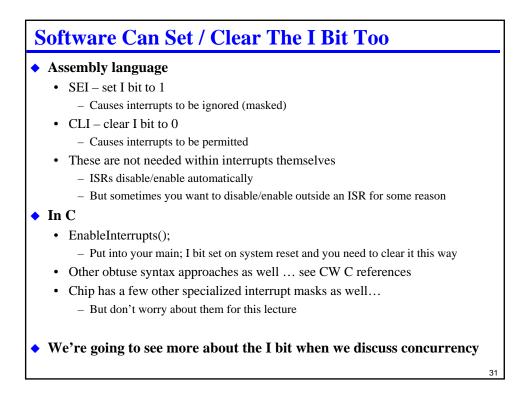

### Tricky part – what's up with the "I" bit?

- Part of the flag bits

- ... see next slide ...

# **Interrupt Masking**

- When we're in the ISR, what prevents TOF from interrupting us again?

- Interrupt processing saves the flag registers, including old I bit

- The I bit gets set by hardware while the ISR vector is fetched, masking interrupts (causes interrupts to be **Ignored**)

- No futher interrupts will be recognized in the ISR

- I bit gets restored as part of the RTI re-enabling interrupts

#### 2.2.5.4 | Mask Bit

The I bit enables and disables maskable interrupt sources. By default, the I bit is set to 1 during reset. An instruction must clear the I bit to enable maskable interrupts. While the I bit is set, maskable interrupts can become pending and are remembered, but operation continues uninterrupted until the I bit is cleared.

When an interrupt occurs after interrupts are enabled, the I bit is automatically set to prevent other maskable interrupts during the interrupt service routine. The I bit is set after the registers are stacked, but before the first instruction in the interrupt service routine is executed.

Normally, an RTI instruction at the end of the interrupt service routine restores register values that were present before the interrupt occurred. Since the CCR is stacked before the I bit is set, the RTI normally clears the I bit, and thus re-enables interrupts. Interrupts can be re-enabled by clearing the I bit within the service routine, but implementing a nested interrupt management scheme requires great care and seldom improves system performance.

# SWI As A System Call

# • Totally different use of "interrupts" from everything else in this lecture

- So, first, any questions up to this point?

- The below technique is more common on larger systems, but still important

#### Background – what does a BIOS do?

- BIOS = "Basic Input/Output Subsystem"

- · Originated as a UV-EPROM on early microcomputers

- Knows how to get a keystroke input

- Knows how to write a character to the screen

- Knows how to write a sector to disk

- Keep real time clock

- In embedded, might also:

- Read/write serial port

- Read A/D; write D/A

# Simple But Fragile System Calls

## Old way – early personal computers (for example, Apple ][ )

- Write BIOS in assembly language

- Record start addresses of every service routine

- JSR to the service you want (e.g., GetKey EQU \$F75B

#### JSR GetKey )

# What if you need to change the BIOS?

- Need to preserve the entry points, but new software might be in different places

- Once you publish an entry point, you have to support it forever

- Can't just re-compile the applications; many are distributed as binary only

- Having a jump table at start of BIOS might help a bit

- Nth jump table entry is a vector to Nth BIOS service; updated with new version

### • What if you want to establish some sort of protected mode for the OS

- What if someone just JSRs to an address other than the designated service address?

- Without protection, tasks can access any OS fragment they want

33

# Using SWI As A System Call Solution: use SWI as a system call (or "service" call) · Put which OS function you want in A register • Put parameters in B, X, Y registers • Optionally can put other parameters on stack • IBM PC BIOS used this approach When you want a service, load A register and execute SWI LDAB OutByte ; data to send to serial port • e.g., ; function 7 outputs byte to serial port LDAA #7 SWI ; BIOS call = send data byte in B to serial port Advantages to SWI · SWI handler knows where services start - Can change entry points with ease when recompiling the BIOS • One place to handle all service calls - CPU can change protection modes when it executes SWI · Easier to protect BIOS code from malicious execution - Use memory management unit to block JSRs into BIOS • (Some CPUs don't push all registers on interrupt, so can be very fast as well)

# **Review**

Really "getting" interrupts is an essential embedded system skill

## Hardware interrupts

• Asynchronous, hardware-triggered cousin to SWI

# • What happens in a HW interrupt? (at a detailed level)

- Trigger interrupt and set I bit

- Save state

- Execute an Interrupt Service Routine specified by a vector

- Acknowledge or otherwise clear the interrupt (so it doesn't retrigger)

- Take care of any action needed (execute body of ISR)

- Clear I bit and resume execution of main program

# Timer example

- Real time clock from last lecture but done with interrupts

- Complete example in both assembler and C what do they do; how do they work?

• Basic idea of SWI as a service call