# <section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header>

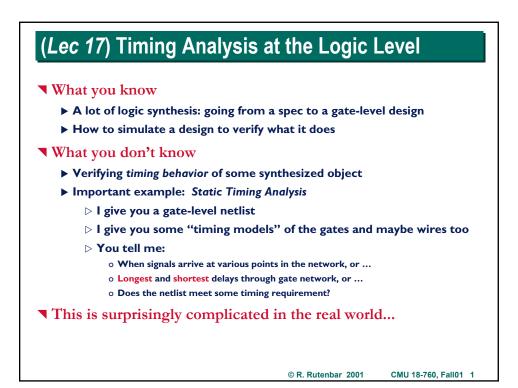

# Where Are We?

|          | Μ  | т  | W  | Th | F  |    |

|----------|----|----|----|----|----|----|

| Aug      | 27 | 28 | 29 | 30 | 31 | 1  |

| Sep      | 3  | 4  | 5  | 6  | 7  | 2  |

|          | 10 |    | 12 | 13 | 14 | 3  |

|          | 17 | 18 | 19 | 20 | 21 | 4  |

|          | 24 | 25 | 26 | 27 | 28 | 5  |

| Oct      |    | 2  | 3  | 4  | 5  | 6  |

|          | 8  | 9  | 10 |    | 12 | 7  |

|          | 15 | 16 | 17 | 18 | 19 | 8  |

|          | 22 | 23 | 24 | 25 | 26 | 9  |

| Nov      | 29 | 30 | 31 |    | 2  | 10 |

|          | 5  | 6  | 7  | 8  | 9  | 11 |

|          | 12 | 13 | 14 | 15 | 16 | 12 |

| Thnxgive | 19 | 20 | 21 | 22 | 23 | 13 |

|          | 26 | 27 | 28 | 29 | 30 | 14 |

| Dec      | 3  | 4  | 5  | 6  | 7  | 15 |

|          | 10 |    | 12 | 13 | 14 | 16 |

|          |    |    |    |    |    |    |

| Introduction                  |

|-------------------------------|

| Advanced Boolean algebra      |

| JAVA Review                   |

| Formal verification           |

| 2-Level logic synthesis       |

| Multi-level logic synthesis   |

| Technology mapping            |

| Placement                     |

| Routing                       |

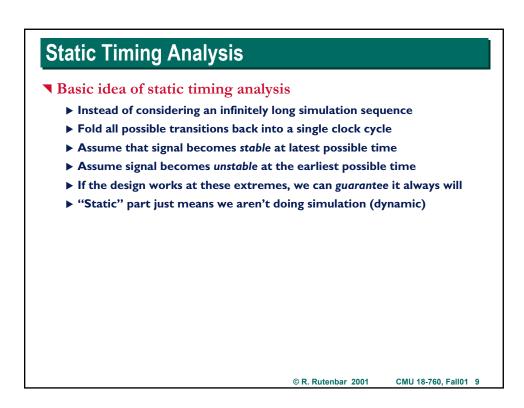

| Static timing analysis        |

| Electrical timing analysis    |

| Geometric data structs & apps |

|                               |

|                               |

|                               |

© R. Rutenbar 2001

CMU 18-760, Fall01 4

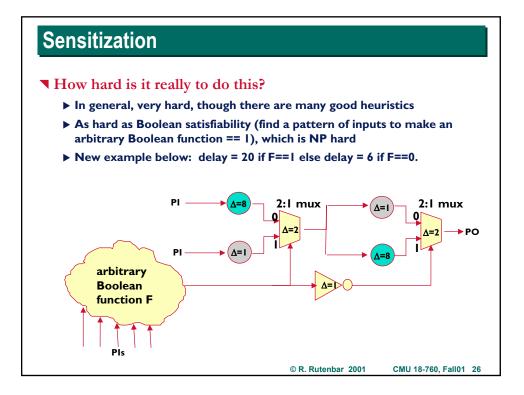

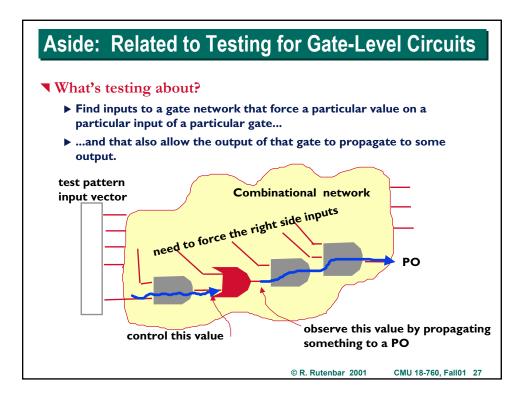

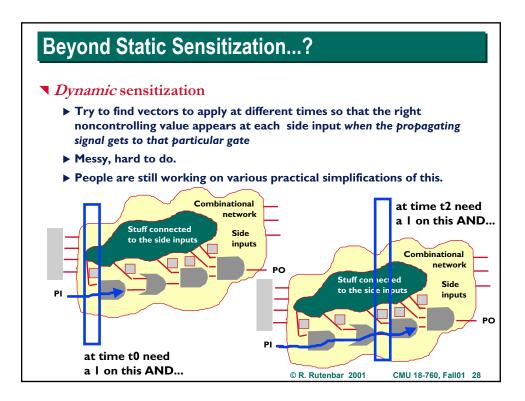

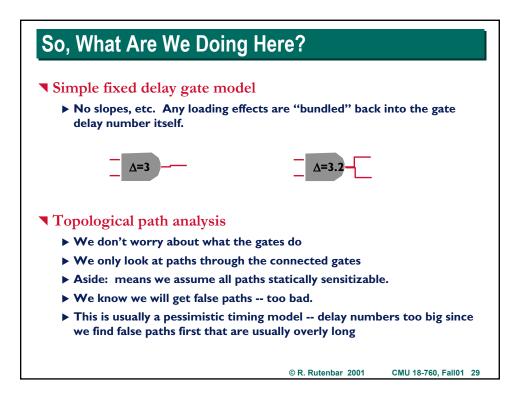

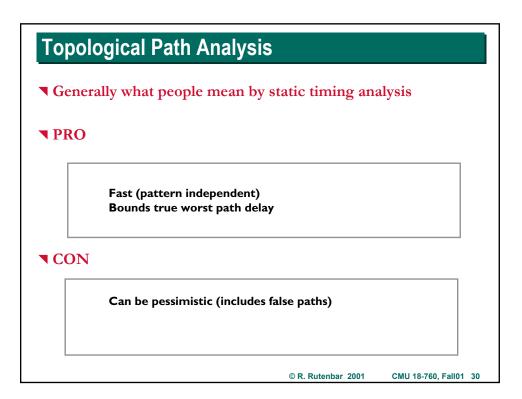

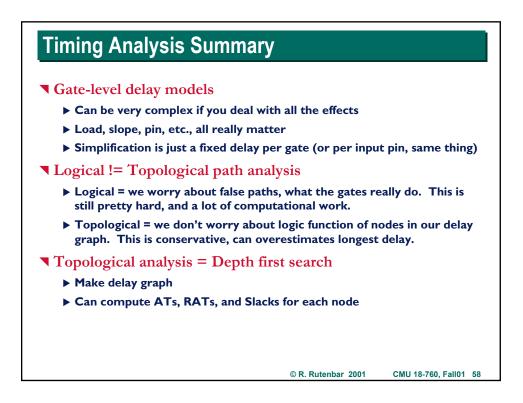

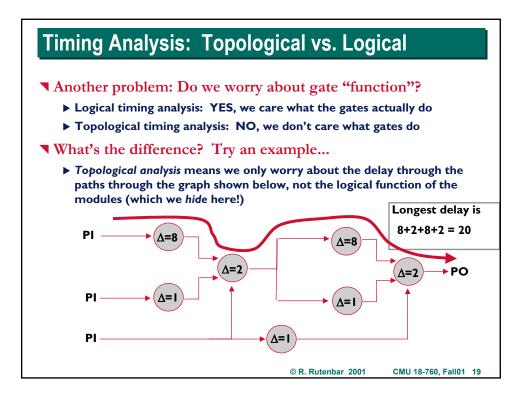

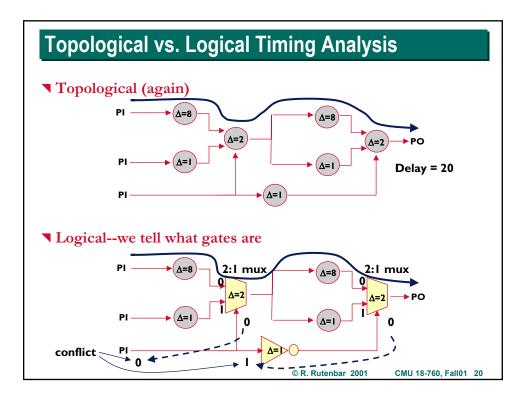

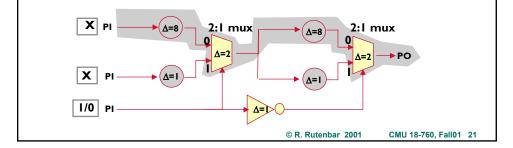

## False Paths and Path Sensitization

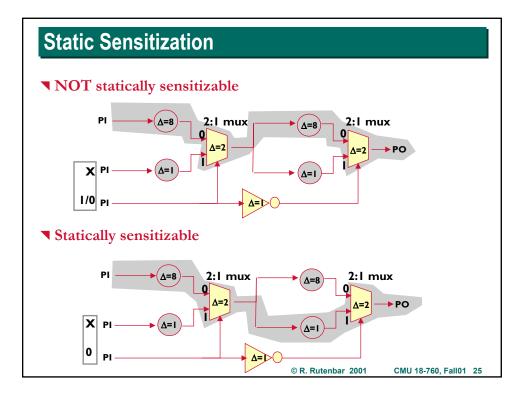

### ■ Oops. We got a *false path*

- ▶ It is not possible to apply a set of inputs that will cause a logic signal to propagate down this supposed "longest" path from PI to PO

- ► This path we found by topological analysis is called a FALSE PATH

- ▶ We got this because we didn't care what the gates did

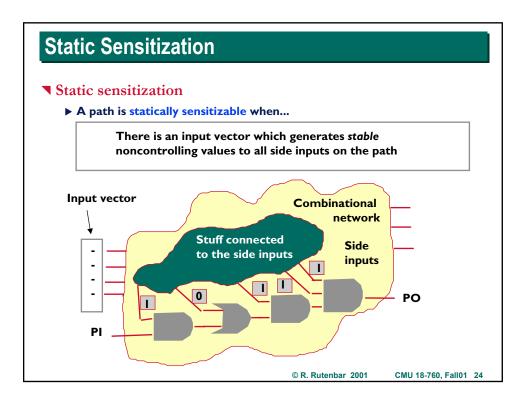

### Sensitization

▶ A path is said to be *sensitized* when it allows a logic signal to propagate along it. In this example, there is no way to sensitize this path

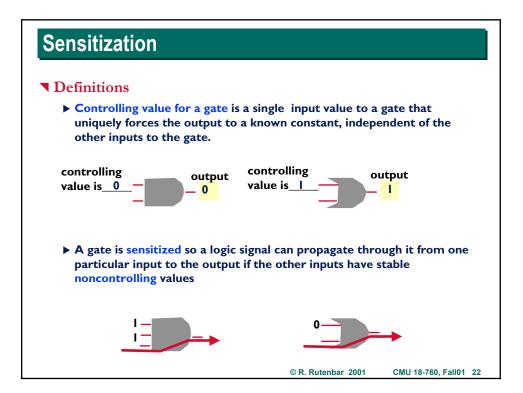

# Sensitization

### Definitions

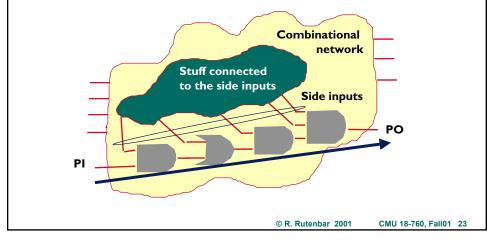

- ► A path is a set of connected gates and wires that starts with some PI and ends with some PO. Path is defined by I input and I output per gate

- ▶ Side inputs on a path are the "other" inputs to these gates on the path.