# (Lec 13) Placement & Partitioning: Part II

### What you know

- ▶ That there are 3 big placement styles: iterative, recursive, direct

- > Placement via iterative improvement using simulated annealing

### What you don't know

- ▶ The other 2: recursive and direct placement

- ▶ The fact that they have many points of great similarity

- ▶ Real algorithms for doing recursive or direct placement

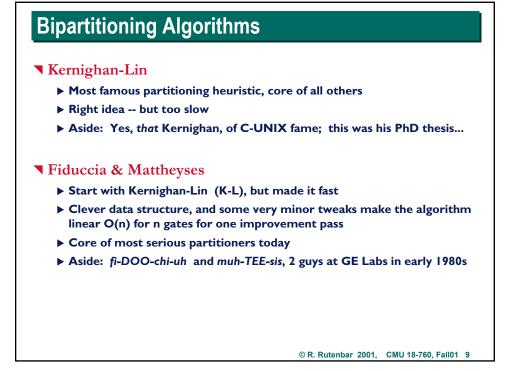

- Recursive: 2 most famous heuristics: K&L, F&M

### What's later still (part III)

► Direct: classical quadratic formulation + Tsay-style legalization

# Where Are We?

### ▼ Physical design--placement via recursive, direct methods

|          | Μ  | Т  | W  | Th | F  |    |

|----------|----|----|----|----|----|----|

| Aug      | 27 | 28 | 29 | 30 | 31 | 1  |

| Sep      | 3  | 4  | 5  | 6  | 7  | 2  |

|          | 10 |    | 12 | 13 | 14 | 3  |

|          | 17 | 18 | 19 | 20 | 21 | 4  |

|          | 24 | 25 | 26 | 27 | 28 | 5  |

| Oct      |    | 2  | 3  | 4  | 5  | 6  |

|          | 8  | 9  | 10 |    | 12 | 7  |

| Midsem   | 15 | 16 | 17 | 18 | 19 | 8  |

| break 🔺  | 22 | 23 | 24 | 25 | 26 | 9  |

|          | 29 | 30 | 31 | 1  | 2  | 10 |

| Nov      | 5  | 6  | 7  | 8  | 9  |    |

|          | 12 | 13 | 14 | 15 | 16 | 12 |

| Thnxgive | 19 | 20 | 21 | 22 | 23 | 13 |

|          | 26 | 27 | 28 | 29 | 30 | 14 |

| Dec      | 3  | 4  | 5  | 6  | 7  | 15 |

|          | 10 | 11 | 12 | 13 | 14 | 16 |

|          |    |    |    |    |    |    |

Introduction Advanced Boolean algebra JAVA Review Formal verification 2-Level logic synthesis Multi-level logic synthesis Technology mapping

### Placement

Routing Static timing analysis Electrical timing analysis Geometric data structs & apps

© R. Rutenbar 2001, CMU 18-760, Fall01 3

# Deadlines

### ■ Project2

- November 8 (next THU)

- Email us your website URL

- Homework 4 (still TBD on the .pdf on website)

- Propose: Nov 15 (Thu in class)

**Paper #2**

- Propose Nov 13 (Tue in class)

- Decided for this one to still be written we'll do PPT for Paper3

### What's left in 760

- ► HW5 (layout, timing), HW6 (geometric data structs, short)

- Project 3 (a REAL floorplanner pay attn to last prob on HW4!)

- Paper 3 something about layout

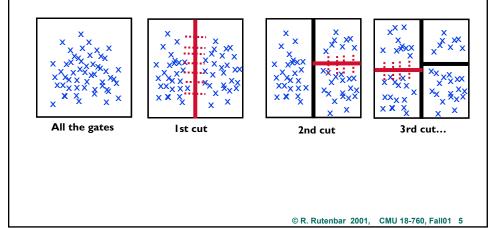

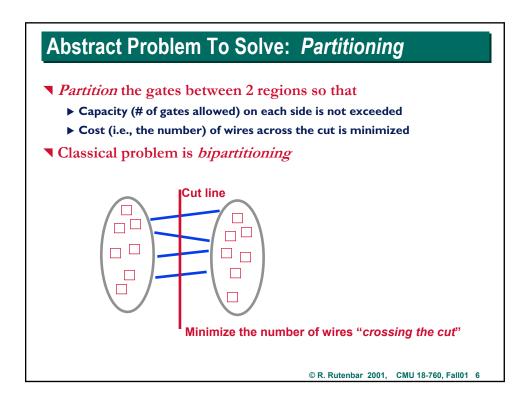

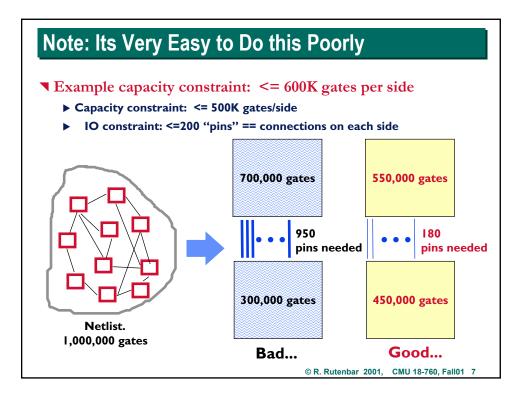

# **Recursive Placement: Min-Cut**

### **Basic idea**

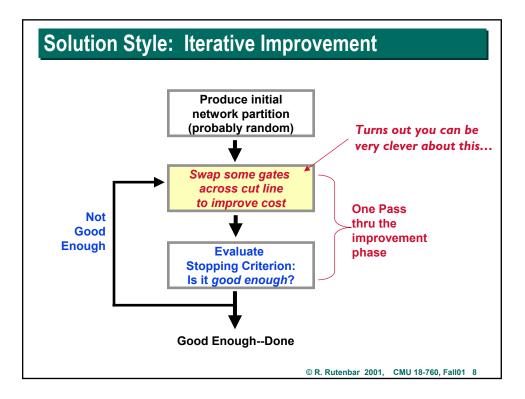

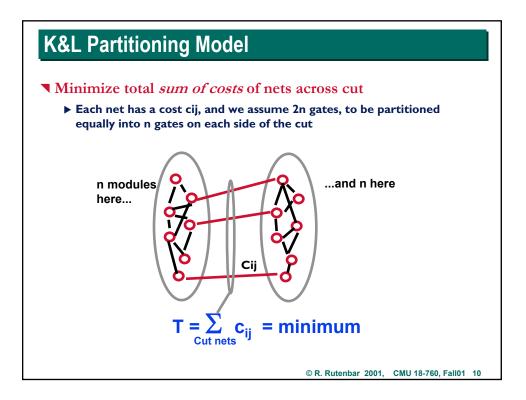

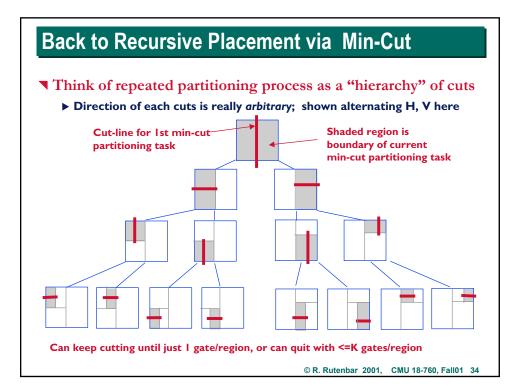

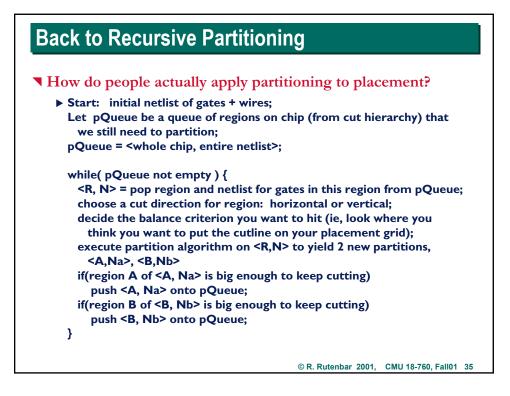

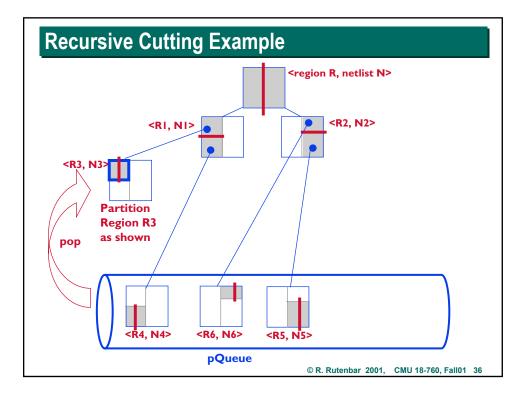

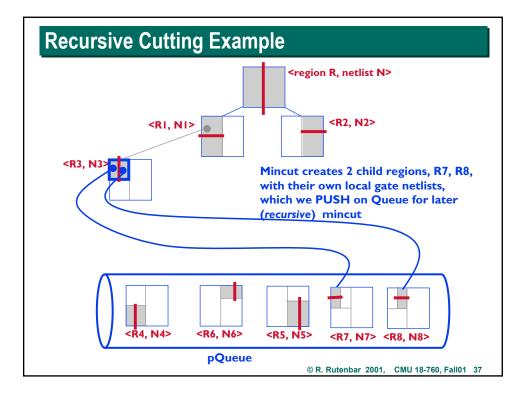

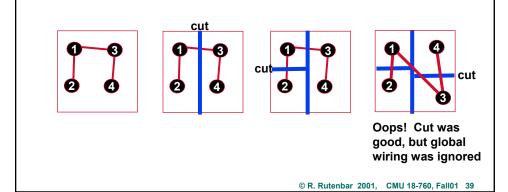

- ► The "simplest" placement decision you can make is: cut the chip into 2 pieces, partition gates over the 2 sides, minimize wiring in between

- ► Can continue doing this recursively with results of each partition step

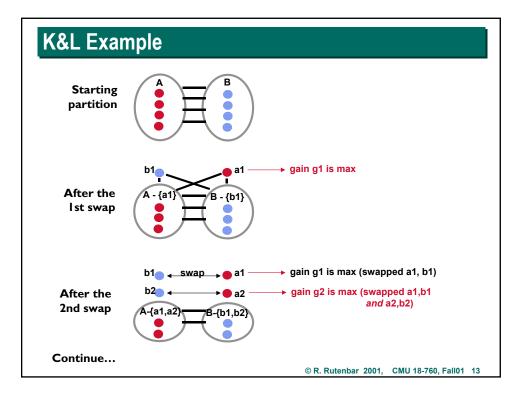

| K&L: Critical                     | Ideas                                                                          |

|-----------------------------------|--------------------------------------------------------------------------------|

| <b>▼</b> Gain                     |                                                                                |

|                                   | ge in cost that results from swapping one gate in the A-<br>ate in the B-side. |

| ► Compute it as                   | Σ <sub>cut</sub> cij - Σ <sub>cut</sub> cij<br>After Before<br>swap swap       |

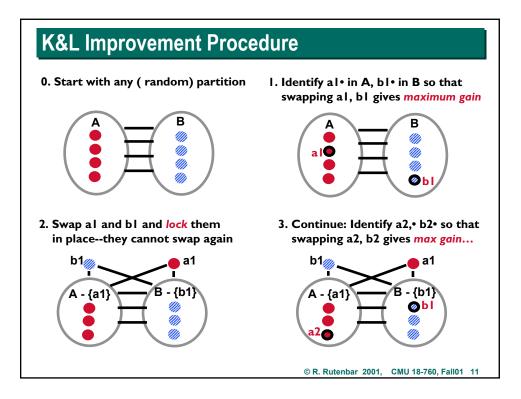

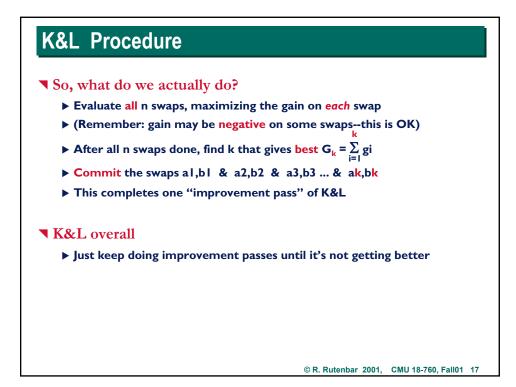

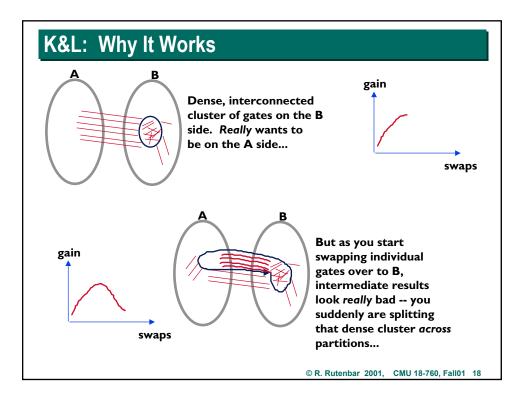

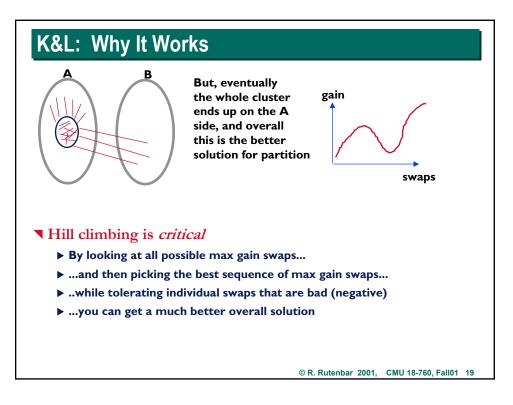

| ■ Be <i>greedy</i> , but <i>p</i> | Dersevere                                                                      |

| Always do the v                   | ery <mark>best</mark> next swap (biggest Gain number) you can                  |

| Do this swap ev                   | en if it's negative, ie, even if it makes the partition worse                  |

| ► So, the swap to                 | pick is the strictly biggest gain:                                             |

| Biggest pos                       | itive gain (makes cut better)                                                  |

| ⊳ Smallest (c                     | losest to 0) negative gain (makes cut the least worse)                         |

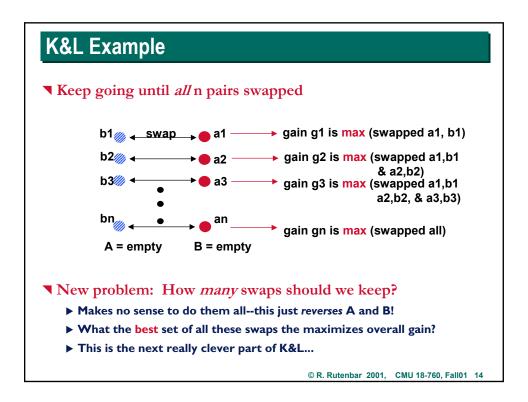

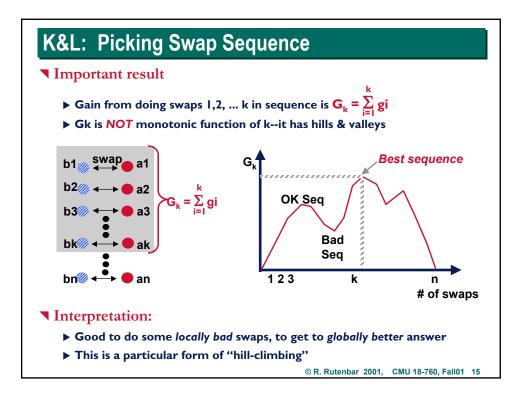

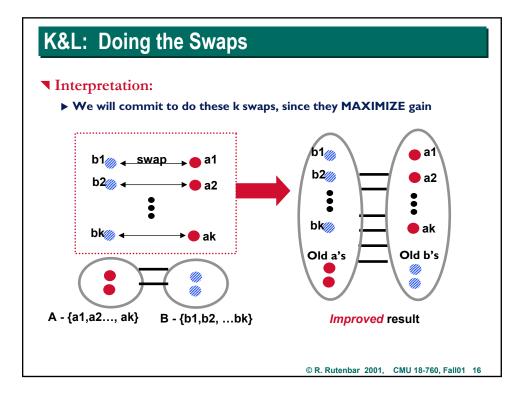

| ■ Do all n swaps                  |                                                                                |

| ►ie, swap until                   | nothing is left to swap.                                                       |

| -                                 | © R. Rutenbar 2001, CMU 18-760, Fall01 12                                      |

Page 13

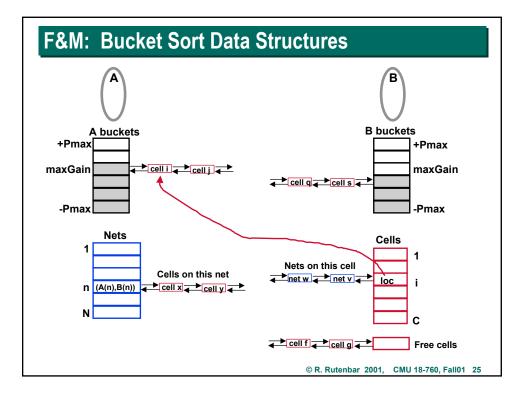

## F&M Bucket Data Structure

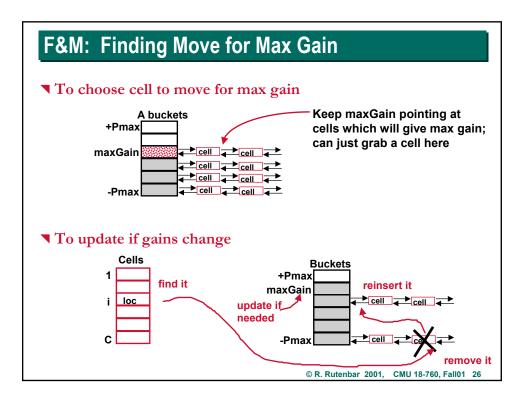

### ■ How much time to find max gain move?

- ► Constant time, O(1), just look at maxGain slot in buckets

- ► Also, to maintain maxGain in constant time, assuming you have to know where all the cells are; again just some pointer hacking

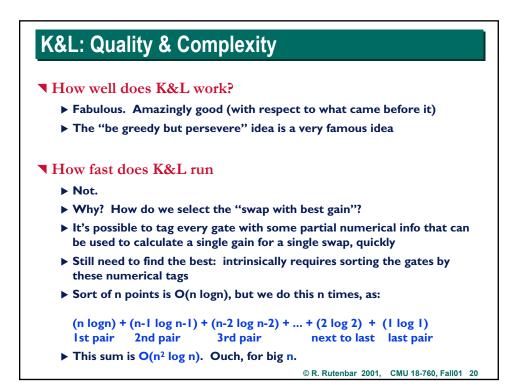

- ► To move n cells, F&M is O(n), K&L was O(n<sup>2</sup> log n)

- Big improvement!

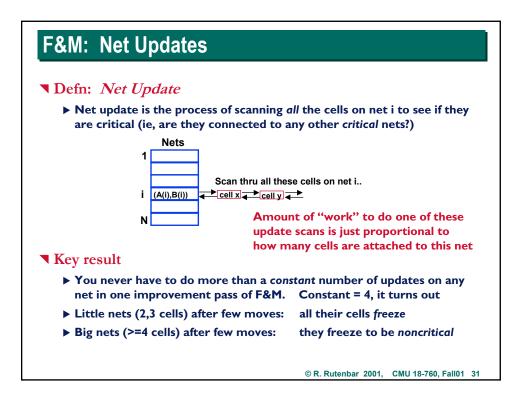

### What's left?

- ▶ How to update all gains on all affected cells when we move one cell ?

- ► K&L assumed this was O(n) for a single swap (you might to update all the cells), so was O(n<sup>2</sup>) to do all n swaps

- ▶ How do we improve on this?

### Page 15

# F&M: Summary

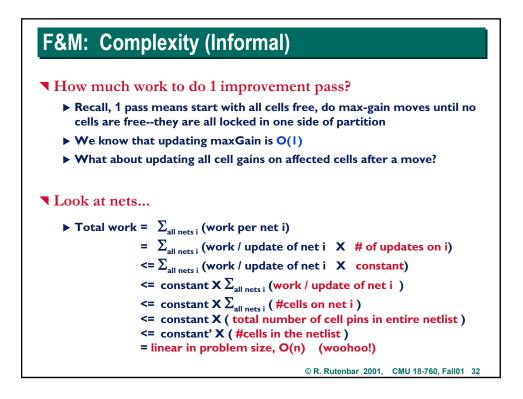

### Complexity of 1 pass is *linear* in problem size

A very important and practical result

### ■ Impact

- ▶ Everybody liked results K&L was capable of getting

- ► F&M preserves the overall improvement strategy, but makes it extremely fast, linear in problem size

- ► Can attack very large netlists with F&M, ~I M cells

- > This is now one of the default, standard ways to do big partitioning probs

### ■ How about today...?

- ► Additional set of ideas improves this further, uses some hierarchical clustering, and some other clever stuff.

- Best tool around today is called "hMetis", from U Minnesota. You can get it from their web page; like CUDD, widely used, easy to use.

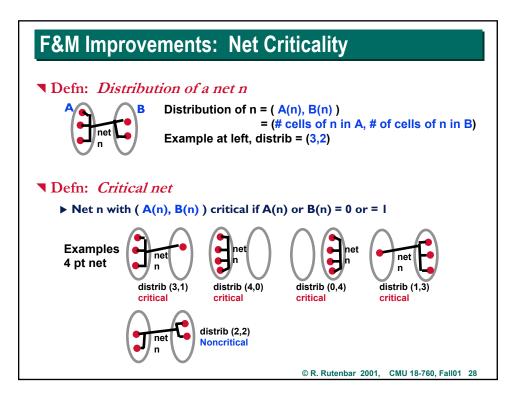

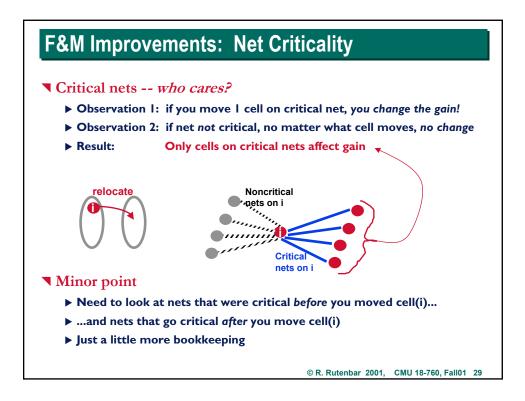

# **Partition Optimizations**

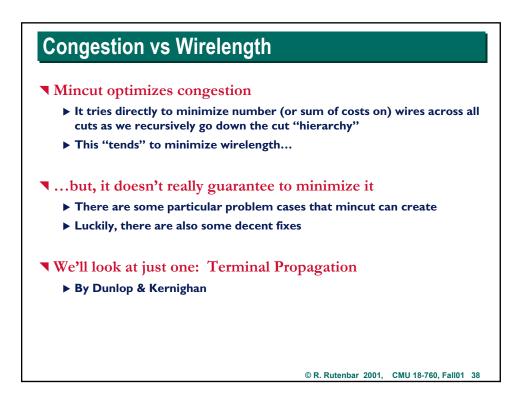

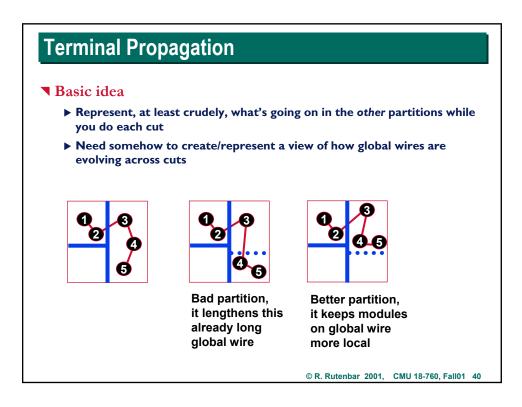

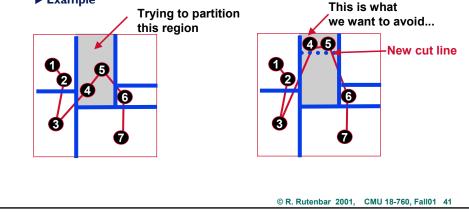

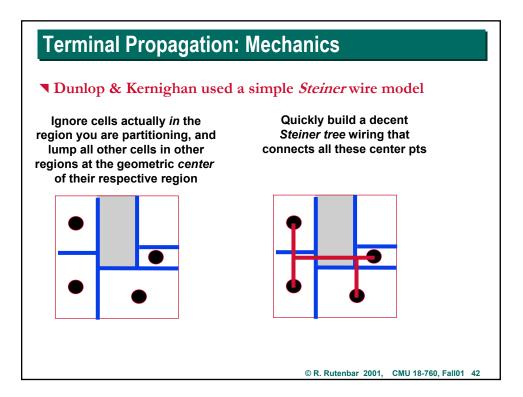

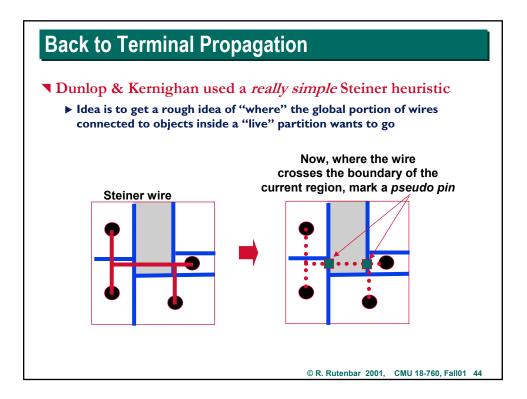

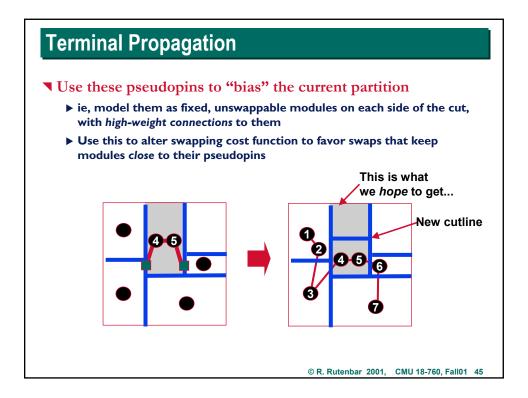

### **▼**Terminal propagation

- ► Now a standard technique, introduced by Dunlop and Kernighan of Bell Labs, for use with Kernighan-Lin partitioning improvement

- Idea: enforce some "coupling" between objects that are connected, but which have ended up in different regions after a hierarchy of slicing cuts

# **Terminal Propagation**

### Mechanics

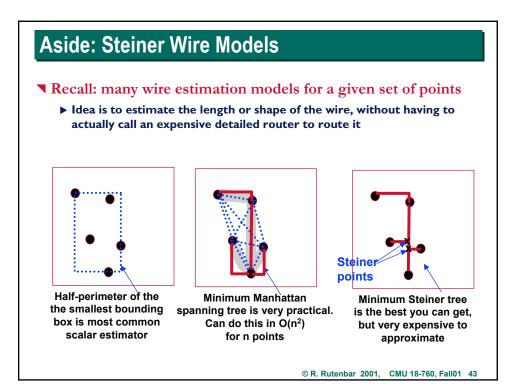

> You try to build a crude "geometric wire model" for the wires that are going across the other cuts, and use this to bias your current partitioning task to minimize spreading connected objects across the the current cut

# <section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>