# (Lec 10) Technology Mapping

#### ■ What you know: Synthesis--*all* there is

- ► 2-level ESPRESSO style

- Multi-level style

- > Structural modifications to Boolean Logic Network

- > Subexpression extraction: cube & kernel extraction

- > Vertex simplification via multi-level don't cares

#### ▶ Clever representation schemes to make these doable

- PCN inside ESPRESSO

- BDDs everywhere else

#### What you don't know

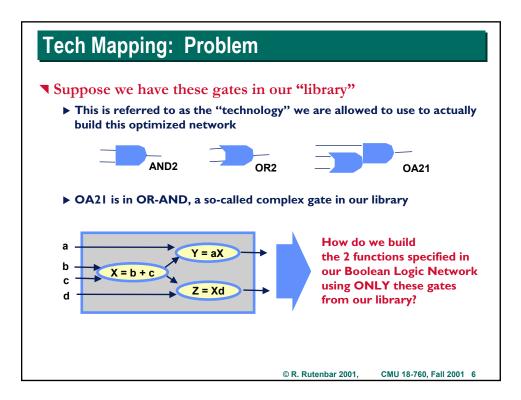

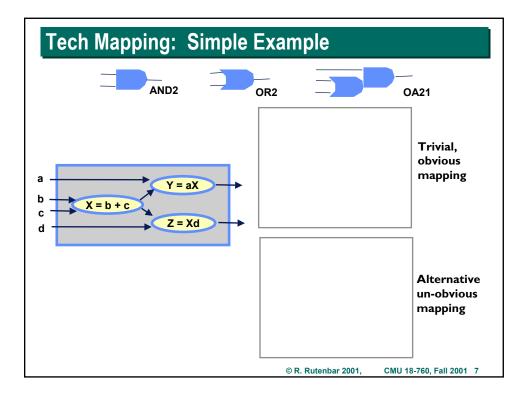

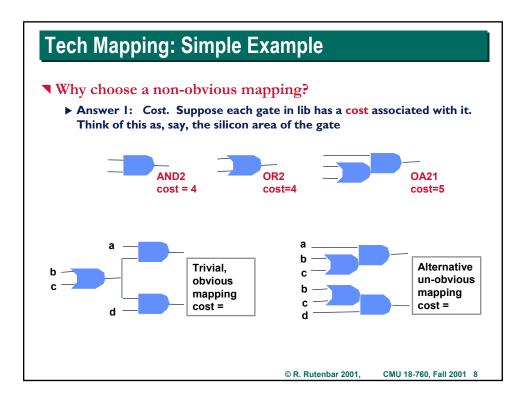

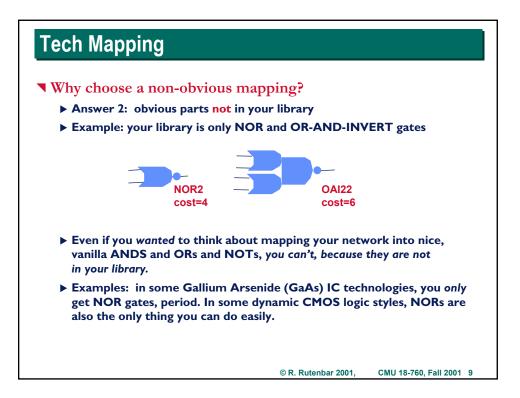

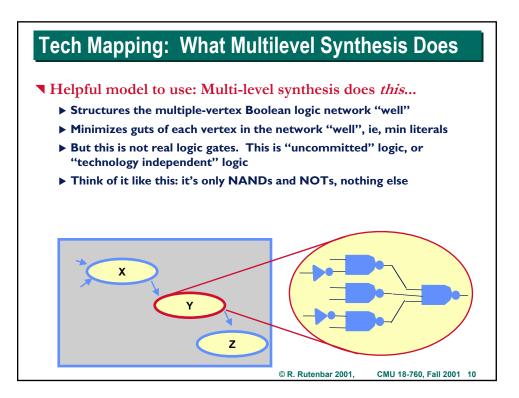

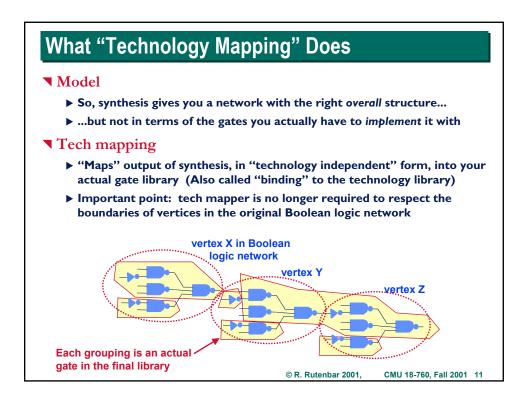

► How a synthesized multi-level logic network gets turned into real, live, usable gates in your implementation

© R. Rutenbar 2001, CMU 18-760, Fall 2001 1

<section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header>

## Where Are We?

#### ■ *After* logic synthesis--how to map to *real* library of gates?

|          | Μ  | т  | W  | Th | F  |    |

|----------|----|----|----|----|----|----|

| Aug      | 27 | 28 | 29 | 30 | 31 | 1  |

| Sep      | 3  | 4  | 5  | 6  | 7  | 2  |

|          | 10 |    | 12 | 13 | 14 | 3  |

|          | 17 | 18 | 19 | 20 | 21 | 4  |

|          | 24 | 25 | 26 | 27 | 28 | 5  |

| Oct      |    | 2  | 3  | 4  | 5  | 6  |

|          | 8  | 9  | 10 |    | 12 | 7  |

| Midsem   | 15 | 16 | 17 | 18 | 19 | 8  |

| break 🔺  | 22 | 23 | 24 | 25 | 26 | 9  |

|          | 29 | 30 | 31 | 1  | 2  | 10 |

| Nov      | 5  | 6  | 7  | 8  | 9  | П  |

|          | 12 | 13 | 14 | 15 | 16 | 12 |

| Thnxgive | 19 | 20 | 21 | 22 | 23 | 13 |

|          | 26 | 27 | 28 | 29 | 30 | 14 |

| Dec      | 3  | 4  | 5  | 6  | 7  | 15 |

|          | 10 |    | 12 | 13 | 14 | 16 |

|          |    |    |    |    |    |    |

Introduction Advanced Boolean algebra JAVA Review Formal verification 2-Level logic synthesis Multi-level logic synthesis

#### Technology mapping

Placement Routing Static timing analysis Electrical timing analysis Geometric data structs & apps

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 3

# Readings

#### **De Micheli**

- Chapter 10 is all about is all about technology mapping, which he calls "cell library binding"

- ▶ Read 10.1, 10.2, 10.3 (but only 10.3.1 here) and also 10.6

# <section-header><section-header><section-header><section-header><list-item><list-item>

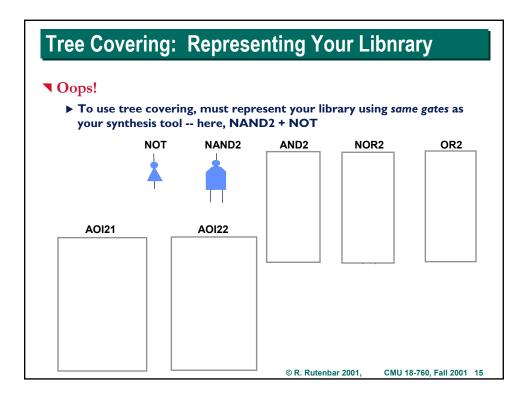

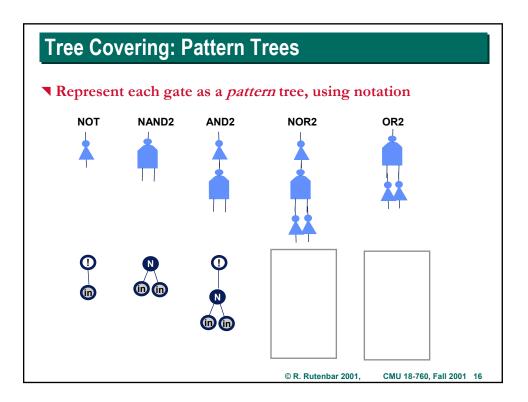

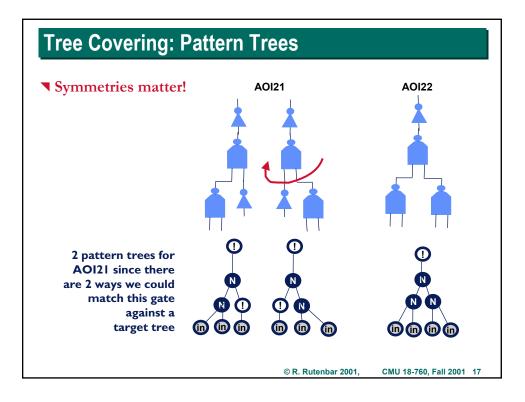

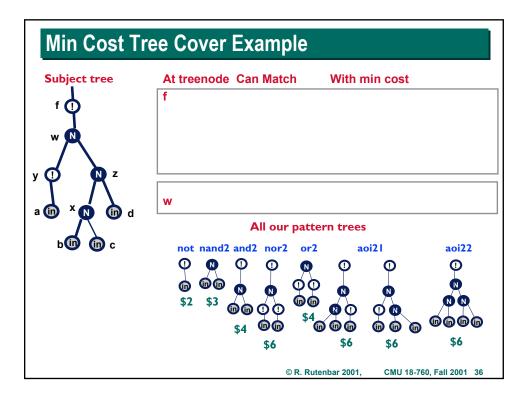

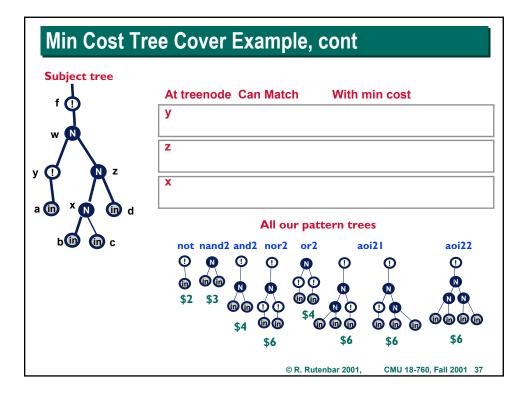

# Technology Mapping as Tree Covering

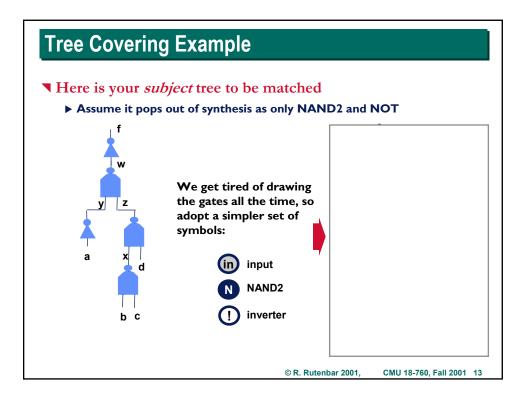

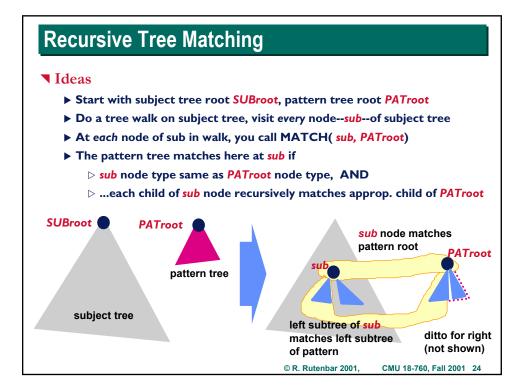

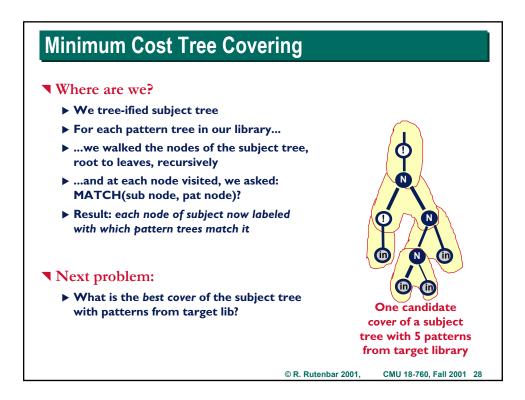

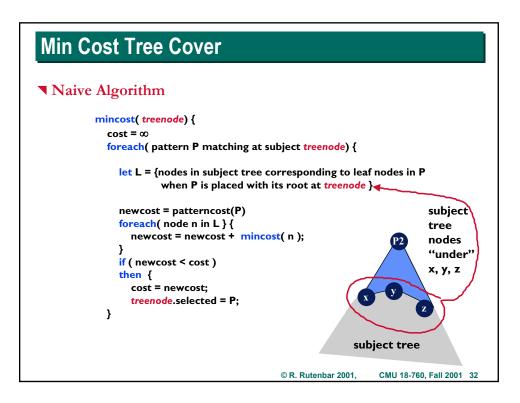

■ One particularly useful, simple model of problem

- > Your logic network to be mapped is a tree of simple gates

- > Easiest to assume absolutely minimal gate types

- **Example:** tech-independent form is 2 input NAND and NOT

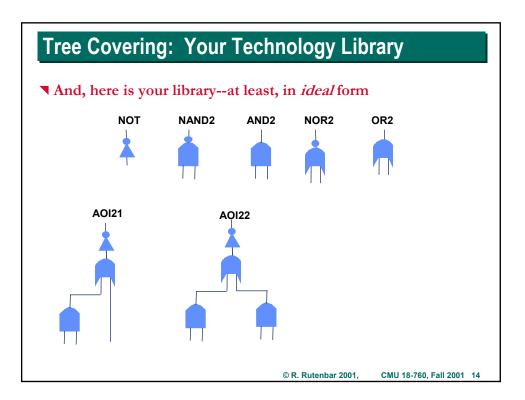

- > Your library of actual gate types is also available in this form

- > Each gate can be represented as a tree of NAND2 and NOT

- > Each gate also has an associated cost

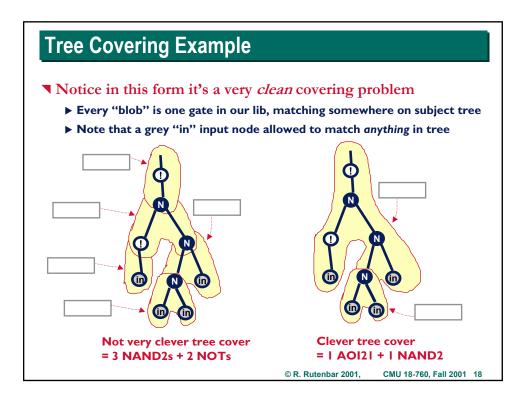

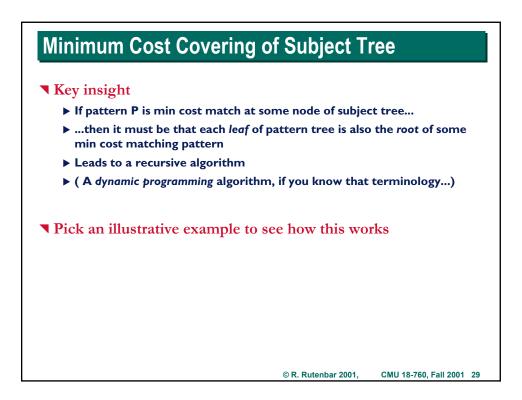

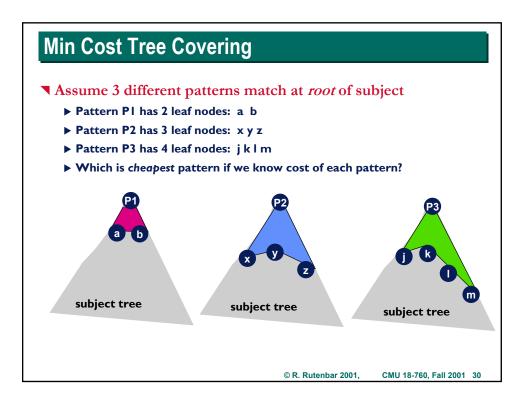

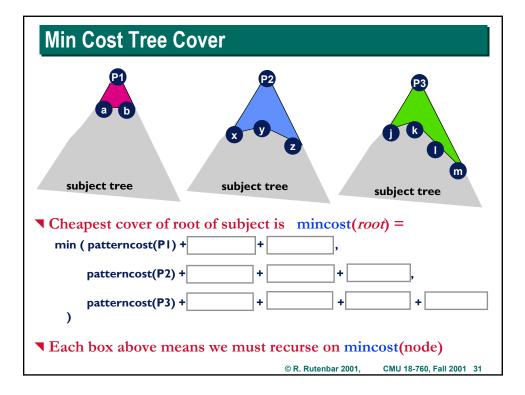

#### **Problem**

- "Cover" the tree that represents your tech-independent logic-called the subject tree...

- ...with minimum cost set of gates (each a pattern tree) from lib

- **Reduces tech mapping to: matching problem + a minimization problem**

Page 11

#### There are several approaches

- ► Elegant, complicated approach: FSM matching

- > Treat subject tree like a special "string" of characters

- > Turn the pattern library into a Finite State Machine (FSM)

- $\triangleright$  Run the subject "string" thru the FSM, it tells you each place in subject tree that ANY tree in library matches

- > Fast, cool, hard to describe quickly (see book)

- ▶ Straightforward, not-so-fast, easy approach: Recursive matching

- > Inputs: subject tree (root), a specific target pattern tree (root)

- > Outputs: each node in subject tree marked if pattern matches

- > Note: need to run this algorithm for every target tree in library

Page 13

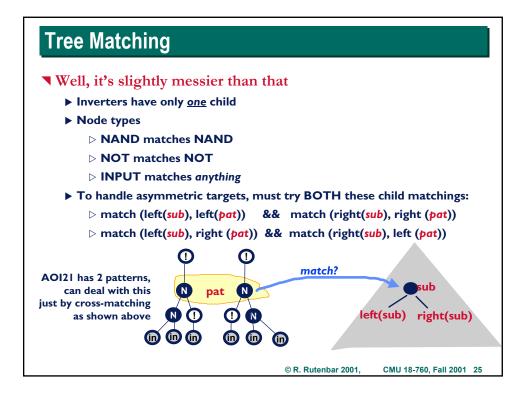

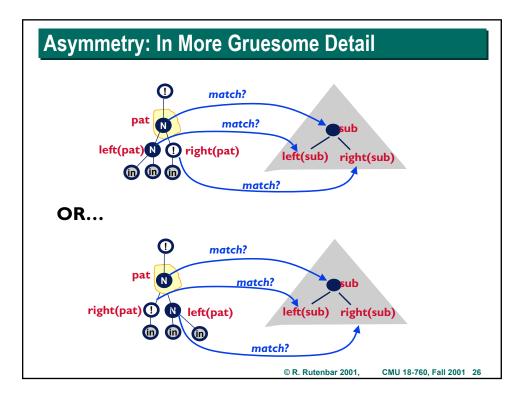

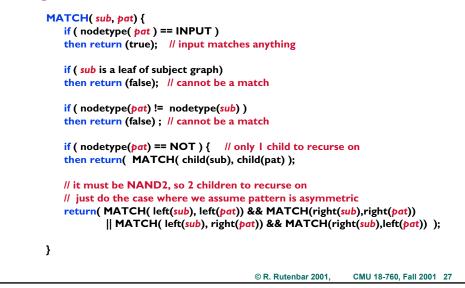

## **Tree Matching**

#### Algorithm outline

### Issues

#### **▼**Pro

- Easy, simple algorithm

- Works great for trees

#### Con

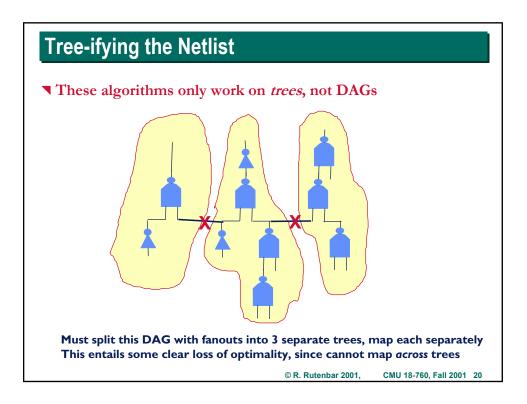

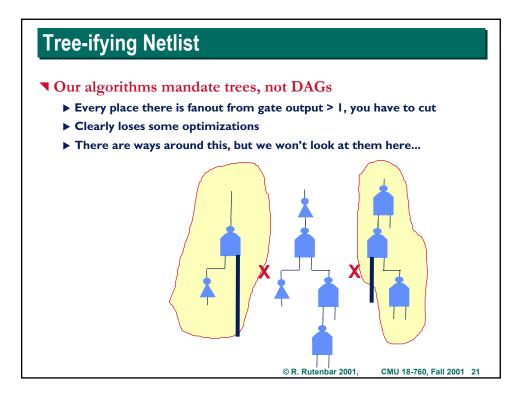

- ► Not everything is a tree

- ▶ Most subject netlists are NOT trees, need to chop up into trees

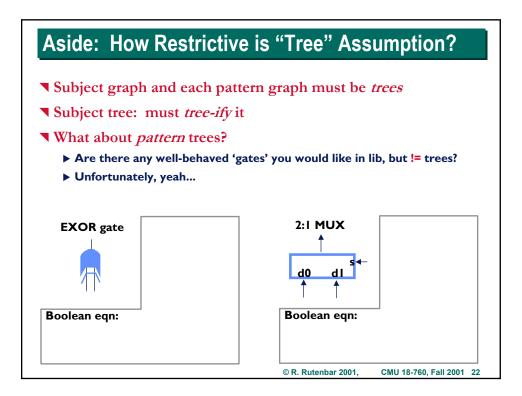

- Some patterns cannot be trees (EXOR, MUX)

#### Comments

- Heuristic tricks for dealing with most of these

- Also, other tech mapping approaches

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 39

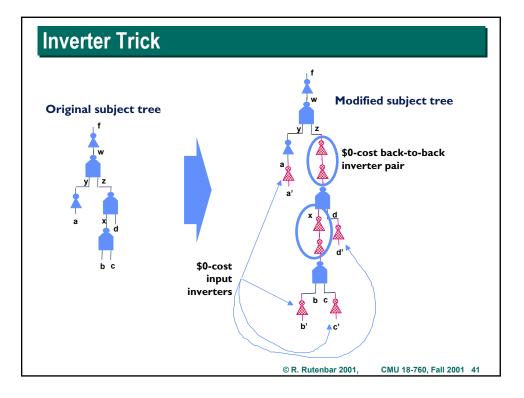

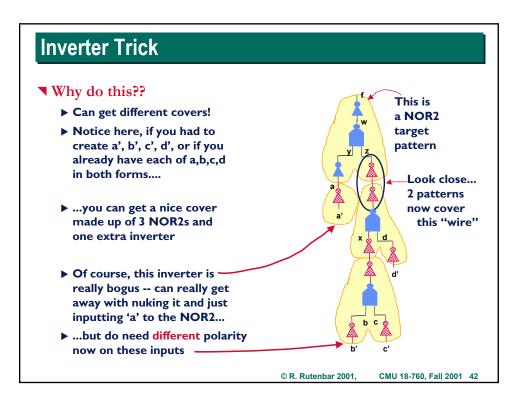

# Polarity Assignment

#### One cool trick worth mentioning

- ▶ What if you can't match a pattern just because you don't have the right polarities (true / complemented form) on internal nodes of subject tree?

- ► Just don't use that good pattern? No -- fix the polarity

#### Do this to netlist

- ► At every *internal* wire in netlist (from a gate output to a gate input) where there is *no* inverter, replace with *back*-to-*back* inverters

- > At every input, add one more zero-cost-inverter

#### **Do this to pattern library**

- Add back-to-back inverter pattern with cost = 0, on every internal wire (from a gate output to a gate input) in your pattern trees

- > Add zero-cost-inverter pattern, only matches at inputs, cost=0

## Summary

#### **▼**Technology mapping ...

- Synthesis gives you "uncommitted" or "technology independent" design, eg, NAND2 and NOT

- ▶ Mapping turns this into real gates in your own library

- ► Can determine difference between good implementation and a bad one

- ► Still a very hot problem

#### **▼**Tree covering

- ▶ One nice, simple, elegant approach to the problem

- ▶ 3 parts: tree-ify input, match all lib patterns, find min cost cover

#### **Tricks**

Adding extra inverters (with cost) can get you out of nasty problems where a nice pattern does't match because of wrong polarity at inputs