# (Lec 9) Multi-Level Min III: Role of Don't Cares

#### What you know

- > 2-level minimization a la ESPRESSO

- Multi-level minimization:

- > Boolean network model,

- > Algebraic model for factoring

- > Rectangle covering for extraction

#### What you don't know

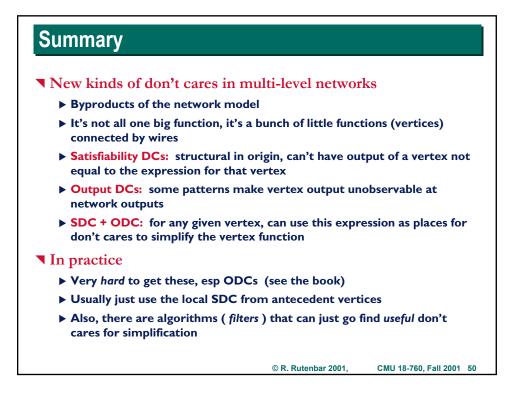

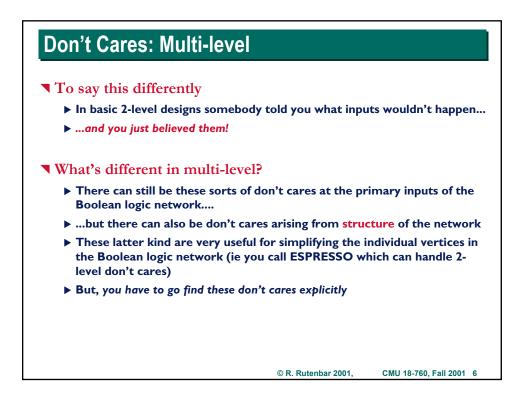

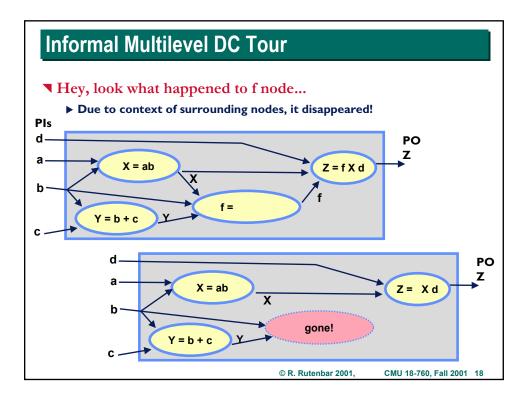

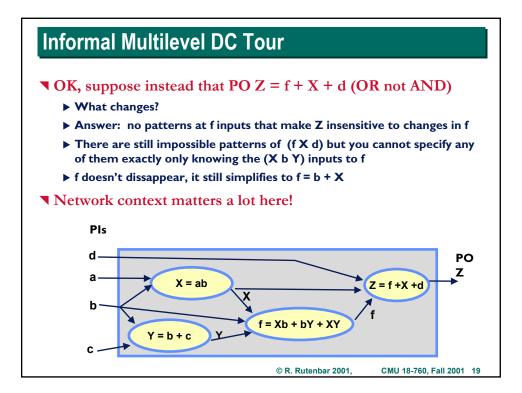

- > Don't cares in a multi-level network are very different

- > They arise naturally as part of the structure of the network model

- > They can help a great deal in simplifying the network

- > They can be very hard to get, algorithmically

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 1

## Where Are We?

#### ▼ In logic synthesis--how *don't cares* are now *very* different beasts

|          | Μ  | Т  | W  | Th | F  |    |

|----------|----|----|----|----|----|----|

| Aug      | 27 | 28 | 29 | 30 | 31 | 1  |

| Sep      | 3  | 4  | 5  | 6  | 7  | 2  |

|          | 10 |    | 12 | 13 | 14 | 3  |

| Oct      | 17 | 18 | 19 | 20 | 21 | 4  |

|          | 24 | 25 | 26 | 27 | 28 | 5  |

|          |    | 2  | 3  | 4  | 5  | 6  |

|          | 8  | 9  | 10 | 11 | 12 | 7  |

|          | 15 | 16 | 17 | 18 | 19 | 8  |

|          | 22 | 23 | 24 | 25 | 26 | 9  |

| Nov      | 29 | 30 | 31 | 1  | 2  | 10 |

|          | 5  | 6  | 7  | 8  | 9  | 11 |

|          | 12 | 13 | 14 | 15 | 16 | 12 |

| Thnxgive | 19 | 20 | 21 | 22 | 23 | 13 |

|          | 26 | 27 | 28 | 29 | 30 | 14 |

| Dec      | 3  | 4  | 5  | 6  | 7  | 15 |

|          | 10 |    | 12 | 13 | 14 | 16 |

|          |    |    |    |    |    |    |

Introduction Advanced Boolean algebra JAVA Review Formal verification 2-Level logic synthesis Multi-level logic synthesis Technology mapping Placement Routing Static timing analysis Electrical timing analysis Geometric data structs & apps

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 3

# **Readings/Deadlines/Projects**

#### **De Micheli**

Section 8.4 is about don't cares in multilevel model

#### **Deadlines**

- ► Today, Thu Oct 11: Paper I Review, Rudell's Dynamic Ordering due

- ► Thursday Oct 18: HW3 (2-level, multi-level synthesis) due

- > As always, check webpage for bugfixes, updates...

- D There are some bugs in eqns for Prob #1, fixed shortly... The state diagrams are correct as is.

#### ■ Project #2

We'll do the overview next Tuesday

## Don't Cares: 2-level

In basic digital design...

- ▶ We told you these were just input patterns that could never happen

- This allowed you to do more simplifications, since you could add a 1 or 0 to the Kmap for that input depending on what was easier to simplify

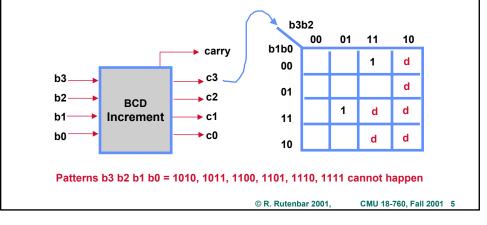

- ► Standard example: BCD incrementer circuit

###

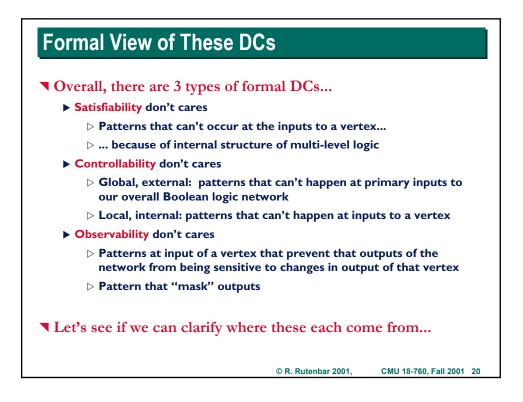

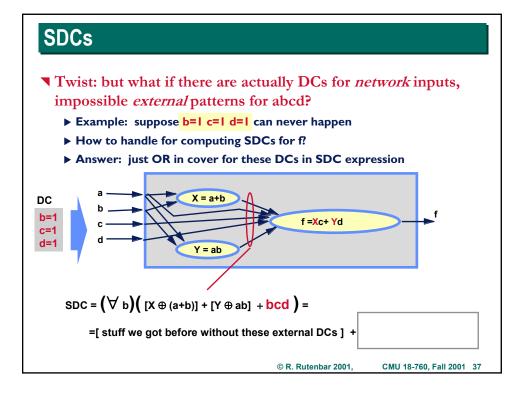

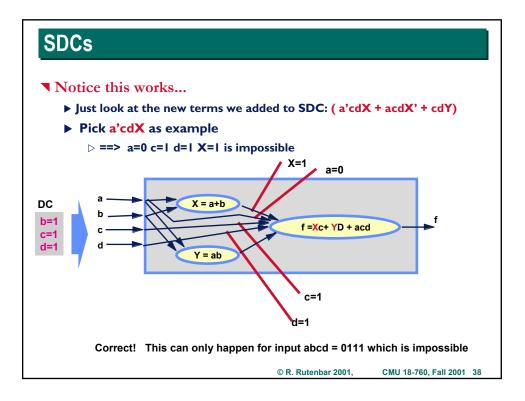

- But, we've already seen these!

- External global CDCs: come from outside for entire network, like b=1 c=1 d=1 is impossible, in our example

- ▶ Internal local CDCs: just patterns that cannot appear at any vertex

=

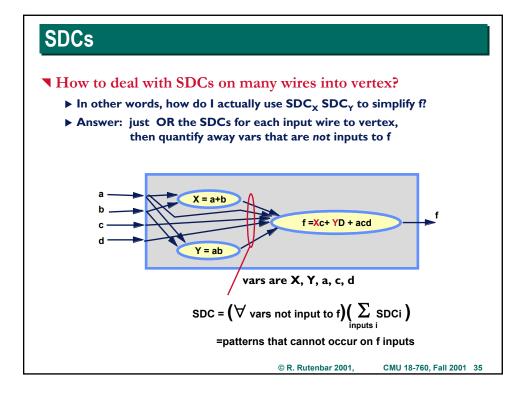

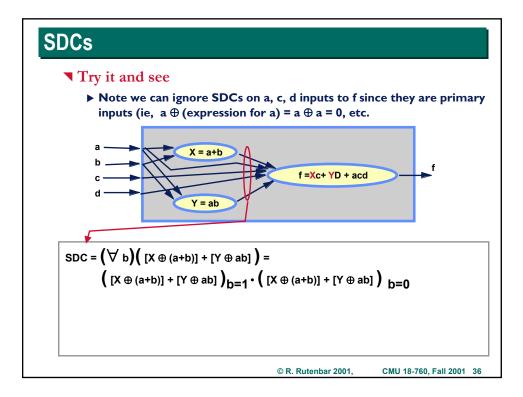

$$(\forall \text{ vars not inputs })(\sum_{\text{vertex}} (\text{local SDCs}) + \text{ext. global CDC})$$

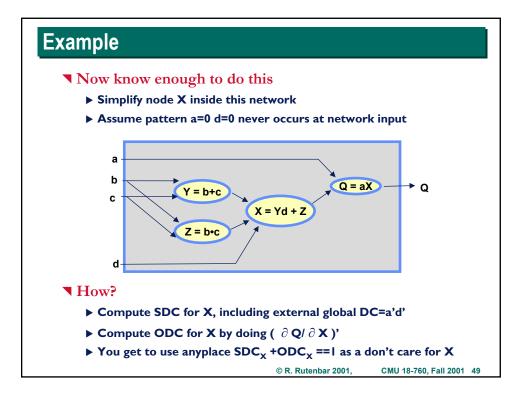

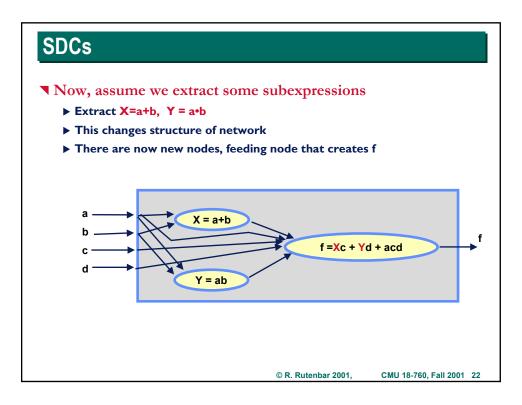

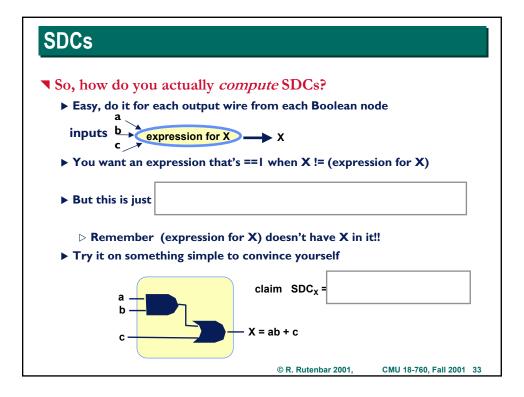

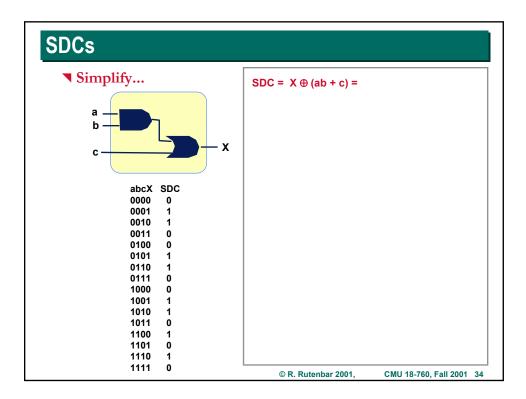

■ SDCs versus CDCs ...?

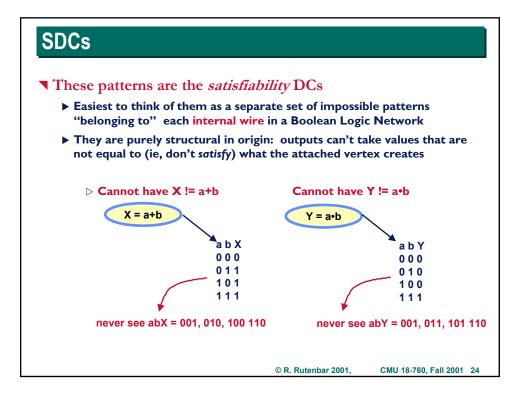

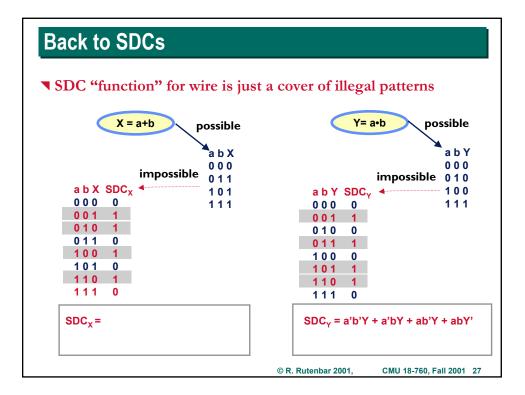

- **SDCs:** think of as belonging to each internal wire in network

- CDCs: think of as belonging to each internal vertex in network

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 39

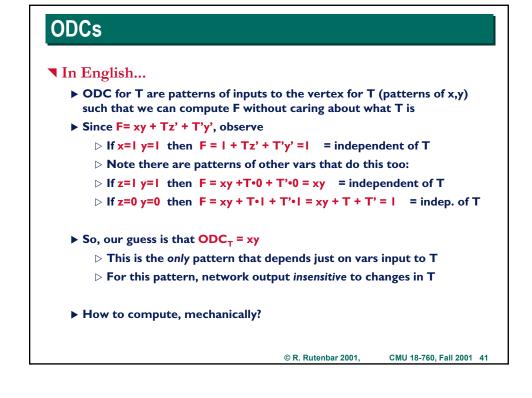

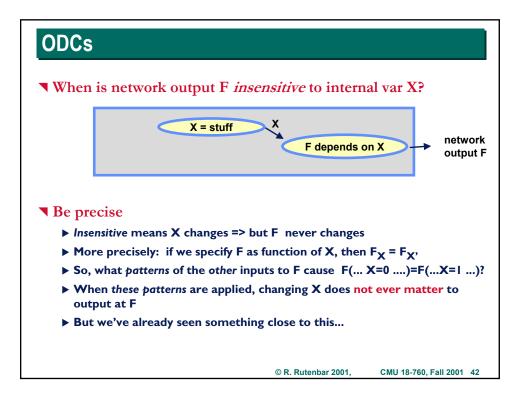

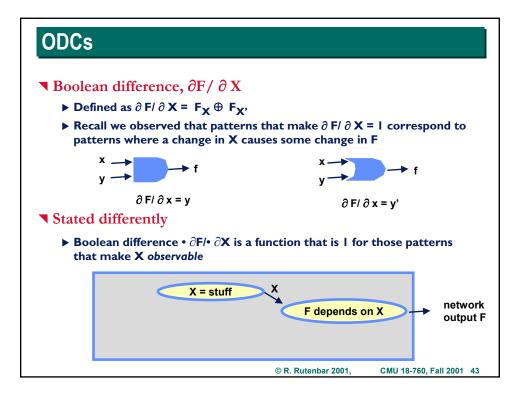

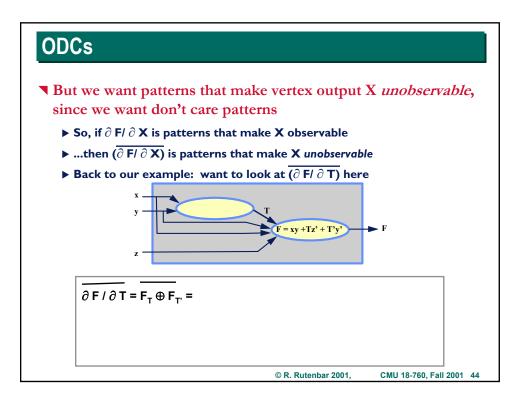

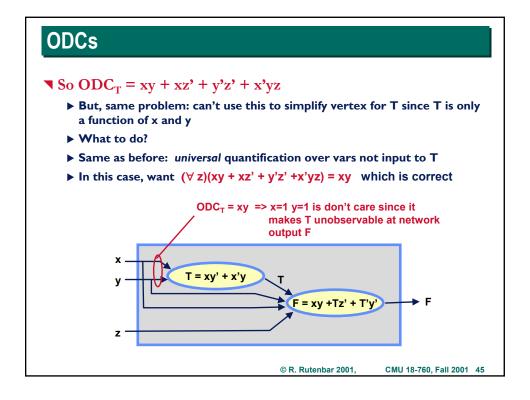

**Observability Don't Cares** ■ ODCs belong to *each* output of a vertex in network ▶ Patterns that will make this output not observable at network output ▶ "Not observable" means a change 0<->1 on this vertex output doesn't not change ANY network output, for this pattern New example Note--new example now... х T = xy' + x'yy/ F = xy +Tz' + T'y' Patterns that make F insensitive to T.... • Look at  $ODC_{T}$  for output wire of vertex T © R. Rutenbar 2001, CMU 18-760, Fall 2001 40