## 18-600 Foundations of Computer Systems

## Lecture 2: "Computer Systems: The Big Picture"

John P. Shen & Gregory Kesden August 30, 2017

Recommended Reference:

- Chapters 1 and 2 of Shen and Lipasti (SnL).

- Other Relevant References:

- "A Detailed Analysis of Contemporary ARM and x86 Architectures" by

- Emily Blem, Jaikrishnan Menon, and Karthikeyan Sankaralingam . (2013)

- "Amdahl's and Gustafson's Laws Revisited" by Andrzej Karbowski. (2008)

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

## 18-600 Foundations of Computer Systems

## Lecture 2: "Computer Systems: The Big Picture"

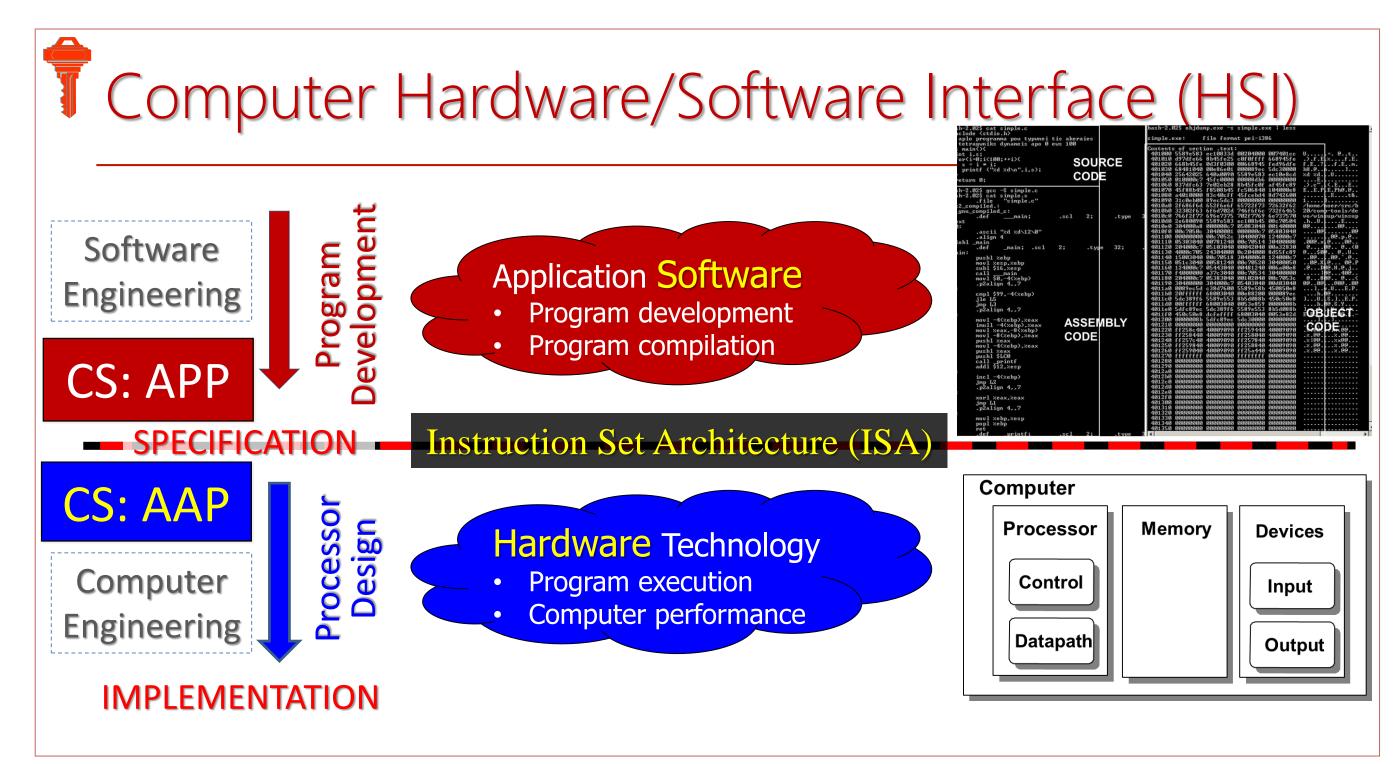

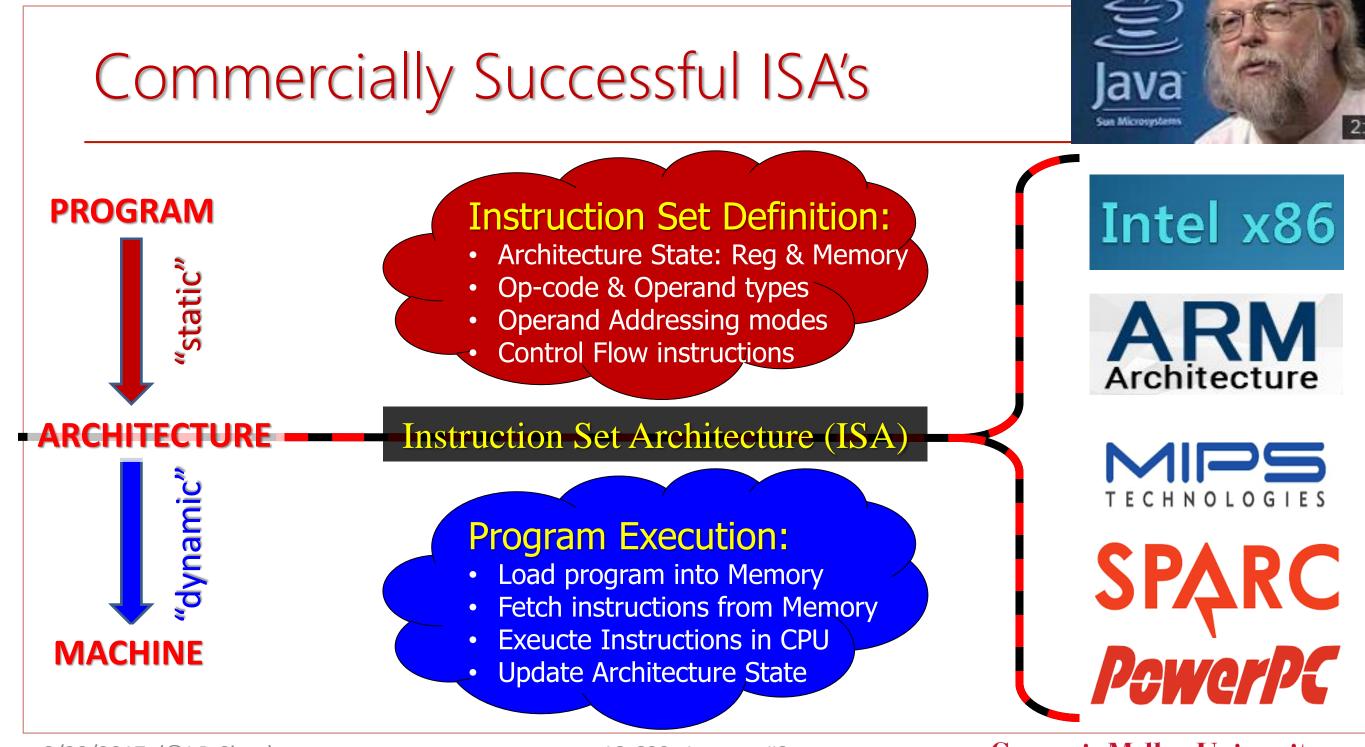

### 1. Instruction Set Architecture (ISA)

- a. Hardware / Software Interface (HSI)

- b. Dynamic / Static Interface (DSI)

- c. Instruction Set Architecture Design & Examples

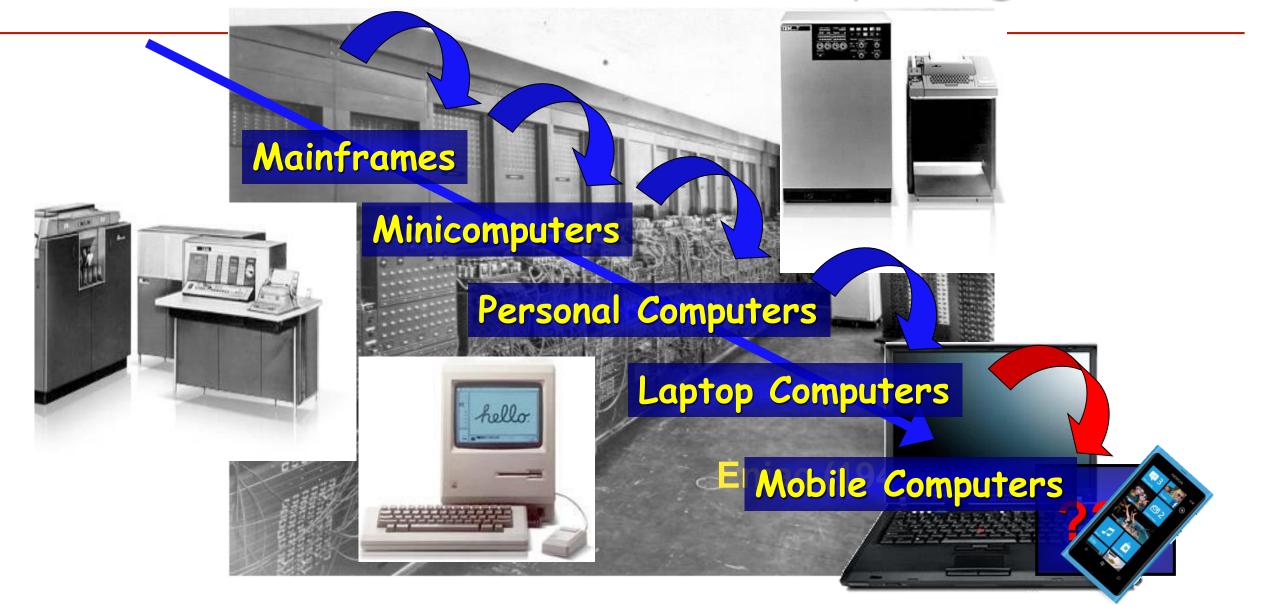

### 2. Historical Perspective on Computing

- a. Major Epochs of Modern Computers

- b. Computer Performance Iron Law (#1)

- 3. "Economics" of Computer Systems

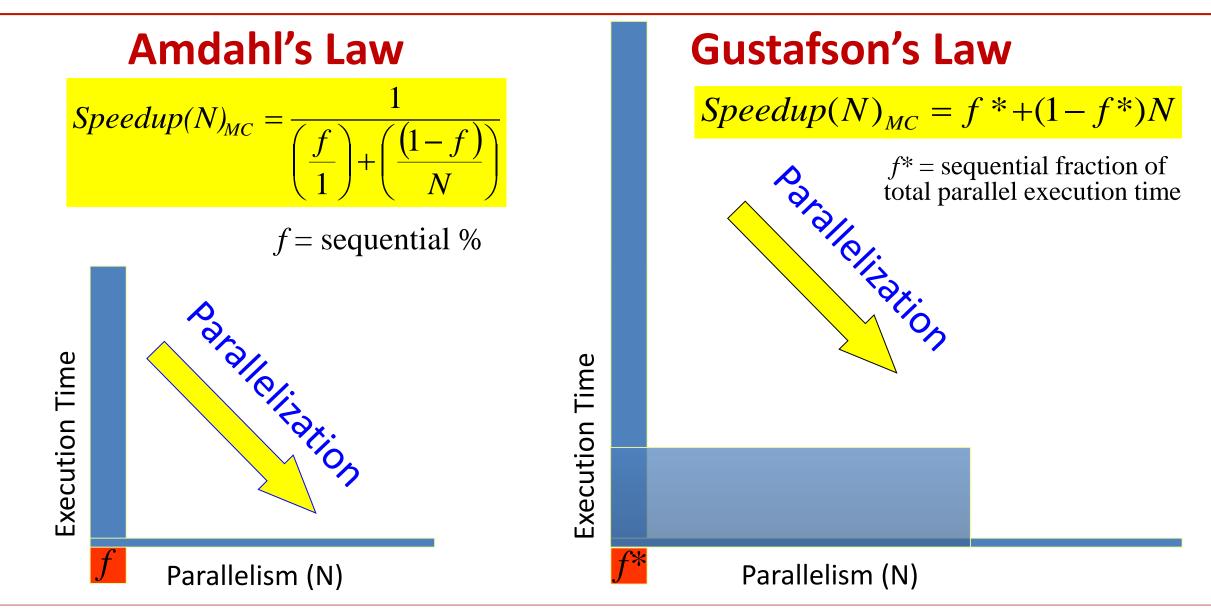

- a. Amdahl's Law and Gustafson's Law

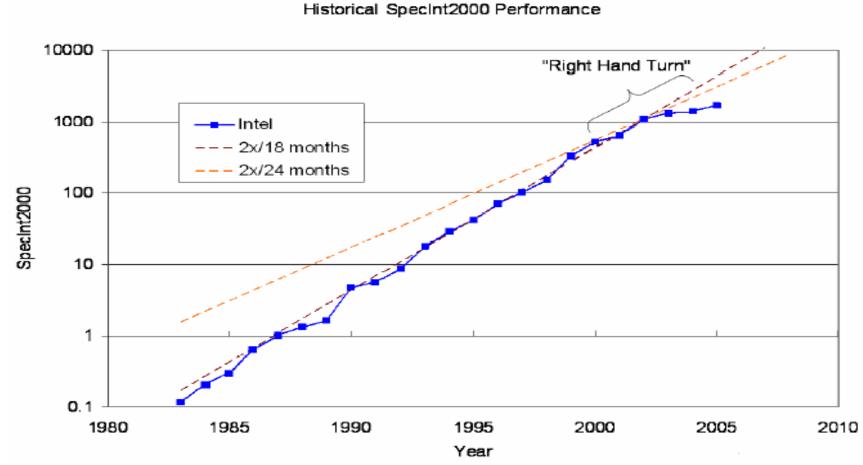

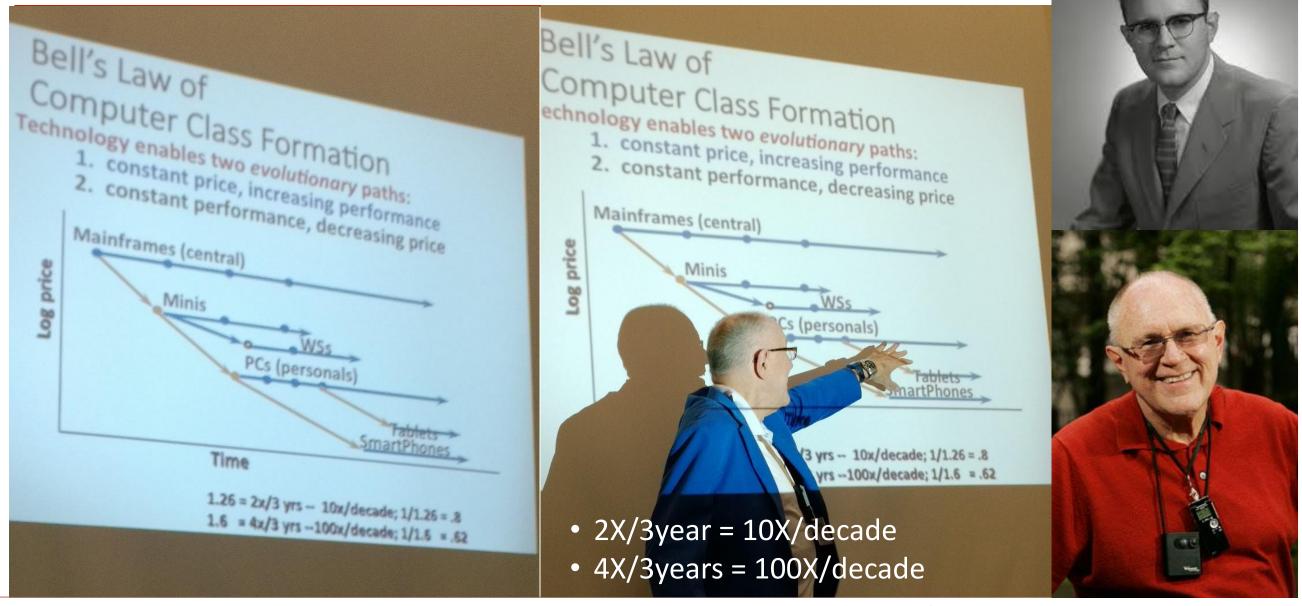

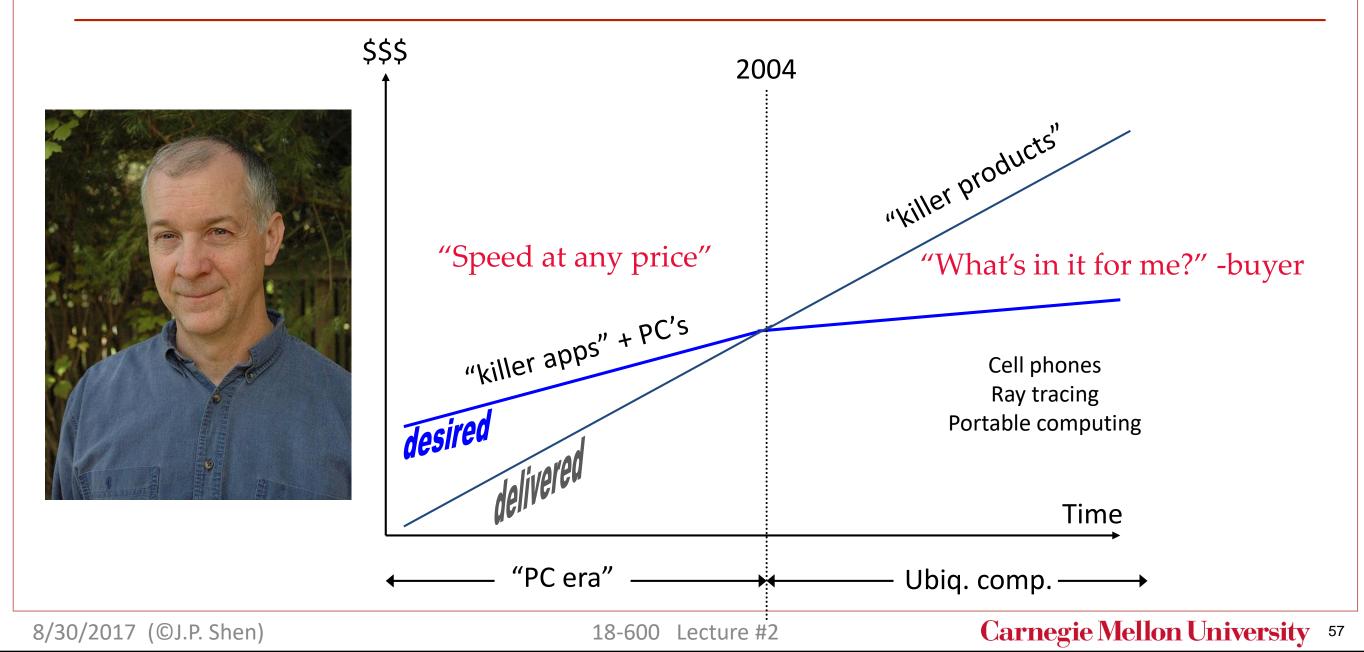

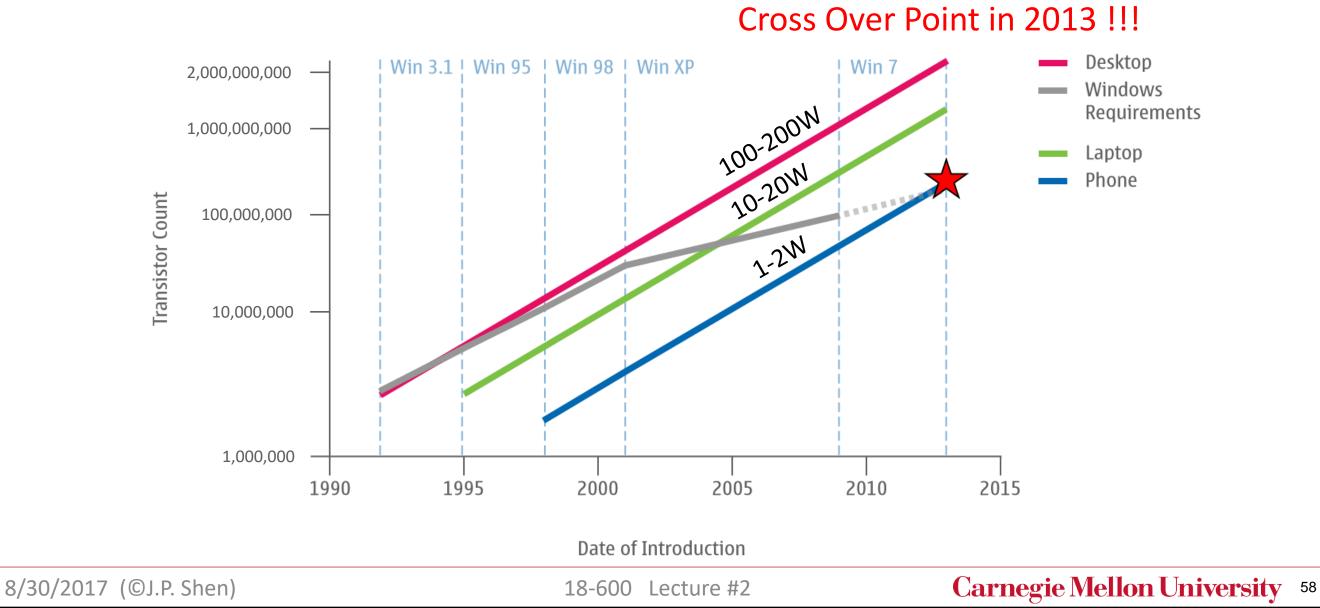

- b. Moore's Law and Bell's Law

18-600 Lecture #2

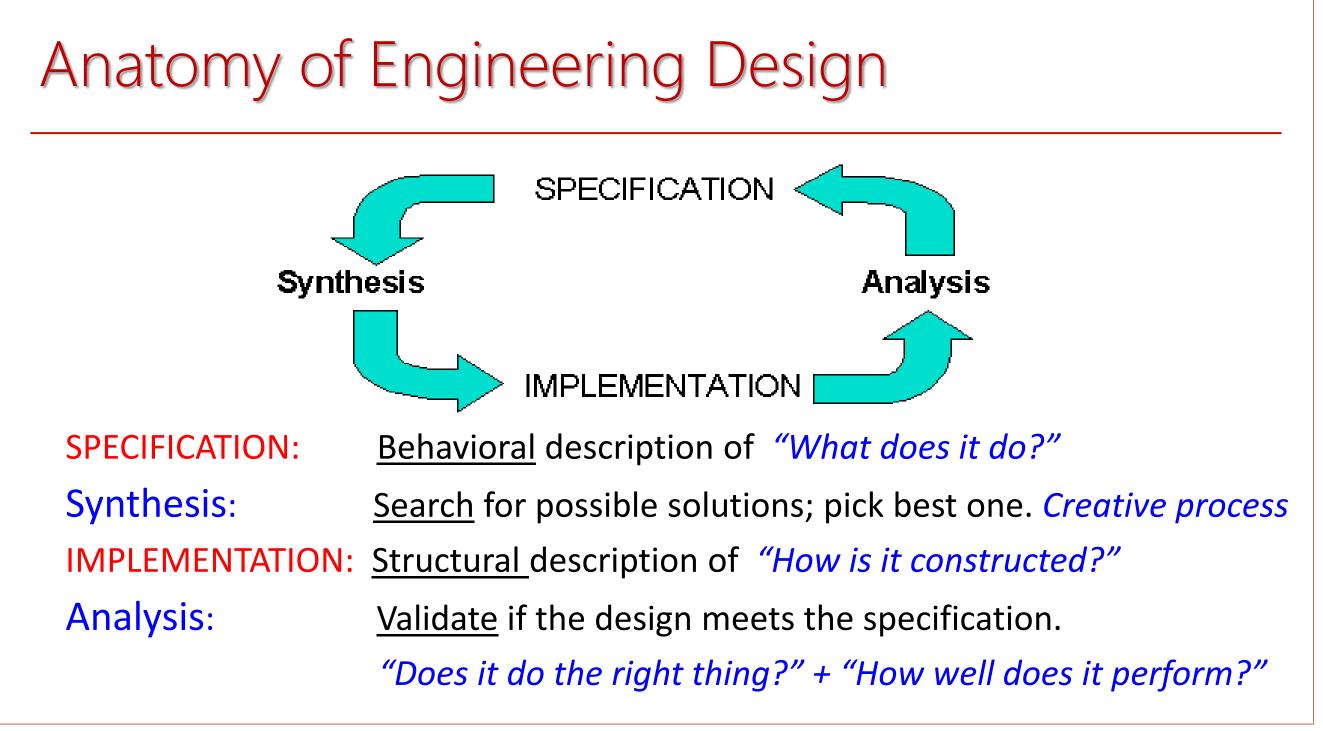

#### [Gerrit Blaauw & Fred Brooks, 1981]

## Instruction Set Processor Design

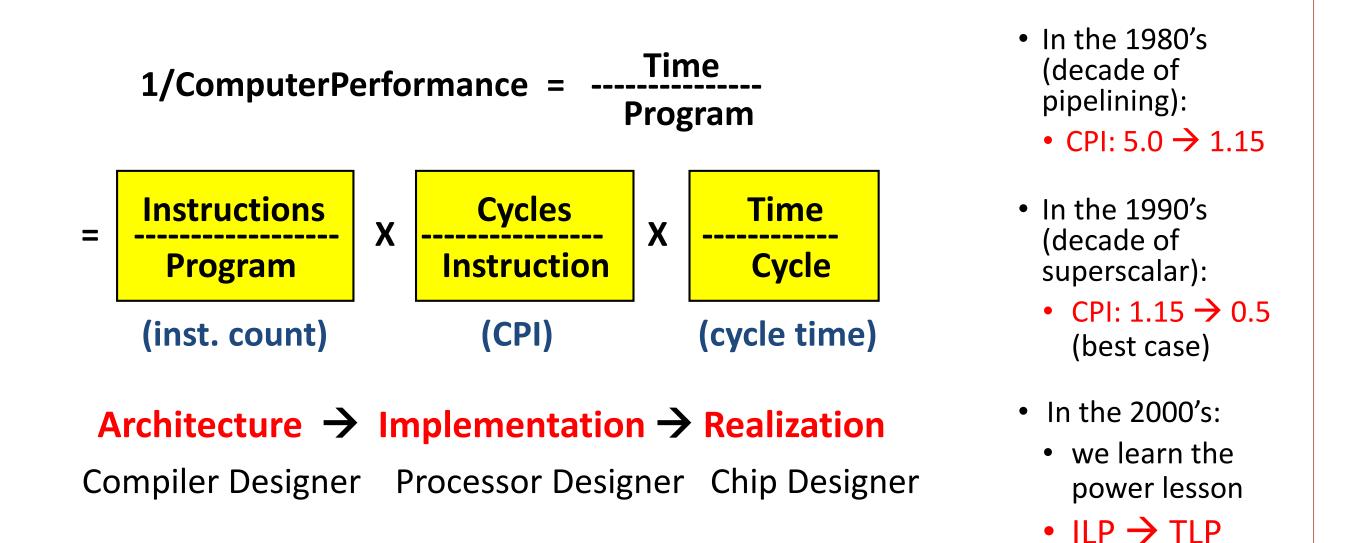

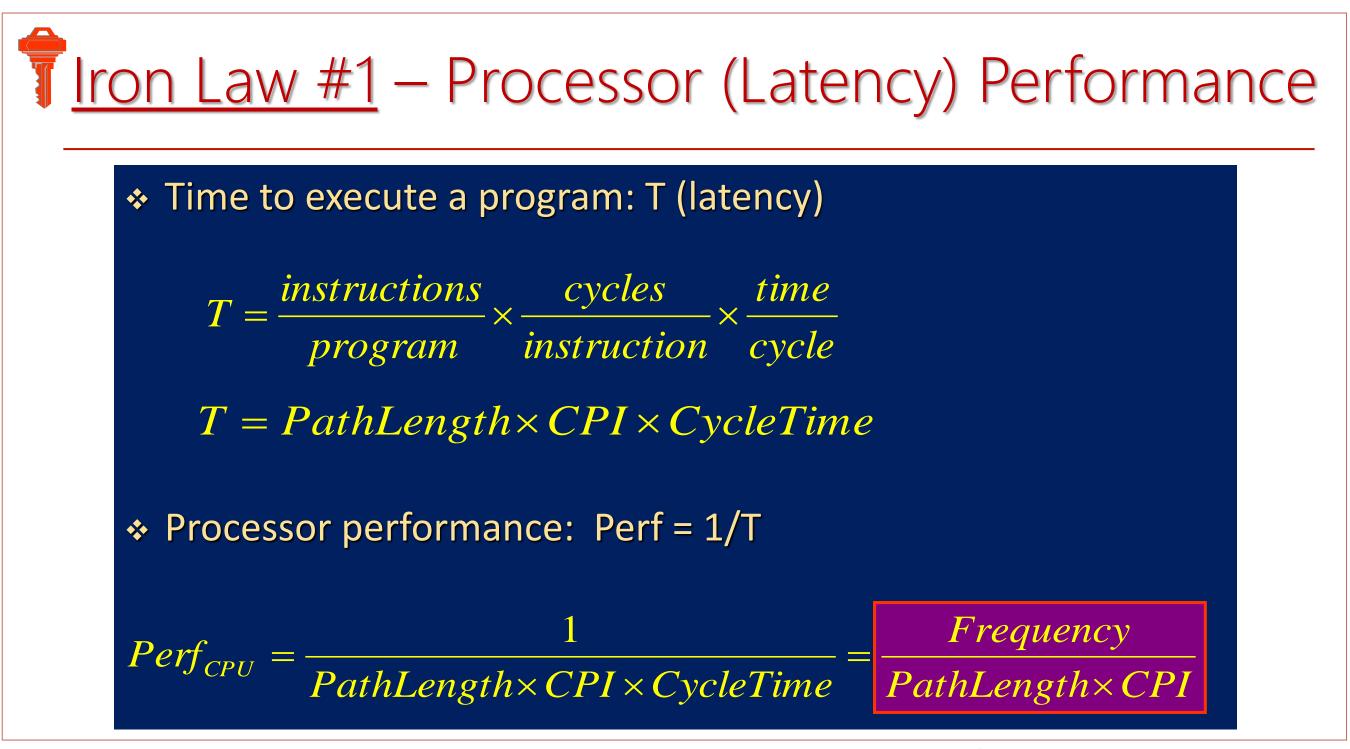

#### **ARCHITECTURE:** (ISA) <u>programmer/compiler view</u> = **SPECIFICATION**

- Functional programming model to application/system programmers

- Opcodes, addressing modes, architected registers, IEEE floating point

### **IMPLEMENTATION:** (µarchitecture) processor designer view

- Logical structure or organization that performs the ISA specification

- Pipelining, functional units, caches, physical registers, buses, branch predictors

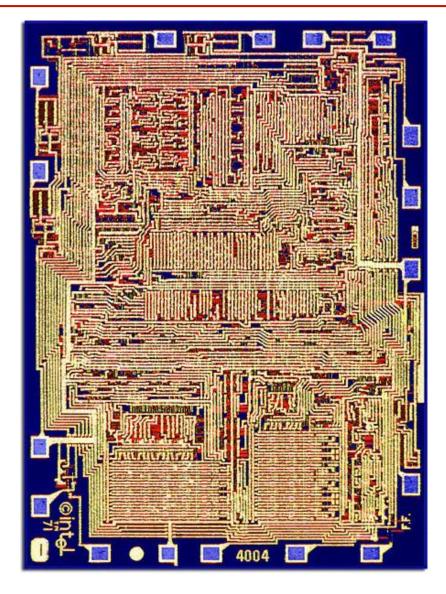

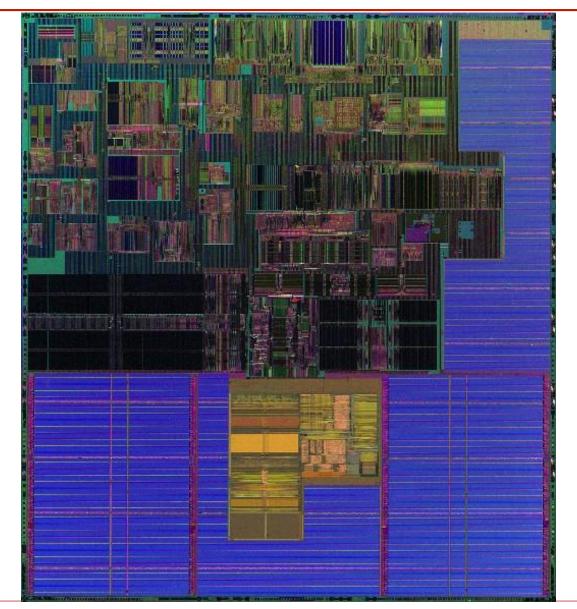

### **REALIZATION:** (Chip) <u>chip/system designer view</u>

- Physical structure that embodies the implementation

- Gates, cells, transistors, wires, dies, packaging

## Lecture 2: "Computer Systems: The Big Picture"

## 1. Instruction Set Architecture (ISA)

- a. Hardware / Software Interface (HSI)

- b. Dynamic / Static Interface (DSI)

- c. Instructure Set Architecture Design & Examples

Carnegie Mellon University 5

18-600 Lecture #2

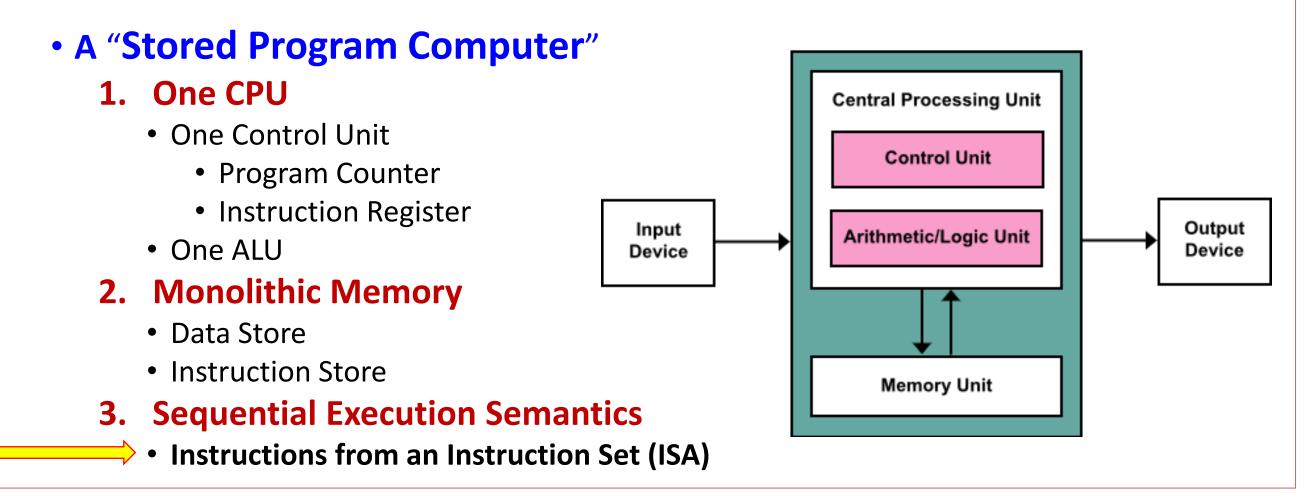

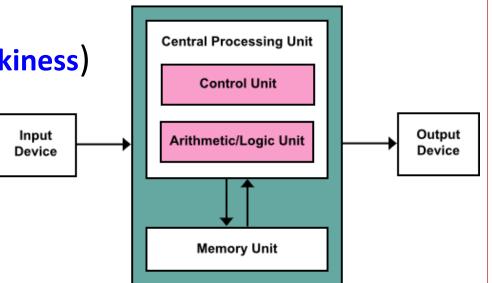

## The Von Neumann Stored Program Computer

• **The Classic Von Neumann Computation Model**: Proposed in 1945 by John Von Neumann and others (Alan Turing, J. Presper Eckert and John Mauchly).

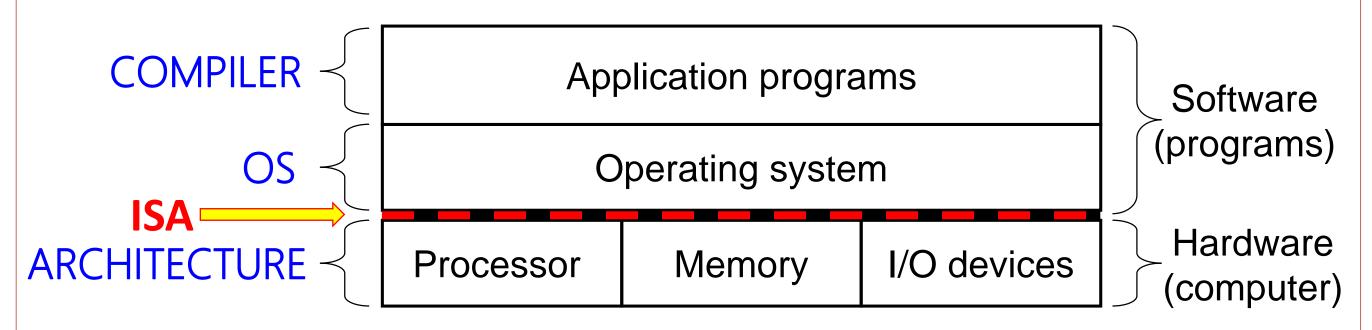

# Anatomy of a Computer System: (ISA)

### > What is a Computer System?

- Software + Hardware

- ✤ Programs + Computer → [Application program + OS] + Computer

- Programming Languages + Operating Systems + Computer Architecture

8/30/2017 (©J.P. Shen)

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

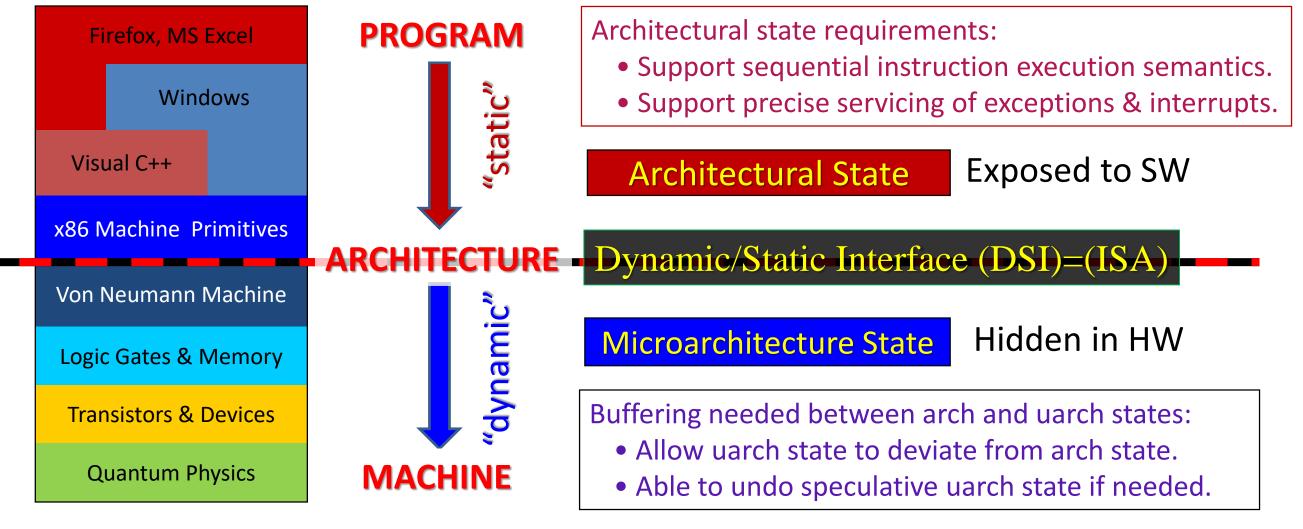

# Computer Dynamic/Static Interface (DSI)

DSI = ISA = a contract between the program and the machine.

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

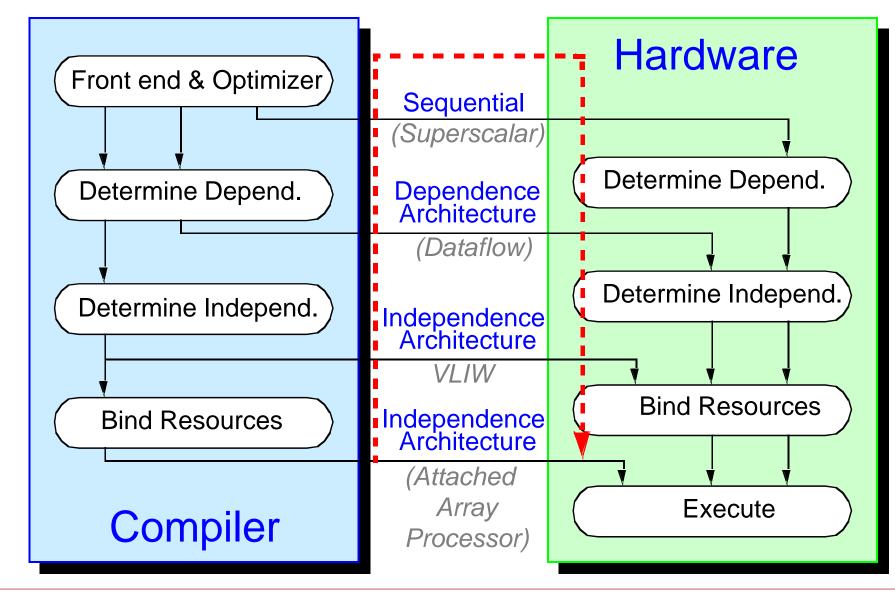

#### [B. Rau & J. Fisher, 1993]

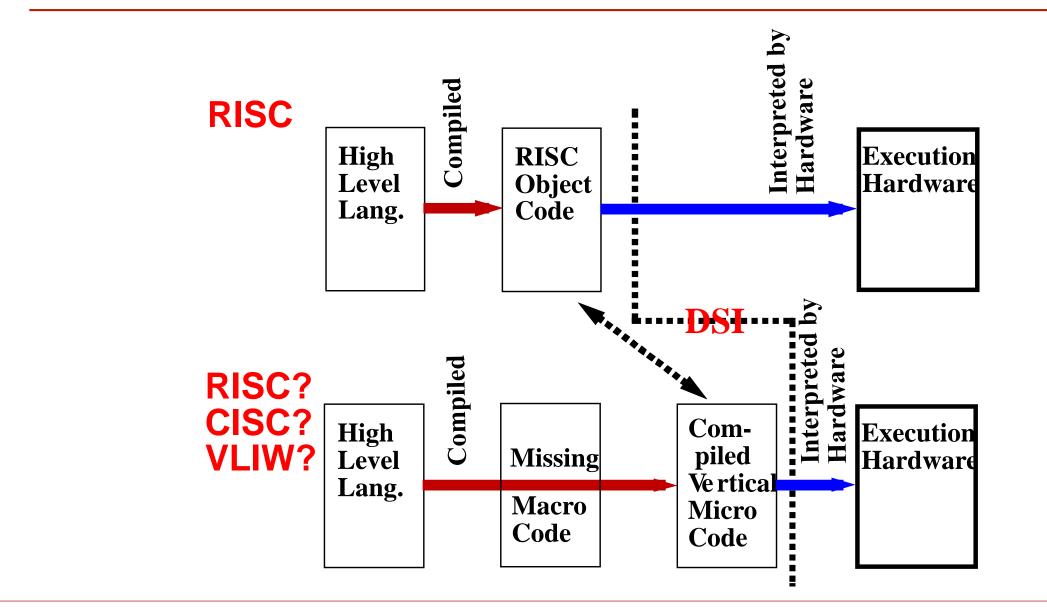

## Dynamic/Static Design Space: DSI Placement

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

Carnegie Mellon University <sup>10</sup>

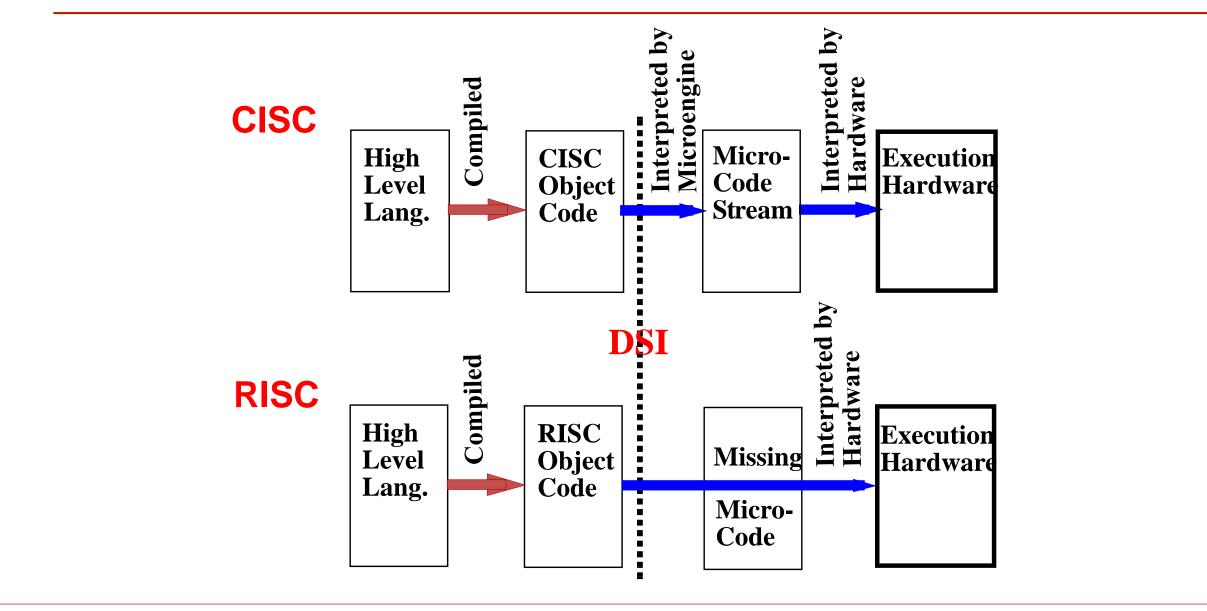

#### [Josh Fisher, HP]

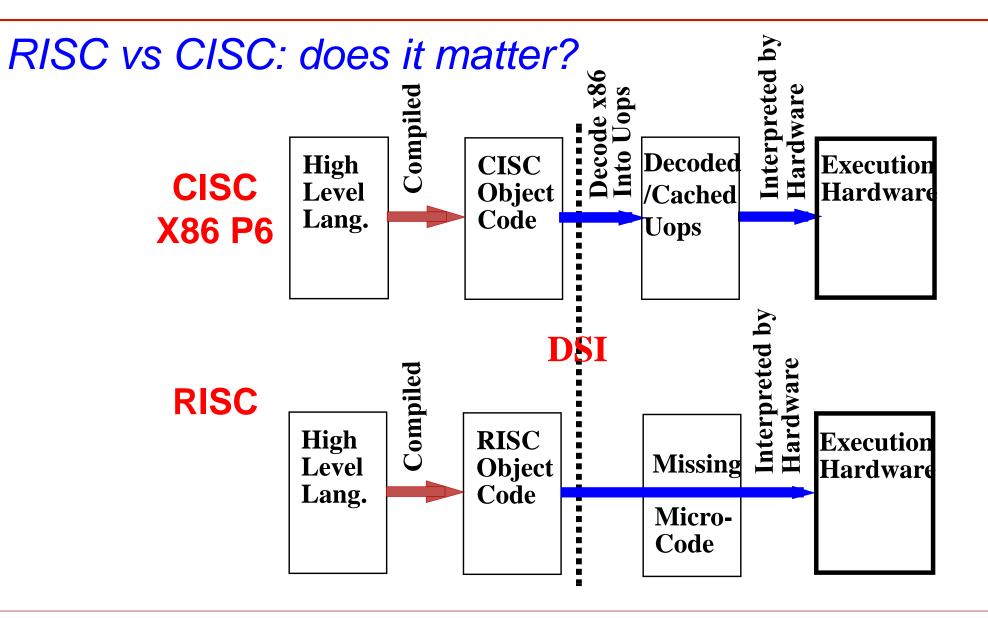

## RISC vs. CISC Transition from CISC to RISC:

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

## Another way to view RISC

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

#### Carnegie Mellon University <sup>12</sup>

## All x86 processors since Pentium Pro (P6)

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

#### Carnegie Mellon University <sup>13</sup>

## Instruction Set Architecture (ISA) Design

### Instruction Types

- Operation Specifiers (OpCodes)

- Operand Specifiers

- Addressing Modes

- Exceptions Handling

### Design Styles: Placement of DSI

- RISC vs. CISC

- Historically Important ISAs

## Instruction Types and OpCodes

#### FOUR CLASSES OF INSTRUCTIONS ARE CONSIDERED:

- INTEGER ARITHMETIC/LOGIC INSTRUCTIONS

- ADD, SUB, MULT

- ADDU, SUBU, MULTU

- OR, AND, NOR, NAND

- FLOATING POINT INSTRUCTIONS

- FADD, FMUL, FDIV

- COMPLEX ARITHMETIC

- MEMORY TRANSFER INSTRUCTIONS

- LOADS AND STORES

- TEST AND SET, AND SWAP

- MAY APPLY TO VARIOUS OPERAND SIZES

#### CONTROL FLOW INSTRUCTIONS

- BRANCHES ARE CONDITIONAL

- CONDITION MAY BE CONDITION BITS (ZCVXN)

- CONDITION MAY TEST THE VALUE OF A REGISTER (SET BY SLT INSTRUCTION)

- CONDITION MAY BE COMPUTED IN THE BRANCH INSTRUCTION ITSELF

- JUMPS ARE UNCONDITIONAL WITH ABSOLUTE ADDRESS OR ADDRESS IN REGISTER

- JAL (JUMP AND LINK) NEEDED FOR PROCEDURES

## CPU Operands

- INCLUDE: ACCUMULATORS, EVALUATION STACKS, REGISTERS, AND IMMEDIATE VALUES

- ACCUMULATORS:

- ADDA <mem\_address>

- MOVA <mem\_address>

#### • STACK

- PUSH <mem\_address>

- ADD

- POP <mem\_address>

#### REGISTERS

- LW R1, <memory-address>

- SW R1, <memory\_address>

- ADD R2, <memory\_address>

- ADD R1,R2,R4

- LOAD/STORE ISAs

- MANAGEMENT BY THE COMPILER: REGISTER SPILL/FILL

#### • IMMEDIATE

• ADDI R1,R2,#5

## Memory Operands

#### OPERAND ALIGNEMENT

- BYTE-ADDRESSABLE MACHINES

- OPERANDS OF SIZE S MUST BE STORED AT AN ADDRESS THAT IS MULTPIPLE OF S

- BYTES ARE ALWAYS ALIGNED

- HALF WORDS (16BITS) ALIGNED AT 0, 2, 4, 6

- WORDS (32 BITS) ARE ALIGNED AT 0, 4, 8, 12, 16,...

- DOUBLE WORDS (64 BITS) ARE ALIGNED AT 0, 8, 16,...

- COMPILER IS RESPONSIBLE FOR ALIGNING OPERANDS. HARDWARE CHECKS AND TRAPS IF

MISALIGNED

- OPCODE INDICATES SIZE (ALSO: TAGS IN MEMORY)

#### • LITTLE vs. BIG ENDIAN

- BIG ENDIAN: MSB IS STORED AT ADDRESS XXXXXX00

- LITTLE ENDIAN: LSB IS STORED AT ADDRESS XXXXXX00

- PORTABILITY PROBLEMS, CONFIGURABLE ENDIANNESS

## Addressing Modes

| MODE               | EXAMPLE         | MEANING                                     |

|--------------------|-----------------|---------------------------------------------|

| REGISTER           | ADD R4,R3       | reg[R4] <- reg[R4] +reg[R3]                 |

| IMMEDIATE          | ADD R4, #3      | reg[R4] <- reg[R4] + 3                      |

| DISPLACEMENT       | ADD R4, 100(R1) | reg[R4] <- reg[R4] + Mem[100 + reg[R1]]     |

| REGISTER INDIRECT  | ADD R4, (R1)    | reg[R4] <- reg[R4] + Mem[reg[R1]]           |

| INDEXED            | ADD R3, (R1+R2) | reg[R3] <- reg[R3] + Mem[reg[R1] + reg[R2]] |

| DIRECT OR ABSOLUTE | ADD R1, (1001)  | reg[R1] <- reg[R1] + Mem[1001]              |

| MEMORY INDIRECT    | ADD R1, @R3     | reg[R1] <- reg[R1] + Mem[Mem[Reg[3]]]       |

| POST INCREMENT     | ADD R1, (R2)+   | ADD R1, (R2) then R2 <- R2+d                |

| PREDECREMENT       | ADD R1, -(R2)   | R2 <- R2-d then ADD R1, (R2)                |

| PC-RELATIVE        | BEZ R1, 100     | if R1==0, PC <- PC+100                      |

| PC-RELATIVE        | JUMP 200        | Concatenate bits of PC and offset           |

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

## Exceptions and Interrupts

- EVENTS TRIGGERED BY PROGRAM and HARDWARE, FORCING THE PROCESSOR TO EXECUTE A HANDLER

- INCLUDES EXCEPTIONS AND INTERRUPTS

- EXCEPTION & INTERRUP EXAMPLES:

- I/O DEVICE INTERRUPTS

- OPERATING SYSTEM CALLS

- INSTRUCTION TRACING AND BREAKPOINTS

- INTEGER OR FLOATING-POINT ARITHMETIC EXCEPTIONS

- PAGE FAULTS

- MISALIGNED MEMORY ACCESSES

- MEMORY PROTECTION VIOLATIONS

- UNDEFINED INSTRUCTIONS

- HARDWARE FAILURE/ALARMS

- POWER FAILURES

- **PRECISE EXCEPTIONS:**

- SYNCHRONIZED WITH AN INSTRUCTION

- MUST RESUME EXECUTION AFTER HANDLER

- SAVE THE PROCESS STATE AT THE FAULTING INSTRUCTION

- OFTEN DIFFICULT IN ARCHITECTURES WHERE MULTIPLE INSTRUCTIONS EXECUTE

## Historically Important ISAs & Implementations

| ISA           | Company          | Implementations | Туре                |

|---------------|------------------|-----------------|---------------------|

| System 370    | IBM              | IBM 370/3081    | CISCLegacy          |

| x86           | Intel/AMD        | Many, many,     | CISC-Legacy         |

| Motorola68000 | Motorola         | Motorola 68020  | CISC-Legacy         |

| Sun SPARC     | Sun Microsystems | SPARC T2        | RISC                |

| PowerPC       | IBM/Motorola     | PowerPC-6       | RISC                |

| Alpha         | DEC/Compaq/HP    | Alpha 21264     | <b>RISC-Retired</b> |

| MIPS          | MIPS/SGI         | MIPS10000       | RISC                |

| IA-64         | Intel            | Itanium-2       | <b>RISC-Retired</b> |

| ARM           | ARM/QC/Samsung   | Many, many,     | RISC                |

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

Carnegie Mellon University <sup>20</sup>

Table 5-1. Instruction Groups in Intel 64 and IA-32 Processors

| Instruction Set<br>Architecture          | Intel 64 and IA-32 Processor Support                                                                                                                                                                                                                                      |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                          | All Intel 64 and IA-32 processors.                                                                                                                                                                                                                                        |

| x87 FPU                                  | Intel486, Pentium, Pentium with MMX Technology, Celeron, Pentium Pro, Pentium II, Pentium II Xeon,<br>Pentium III, Pentium III Xeon, Pentium 4, Intel Xeon processors, Pentium M, Intel Core Solo, Intel Core Duo,<br>Intel Core 2 Duo processors, Intel Atom processors. |

| x87 FPU and SIMD State<br>Management     | Pentium II, Pentium II Xeon, Pentium III, Pentium III Xeon, Pentium 4, Intel Xeon processors, Pentium M,<br>Intel Core Solo, Intel Core Duo, Intel Core 2 Duo processors, Intel Atom processors.                                                                          |

| MMX Technology                           | Pentium with MMX Technology, Celeron, Pentium II, Pentium II Xeon, Pentium III, Pentium III Xeon, Pentium 4, Intel Xeon processors, Pentium M, Intel Core Solo, Intel Core Duo, Intel Core 2 Duo processors, Intel Atom processors.                                       |

| SSE Extensions                           | Pentium III, Pentium III Xeon, Pentium 4, Intel Xeon processors, Pentium M, Intel Core Solo, Intel Core Duo,<br>Intel Core 2 Duo processors, Intel Atom processors.                                                                                                       |

| SSE2 Extensions                          | Pentium 4, Intel Xeon processors, Pentium M, Intel Core Solo, Intel Core Duo, Intel Core 2 Duo processors,<br>Intel Atom processors.                                                                                                                                      |

| SSE3 Extensions                          | Pentium 4 supporting HT Technology (built on 90nm process technology), Intel Core Solo, Intel Core Duo,<br>Intel Core 2 Duo processors, Intel Xeon processor 3xxxx, 5xxx, 7xxx Series, Intel Atom processors.                                                             |

| SSSE3 Extensions                         | Intel Xeon processor 3xxx, 5100, 5200, 5300, 5400, 5500, 5600, 7300, 7400, 7500 series, Intel Core 2<br>Extreme processors QX6000 series, Intel Core 2 Duo, Intel Core 2 Quad processors, Intel Pentium Dual-Core<br>processors, Intel Atom processors.                   |

| IA-32e mode: 64-bit<br>mode instructions | Intel 64 processors.                                                                                                                                                                                                                                                      |

| System Instructions                      | Intel 64 and IA-32 processors.                                                                                                                                                                                                                                            |

| VMX Instructions                         | Intel 64 and IA-32 processors supporting Intel Virtualization Technology.                                                                                                                                                                                                 |

| SMX Instructions                         | Intel Core 2 Duo processor E6x50, E8xxx; Intel Core 2 Quad processor Q9xxx.                                                                                                                                                                                               |

8/30/2017 (©J.P. Shen)

#### Carnegie Mellon University <sup>21</sup>

#### Table 5-2. Recent Instruction Set Extensions Introduction in Intel 64 and IA-32 Processors

| Instruction Set<br>Architecture          | Processor Generation Introduction                                                                                                                                                                                     |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSE4.1 Extensions                        | Intel Xeon processor 3100, 3300, 5200, 5400, 7400, 7500 series, Intel Core 2 Extreme processors<br>QX9000 series, Intel Core 2 Quad processor Q9000 series, Intel Core 2 Duo processors 8000 series, T9000<br>series. |

| SSE4.2 Extensions,<br>CRC32, POPCNT      | Intel Core i7 965 processor, Intel Xeon processors X3400, X3500, X5500, X6500, X7500 series.                                                                                                                          |

| AESNI, PCLMULQDQ                         | InteL Xeon processor E7 series, Intel Xeon processors X3600, X5600, Intel Core i7 980X processor; Use CPUID to verify presence of AESNI and PCLMULQDQ across Intel Core processor families.                           |

| Intel AVX                                | Intel Xeon processor E3 and E5 families; 2nd Generation Intel Core i7, i5, i3 processor 2xxx families.                                                                                                                |

| F16C, RDRAND, FS/GS<br>base access       | 3rd Generation Intel Core processors, Intel Xeon processor E3-1200 v2 product family, Next Generation<br>Intel Xeon processors, Intel Xeon processor E5 v2 and E7 v2 families.                                        |

| FMA, AVX2, BMI1, BMI2,<br>INVPCID        | Intel Xeon processor E3-1200 v3 product family; 4th Generation Intel Core processor family.                                                                                                                           |

| TSX                                      | Intel Xeon processor E7 v3 product family.                                                                                                                                                                            |

| ADX, RDSEED, CLAC,<br>STAC               | Intel Core M processor family; 5th Generation Intel Core processor family.                                                                                                                                            |

| CLFLUSHOPT, XSAVEC,<br>XSAVES, MPX, SGX1 | 6th Generation Intel Core processor family.                                                                                                                                                                           |

#### 5.1.1 Data Transfer Instructions

The data transfer instructions move data between memory and the general-purpose and segment registers. They also perform specific operations such as conditional moves, stack access, and data conversion.

| CMOVE/CMOVZConditional move if equal/Conditional move if not zero.CMOVNE/CMOVNZConditional move if not equal/Conditional move if not zero.CMOVA/CMOVNBEConditional move if above/Conditional move if not below or equal.CMOVA/CMOVNAEConditional move if below/Conditional move if not below.CMOVBE/CMOVNAEConditional move if below or equal/Conditional move if not below.CMOVE/CMOVNAEConditional move if greater/Conditional move if not below.CMOVE/CMOVNAEConditional move if greater/Conditional move if not below.CMOVE/CMOVNAEConditional move if greater/Conditional move if not less or equal.CMOVE/CMOVNGEConditional move if greater/Conditional move if not greater.CMOVL/CMOVNGEConditional move if less/Conditional move if not greater.CMOVCConditional move if less or equal/Conditional move if not greater.CMOVCConditional move if out carry.CMOVCConditional move if out fort carry.CMOVOConditional move if fort sign (negative).CMOVSConditional move if fort sign (non-negative).CMOVP/CMOVPEConditional move if fort parity/Conditional move if parity even.CMOVP/CMOVPEConditional move if not parity/Conditional move if parity odd.XCHGExchange.SWAPByte swap.XADDExchange and add.CMPXCHG8BCompare and exchange.CMPXCHG8BCompare and exchange.POPPop off of stack.POPPop off of stack.POPPop off of stack.POP/CPOPADPop general-purpose registers onto stack. </th <th>MOV</th> <th>Move data between general-purpose registers; move data between memory and general-<br/>purpose or segment registers; move immediates to general-purpose registers.</th> | MOV           | Move data between general-purpose registers; move data between memory and general-<br>purpose or segment registers; move immediates to general-purpose registers. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMOVA/CMOVNBEConditional move if above/Conditional move if not below or equal.CMOVAE/CMOVNBEConditional move if above or equal/Conditional move if not below.CMOVB/CMOVNAEConditional move if below/Conditional move if not above or equal.CMOVB/CMOVNAEConditional move if below or equal/Conditional move if not above.CMOVG/CMOVNLEConditional move if greater or equal/Conditional move if not less or equal.CMOVGE/CMOVNLEConditional move if greater or equal/Conditional move if not less.CMOVL/CMOVNGEConditional move if greater or equal/Conditional move if not greater.CMOVLE/CMOVNGConditional move if less/Conditional move if not greater.CMOVCConditional move if carry.CMOVOConditional move if overflow.CMOVNOConditional move if overflow.CMOVNOConditional move if not sign (non-negative).CMOVNSConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPEConditional move if parity/Conditional move if parity odd.CMOVNSConditional move if parity/Conditional move if parity odd.CMOVNP/CMOVPEConditional move if parity/Conditional move if parity odd.CMOVNP/CMOVPDConditional move if parity/Conditional move if parity odd.CMOVNP/CMOVPDConditional move if parity/Conditional move if parity odd.CMOVNP/CMOVPDCompare and exchange.CMOVNP/CMOVPDCompare and exchange.CMOVNCCompare and exchange.CMOVNCCompare and exchange.CMOVNCCompare and exchange.CMPXCHGBBCompare and exchange 8 bytes. <td< td=""><td>CMOVE/CMOVZ</td><td>Conditional move if equal/Conditional move if zero.</td></td<>                                                 | CMOVE/CMOVZ   | Conditional move if equal/Conditional move if zero.                                                                                                               |

| CMOVAE/CMOVNBConditional move if above or equal/Conditional move if not below.CMOVB/CMOVNAEConditional move if below/Conditional move if not above or equal.CMOVBE/CMOVNAConditional move if below or equal/Conditional move if not above.CMOVG/CMOVNLEConditional move if greater/Conditional move if not less or equal.CMOVGE/CMOVNLConditional move if greater or equal/Conditional move if not less.CMOVLE/CMOVNGEConditional move if greater or equal/Conditional move if not greater.CMOVLE/CMOVNGEConditional move if less or equal/Conditional move if not greater.CMOVCConditional move if carry.CMOVCConditional move if or carry.CMOVOConditional move if not sign (negative).CMOVNOConditional move if sign (negative).CMOVNSConditional move if not sign (non-negative).CMOVNP/CMOVPEConditional move if not parity/Conditional move if parity even.CMOVNP/CMOVPDConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGSBCompare and exchange.CMPXCHGSBCompare and exchange.CMPXCHGSBCompare and exchange.POPPop off of stack.POPPop off of stack.POPA/POPADPop general-purpose registers from stack.POPA/POPADPop general-purpose registers from stack.POPA/POPADPop general-purpose registers from stack.CMDCDQConvert word to doubleword/convert doubleword to quadword.CMDCDQConvert w                                                                                                                                                                                                                   | CMOVNE/CMOVNZ | Conditional move if not equal/Conditional move if not zero.                                                                                                       |

| CMOVB/CMOVNAEConditional move if below/Conditional move if not above or equal.CMOVBE/CMOVNAConditional move if below or equal/Conditional move if not above.CMOVG/CMOVNLEConditional move if greater/Conditional move if not less or equal.CMOVG/CMOVNLEConditional move if greater or equal/Conditional move if not less.CMOVL/CMOVNGEConditional move if greater or equal/Conditional move if not greater or equal.CMOVL/CMOVNGEConditional move if less or equal/Conditional move if not greater.CMOVLE/CMOVNGConditional move if carry.CMOVCConditional move if not carry.CMOVOConditional move if not overflow.CMOVNOConditional move if not sign (non-negative).CMOVNSConditional move if not parity/Conditional move if parity even.CMOVNP/CMOVPEConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHG8BCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.POPA/POPADPop general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CVMD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                     | CMOVA/CMOVNBE | Conditional move if above/Conditional move if not below or equal.                                                                                                 |

| CMOVBE/CMOVNAConditional move if below or equal/Conditional move if not above.CMOVG/CMOVNLEConditional move if greater/Conditional move if not less or equal.CMOVE/CMOVNLEConditional move if greater or equal/Conditional move if not less.CMOVL/CMOVNGEConditional move if greater or equal/Conditional move if not greater or equal.CMOVL/CMOVNGEConditional move if less or equal/Conditional move if not greater.CMOVLE/CMOVNGConditional move if less or equal/Conditional move if not greater.CMOVCConditional move if ot carry.CMOVNCConditional move if not overflow.CMOVNOConditional move if not overflow.CMOVNSConditional move if not sign (non-negative).CMOVNSConditional move if not parity/Conditional move if parity even.CMOVNP/CMOVPEConditional move if not parity/Conditional move if parity odd.XCHGExchange.SWAPByte swap.XADDExchange and add.CMPXCHGCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.POPA/POPADPog general-purpose registers from stack.POPA/POPADPog general-purpose registers from stack.POVD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                       | CMOVAE/CMOVNB | Conditional move if above or equal/Conditional move if not below.                                                                                                 |

| CMOVG/CMOVNLEConditional move if greater/Conditional move if not less or equal.CMOVGE/CMOVNLConditional move if greater or equal/Conditional move if not less.CMOVL/CMOVNGEConditional move if less or equal/Conditional move if not greater or equal.CMOVLE/CMOVNGConditional move if less or equal/Conditional move if not greater.CMOVCConditional move if oct greater.CMOVCConditional move if not carry.CMOVOConditional move if not overflow.CMOVOConditional move if not overflow.CMOVSConditional move if not sign (negative).CMOVNSConditional move if not sign (non-negative).CMOVP/CMOVPEConditional move if not parity/Conditional move if parity even.CMOVNP/CMOVPEConditional move if not parity/Conditional move if parity even.CMOVNP/CMOVPOConditional move if not parity/Conditional move if parity even.CMOVNP/CMOVPOConditional move if not parity/Conditional move if parity even.CMOVNP/CMOVPDConditional move if not parity/Conditional move if parity even.CMOVNP/CMOVPDConditional move if not parity/Conditional move if parity even.CMOVNP/CMOVPDCompare and exchange.CMPXCHGCompare and exchange.CMPXCHGSBCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.POPA/POPADPop general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CWD/CDQConvert word to doubleword to double                                                                                                                                                             | CMOVB/CMOVNAE | Conditional move if below/Conditional move if not above or equal.                                                                                                 |

| CMOVGE/CMOVNLConditional move if greater or equal/Conditional move if not less.CMOVL/CMOVNGEConditional move if less/Conditional move if not greater or equal.CMOVLE/CMOVNGConditional move if less or equal/Conditional move if not greater.CMOVCConditional move if carry.CMOVNCConditional move if not carry.CMOVOConditional move if not overflow.CMOVNOConditional move if not overflow.CMOVNOConditional move if not overflow.CMOVNSConditional move if not sign (negative).CMOVNSConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPEConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGSCompare and exchange.CMPXCHGSBCompare and exchange.PUSHPush onto stack.POPPop off of stack.POPA/POPADPog general-purpose registers onto stack.POPA/POPADPog general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CWD/CDDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CMOVBE/CMOVNA | Conditional move if below or equal/Conditional move if not above.                                                                                                 |

| CMOVL/CMOVNGEConditional move if less/Conditional move if not greater or equal.CMOVLE/CMOVNGConditional move if less or equal/Conditional move if not greater.CMOVCConditional move if ot carry.CMOVNCConditional move if not carry.CMOVOConditional move if overflow.CMOVNOConditional move if not overflow.CMOVSConditional move if not overflow.CMOVSConditional move if not sign (non-negative).CMOVNSConditional move if parity/Conditional move if parity even.CMOVP/CMOVPEConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGSBCompare and exchange.PUSHPush onto stack.POPPop off of stack.POPPop off of stack.POPA/POPADPop general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CMOVG/CMOVNLE | Conditional move if greater/Conditional move if not less or equal.                                                                                                |

| CMOVLE/CMOVNGConditional move if less or equal/Conditional move if not greater.CMOVCConditional move if carry.CMOVNCConditional move if not carry.CMOVOConditional move if overflow.CMOVOConditional move if not overflow.CMOVSConditional move if sign (negative).CMOVSConditional move if sign (non-negative).CMOVP/CMOVPEConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPEConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGSBCompare and exchange.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CMOVGE/CMOVNL | Conditional move if greater or equal/Conditional move if not less.                                                                                                |

| CMOVCConditional move if carry.CMOVNCConditional move if not carry.CMOVOConditional move if overflow.CMOVOConditional move if not overflow.CMOVSConditional move if sign (negative).CMOVSConditional move if not sign (non-negative).CMOVP/CMOVPEConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPOConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGCompare and exchange.CMPXCHGBBCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.POPA/POPADPop general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CMOVL/CMOVNGE | Conditional move if less/Conditional move if not greater or equal.                                                                                                |

| CMOVNCConditional move if not carry.CMOVOConditional move if overflow.CMOVNOConditional move if not overflow.CMOVSConditional move if sign (negative).CMOVSConditional move if sign (non-negative).CMOVNSConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPEConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGCompare and exchange.CMPXCHGBBCompare and exchange.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CMOVLE/CMOVNG | Conditional move if less or equal/Conditional move if not greater.                                                                                                |

| CMOVOConditional move if overflow.CMOVNOConditional move if not overflow.CMOVSConditional move if sign (negative).CMOVNSConditional move if not sign (non-negative).CMOVP/CMOVPEConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPOConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGBCompare and exchange.CMPXCHGBBCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.POPA/POPADPop general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CMOVC         | Conditional move if carry.                                                                                                                                        |

| CMOVNOConditional move if not overflow.CMOVSConditional move if sign (negative).CMOVNSConditional move if not sign (non-negative).CMOVP/CMOVPEConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPOConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGSCompare and exchange.CMPXCHGSBCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.POPA/POPADPop general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CMOVNC        | Conditional move if not carry.                                                                                                                                    |

| CMOVSConditional move if sign (negative).CMOVNSConditional move if not sign (non-negative).CMOVP/CMOVPEConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPOConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGCompare and exchange.CMPXCHG8BCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CMOVO         | Conditional move if overflow.                                                                                                                                     |

| CMOVNSConditional move if not sign (non-negative).CMOVP/CMOVPEConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPOConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGCompare and exchange.CMPXCHG8BCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CMOVNO        | Conditional move if not overflow.                                                                                                                                 |

| CMOVP/CMOVPEConditional move if parity/Conditional move if parity even.CMOVNP/CMOVPOConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGCompare and exchange.CMPXCHGSBCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CMOVS         | Conditional move if sign (negative).                                                                                                                              |

| CMOVNP/CMOVPOConditional move if not parity/Conditional move if parity odd.XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGCompare and exchange.CMPXCHG8BCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CMOVNS        | Conditional move if not sign (non-negative).                                                                                                                      |

| XCHGExchange.BSWAPByte swap.XADDExchange and add.CMPXCHGCompare and exchange.CMPXCHG8BCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CMOVP/CMOVPE  | Conditional move if parity/Conditional move if parity even.                                                                                                       |

| BSWAPByte swap.XADDExchange and add.CMPXCHGCompare and exchange.CMPXCHG8BCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CMOVNP/CMOVPO | Conditional move if not parity/Conditional move if parity odd.                                                                                                    |

| XADDExchange and add.CMPXCHGCompare and exchange.CMPXCHG8BCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XCHG          | Exchange.                                                                                                                                                         |

| CMPXCHGCompare and exchange.CMPXCHG8BCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BSWAP         | Byte swap.                                                                                                                                                        |

| CMPXCHG8BCompare and exchange 8 bytes.PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | XADD          | Exchange and add.                                                                                                                                                 |

| PUSHPush onto stack.POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CMPXCHG       | Compare and exchange.                                                                                                                                             |

| POPPop off of stack.PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CMPXCHG8B     | Compare and exchange 8 bytes.                                                                                                                                     |

| PUSHA/PUSHADPush general-purpose registers onto stack.POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PUSH          | Push onto stack.                                                                                                                                                  |

| POPA/POPADPop general-purpose registers from stack.CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | POP           | Pop off of stack.                                                                                                                                                 |

| CWD/CDQConvert word to doubleword/Convert doubleword to quadword.CBW/CWDEConvert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PUSHA/PUSHAD  | Push general-purpose registers onto stack.                                                                                                                        |

| CBW/CWDE Convert byte to word/Convert word to doubleword in EAX register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | POPA/POPAD    | Pop general-purpose registers from stack.                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CWD/CDQ       | Convert word to doubleword/Convert doubleword to quadword.                                                                                                        |

| MOVSX Move and sign extend.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CBW/CWDE      | Convert byte to word/Convert word to doubleword in EAX register.                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MOVSX         | Move and sign extend.                                                                                                                                             |

8/30/2017 (©J.P. Shen)

18-600 Lecture #2

#### 5.1.2 Binary Arithmetic Instructions

| The binary arithmetic instructions perform basic binary integer computations on byte, word, and doubleword inte- |  |

|------------------------------------------------------------------------------------------------------------------|--|

| gers located in memory and/or the general purpose registers.                                                     |  |

| ADCX | Unsigned integer add with carry.    |

|------|-------------------------------------|

| ADOX | Unsigned integer add with overflow. |

| ADD  | Integer add.                        |

| ADC  | Add with carry.                     |

| SUB  | Subtract.                           |

| SBB  | Subtract with borrow.               |

| IMUL | Signed multiply.                    |

| MUL  | Unsigned multiply.                  |

| IDIV | Signed divide.                      |

| DIV  | Unsigned divide.                    |

| INC  | Increment.                          |

| DEC  | Decrement.                          |

| NEG  | Negate.                             |

| CMP  | Compare.                            |

|      |                                     |

#### 5.1.3 Decimal Arithmetic Instructions

| The decima             | al arithmetic instructions perform decimal arithmetic on binary coded decimal (BCD) data.         |

|------------------------|---------------------------------------------------------------------------------------------------|

| DAA                    | Decimal adjust after addition.                                                                    |

| DAS                    | Decimal adjust after subtraction.                                                                 |

| AAA                    | ASCII adjust after addition.                                                                      |

| AAS                    | ASCII adjust after subtraction.                                                                   |

| AAM                    | ASCII adjust after multiplication.                                                                |

| AAD                    | ASCII adjust before division.                                                                     |

| 5.1.4                  | Logical Instructions                                                                              |

| The logical<br>values. | instructions perform basic AND, OR, XOR, and NOT logical operations on byte, word, and doubleword |

| AND                    | Perform bitwise logical AND.                                                                      |

| OR                     | Perform bitwise logical OR.                                                                       |

| XOR | Perform bitwise logical exclusive OR. |

|-----|---------------------------------------|

| NOT | Perform bitwise logical NOT.          |

#### 5.1.5 Shift and Rotate Instructions

| The shift and rotate instructions shift and rotate the bits in word and doubleword operan |                                           |

|-------------------------------------------------------------------------------------------|-------------------------------------------|

| SAR                                                                                       | Shift arithmetic right.                   |

| SHR                                                                                       | Shift logical right.                      |

| SAL/SHL                                                                                   | Shift arithmetic left/Shift logical left. |

SHRD Shift right double.

8/30/2017 (©J.P. Shen)

| SHLD | Shift left double.          |

|------|-----------------------------|

| ROR  | Rotate right.               |

| ROL  | Rotate left.                |

| RCR  | Rotate through carry right. |

| RCL  | Rotate through carry left.  |

#### 5.1.6 Bit and Byte Instructions

Bit instructions test and modify individual bits in word and doubleword operands. Byte instructions set the value of a byte operand to indicate the status of flags in the EFLAGS register.

|                     | ······································                                                                                                                     |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BT                  | Bit test.                                                                                                                                                  |

| BTS                 | Bit test and set.                                                                                                                                          |

| BTR                 | Bit test and reset.                                                                                                                                        |

| BTC                 | Bit test and complement.                                                                                                                                   |

| BSF                 | Bit scan forward.                                                                                                                                          |

| BSR                 | Bit scan reverse.                                                                                                                                          |

| SETE/SETZ           | Set byte if equal/Set byte if zero.                                                                                                                        |

| SETNE/SETNZ         | Set byte if not equal/Set byte if not zero.                                                                                                                |

| SETA/SETNBE         | Set byte if above/Set byte if not below or equal.                                                                                                          |

| SETAE/SETNB/SETNC   | Set byte if above or equal/Set byte if not below/Set byte if not carry.                                                                                    |

| SETB/SETNAE/SETC    | Set byte if below/Set byte if not above or equal/Set byte if carry.                                                                                        |

| SETBE/SETNA         | Set byte if below or equal/Set byte if not above.                                                                                                          |

| SETG/SETNLE         | Set byte if greater/Set byte if not less or equal.                                                                                                         |

| SETGE/SETNL         | Set byte if greater or equal/Set byte if not less.                                                                                                         |

| SETL/SETNGE         | Set byte if less/Set byte if not greater or equal.                                                                                                         |

| SETLE/SETNG         | Set byte if less or equal/Set byte if not greater.                                                                                                         |

| SETS                | Set byte if sign (negative).                                                                                                                               |