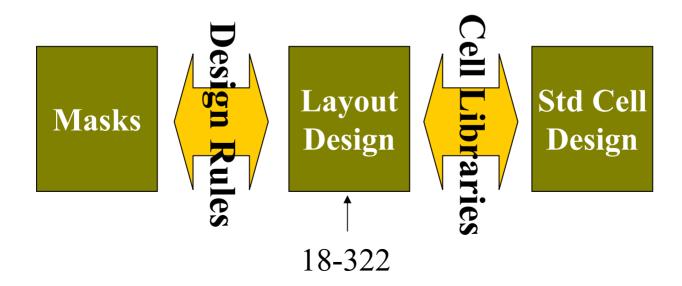

#### Layout Design

#### Lecture 4 18-322 Fall 2003

Textbook: Design Methodology Insert A

[Portions adapted from J. P. Uyemura "Introduction to VLSI Circuits and Systems", Wiley 2001.]

- Today: Basic CMOS Layout: "design in the small"

- Thursday: Layout Verification & "design in the large"

- Next week:

- ➡ Transistor sizing

- **⊠**Wires

- Homework 1: Due Thursday

- Homework 2: Out Thursday

- Lab 2: This week

# Today's Overview

Physical structure of ICs

Design rules

Basic gates layout

Stick diagrams

Basic rules

Examples

Cadence (Virtuoso)

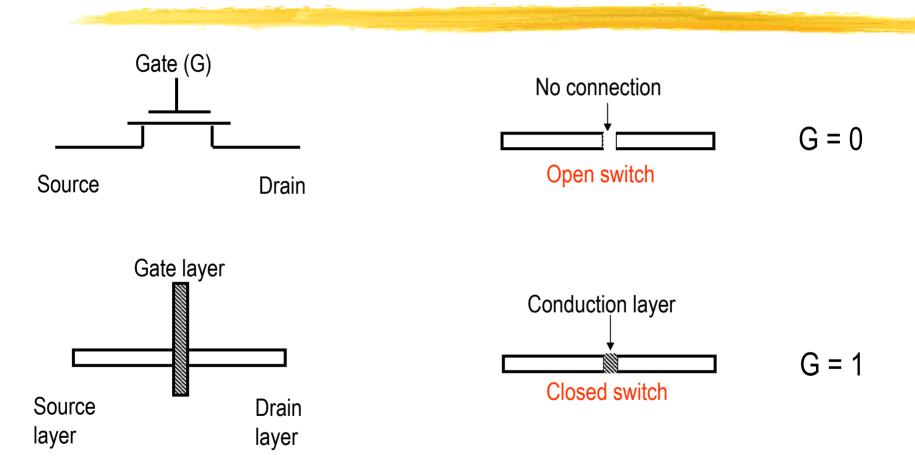

# **Review: MOSFETs**

G is responsible for the absence or presence of the conduction region between the drain and the source regions

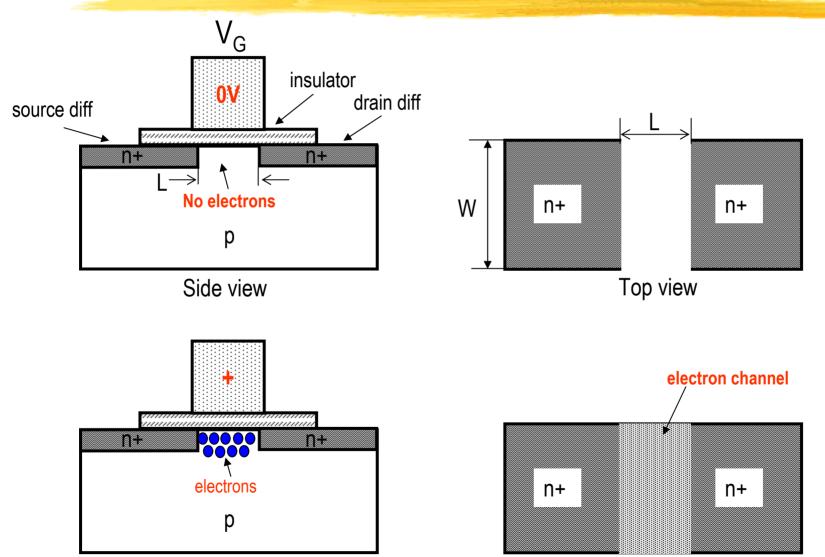

# Review: Controlling Current Flow (nFET)

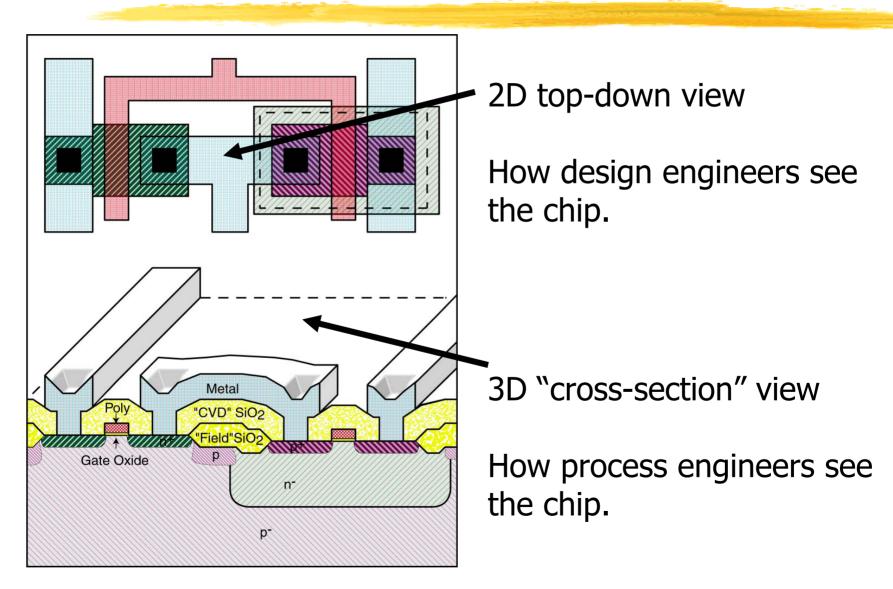

# **Review: Manufacturing**

# **Design Rules**

Interface between designer and process engineer

- Clean separation between the process during wafer fabrication and the design effort

- ☑ Permissible geometries -> DESIGN RULES

- Width rule, space rule, overlap rule, etc.

#### Ways to do design rules

- △ Absolute measures

# Scalable Design Rules

#### CMOS scales

- □ Implement something now, shrink it later

- Express all design rules in terms of a unit dimension

- Change the actual dimension of the unit, and the whole design shrinks

Mead and Conway

- Unit dimension: Minimum line width  $(2\lambda)$

$\square$  In 1978,  $\lambda = 1.5 \mu$ m (a.k.a. 3 micron technology)

$\square$  In 2003,  $\lambda = 0.065 \mu$ m (a.k.a. 0.13 micron technology)

Important Intellectual idea, not used in industry (but we will)

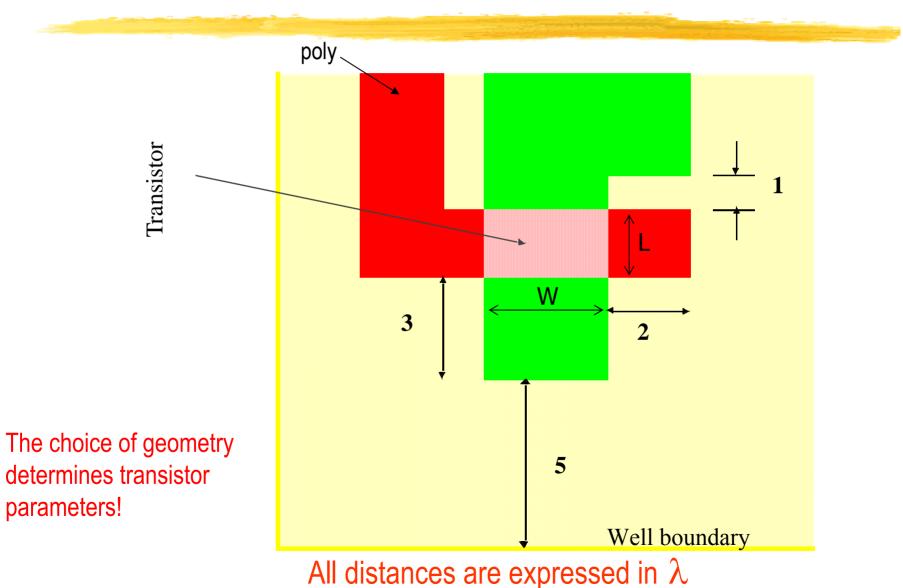

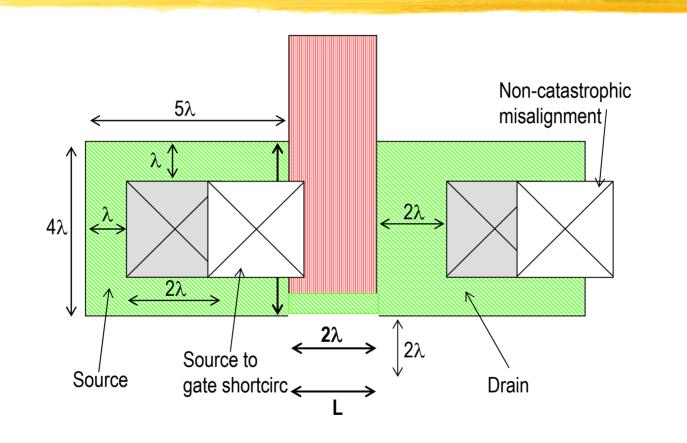

# **Transistor Layout**

#### **Transistor Layout**

$$A_{\rm S} = A_{\rm D} = 5\lambda W$$

$$\lambda = 0.5\mu \text{m} \rightarrow \text{A} = 12.5\mu \text{m}^2$$

# Absolute Design Rules

- It is hard to scale every aspect of design linearly

- The elegance of scalable CMOS isn't worth the cost

- Specify all dimensions in real units (μm or nm)

- Currently (0.13 micron), there are THOUSANDS of design rules

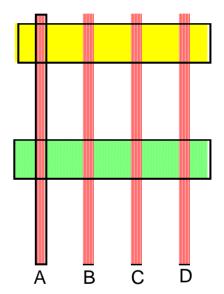

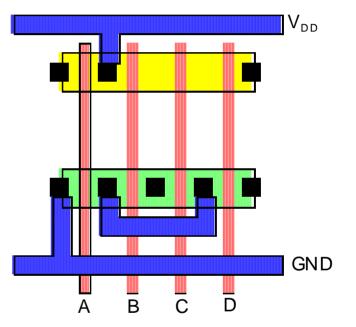

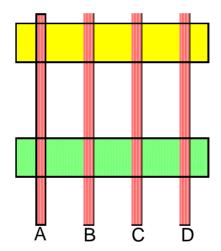

# **CMOS Process Layers**

| Layer                | Color   | Representation |

|----------------------|---------|----------------|

| Well (p,n)           | Yellow  |                |

| Active Area (n+,p+)  | Green   |                |

| Select (p+,n+)       | Green   | CTTTTT3        |

| Polysilicon          | Red     |                |

| Metal1               | Blue    |                |

| Metal2               | Magenta |                |

| Contact To Poly      | Black   |                |

| Contact To Diffusion | Black   |                |

| Via                  | Black   |                |

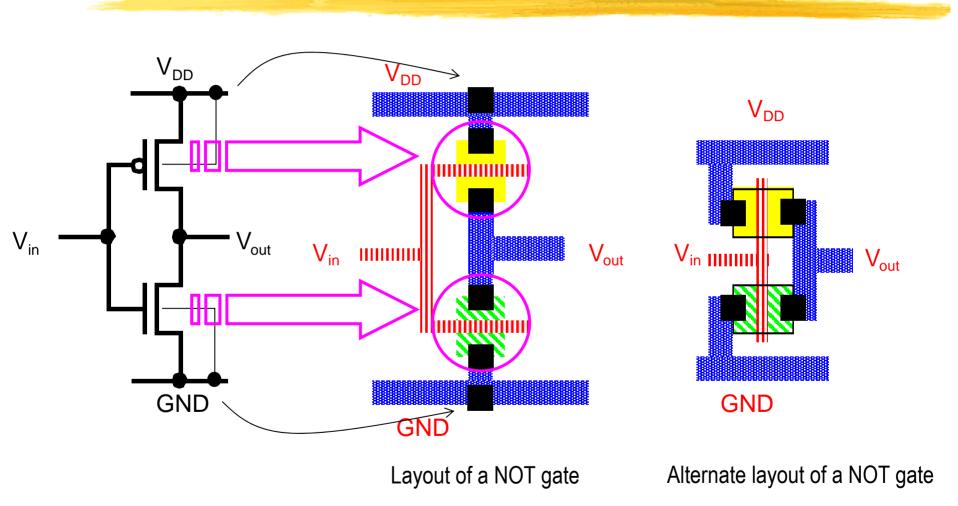

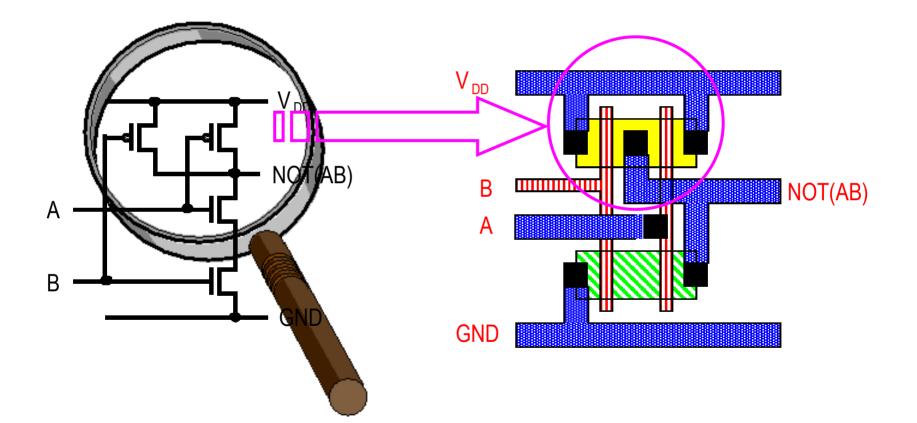

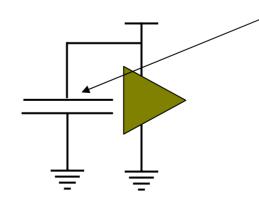

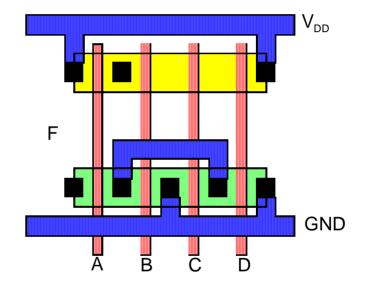

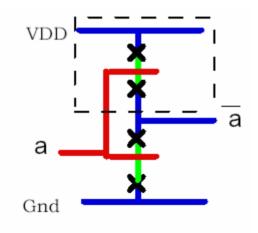

#### Inverters

Transistor sizing determines inverter fundamental properties!

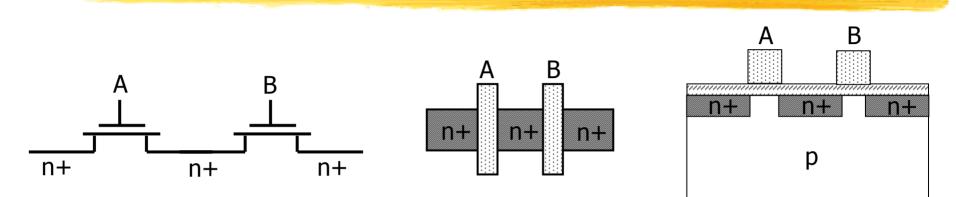

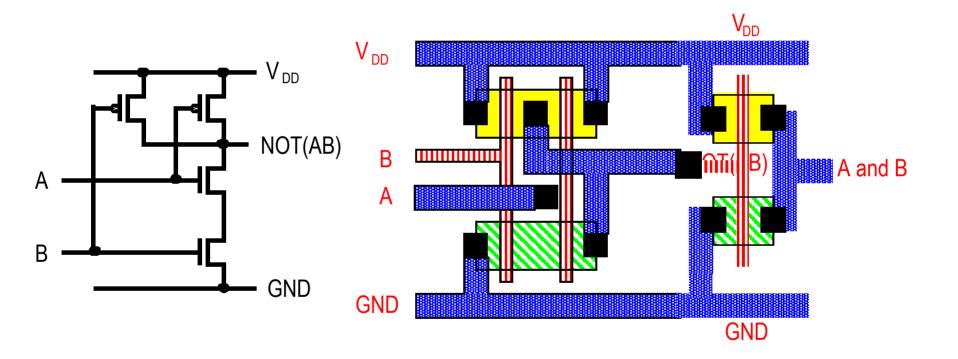

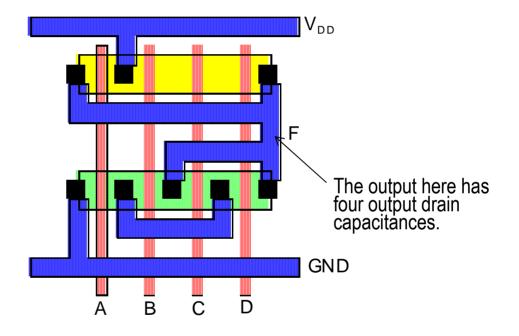

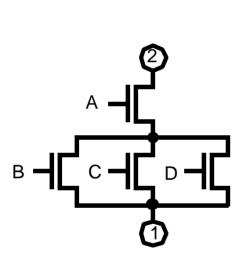

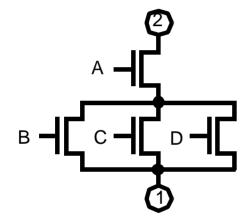

# **Series/Parallel Connections**

Devices can share patterned regions; this may reduce the layout area or complexity!

# Question: How About AND2?

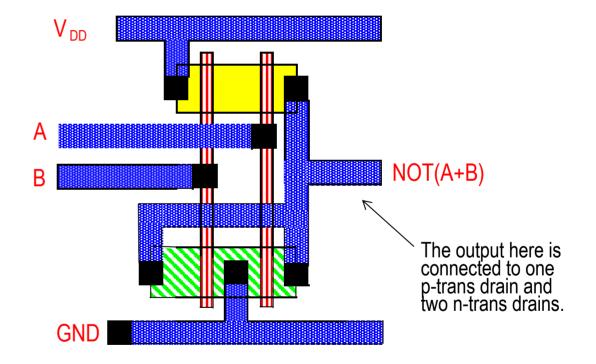

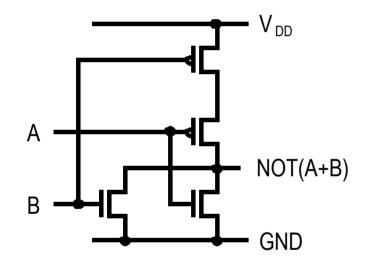

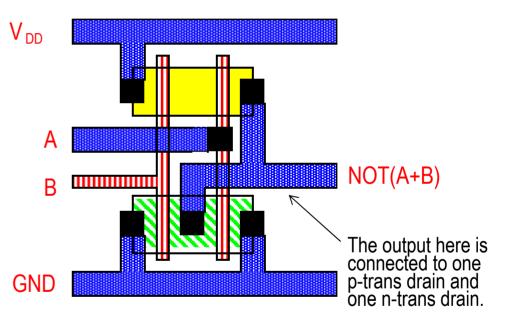

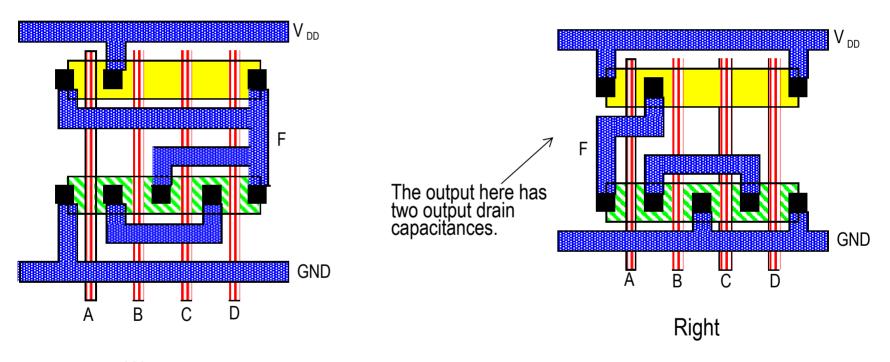

# NOR2 (alternate layout)

#### This is better!

Less drain area connected to the output . This results in a faster gate.

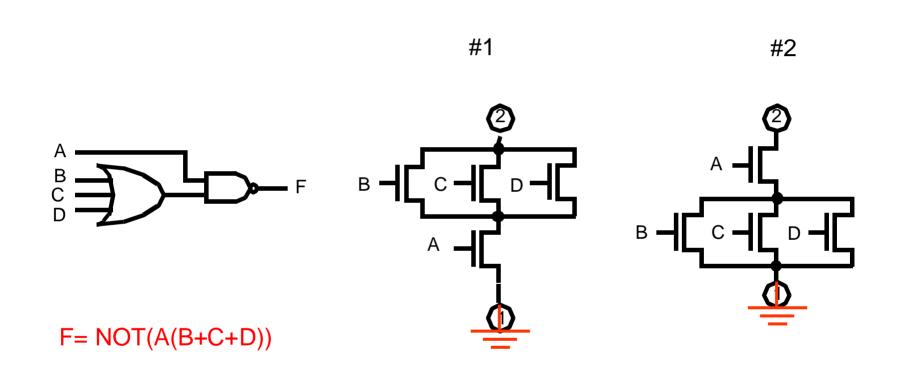

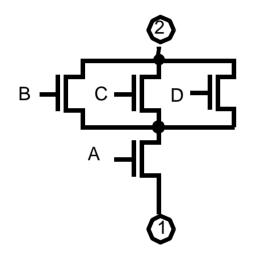

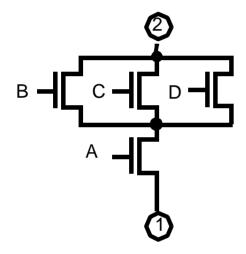

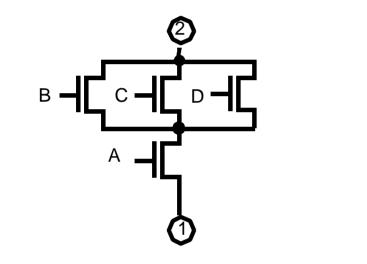

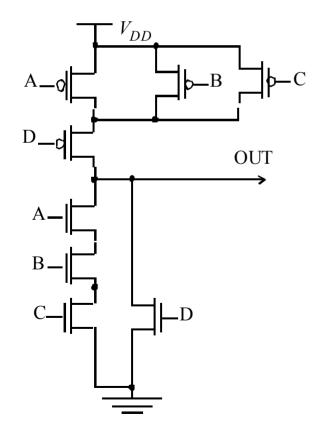

#### **Complex Logic Gates: OAI Gates**

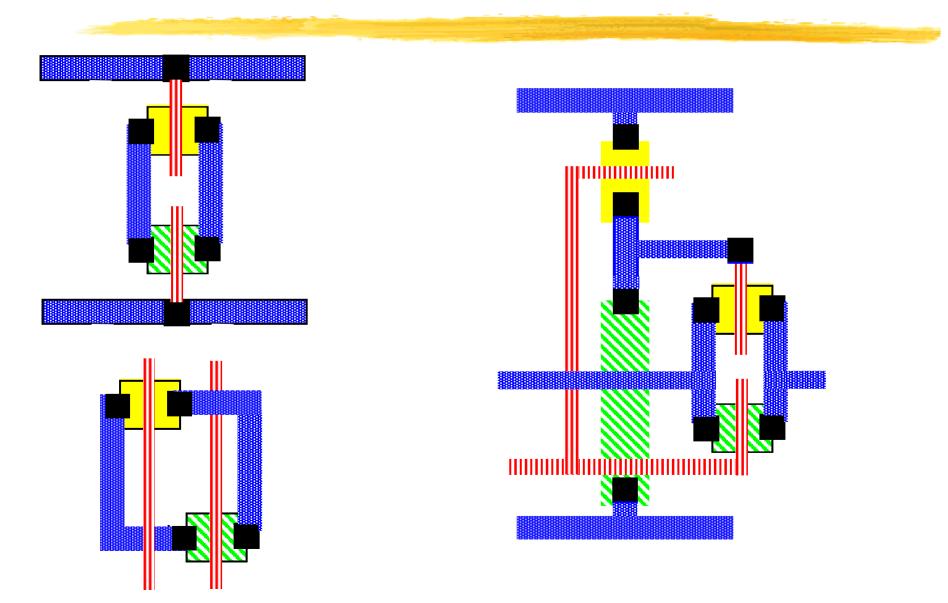

# OAI Gates: Sharing S/D (option 1)

## OAI Gates: Sharing S/D

# OAI Gates: Sharing S/D

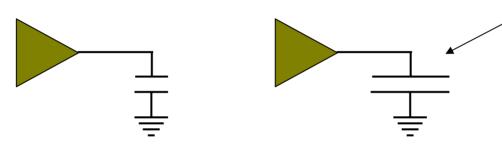

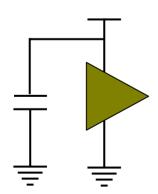

# Capacitance: Friend or Foe???

Foe: Slows down the output:

Big Capacitance More charge to to change voltage SLOWER!

Friend: Stabilizes the Power Supply

Big Capacitance More charge to to change voltage More stable supply voltage!

# OAI Gates: Sharing S/D (option 2)

#2

# OAI Gates: Sharing S/D

# OAI Gates: Sharing S/D

Wrong

# Gate Design Procedure

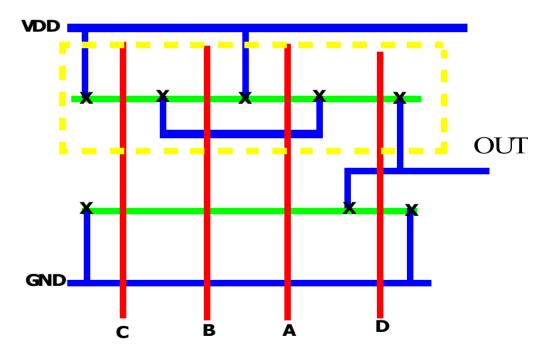

Run VDD and GND in metal at top and bottom

- Run vertical poly for each gate input

- Order gates to allow maximum source-drain abutting

- Place max number of n-diffusions close to GND

- Place max number of p-diffusions close to VDD

- Make remaining connections with metal

Minimize metal usage

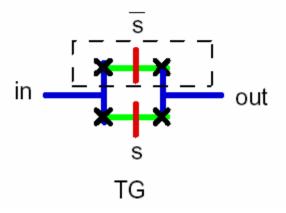

# Question: How About TGs?

Physical structure of ICs

Design rules

Basic gates layout

Stick diagrams

Basic rules

Examples

Cadence (Virtuoso)

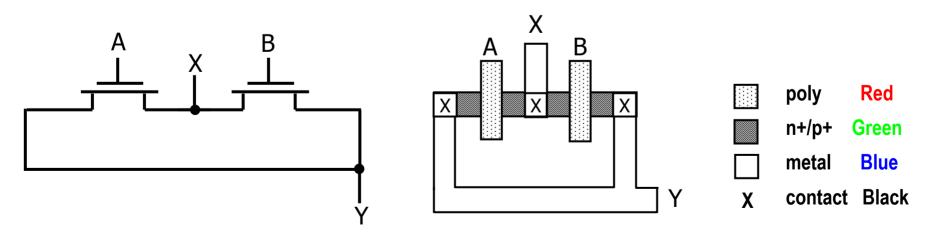

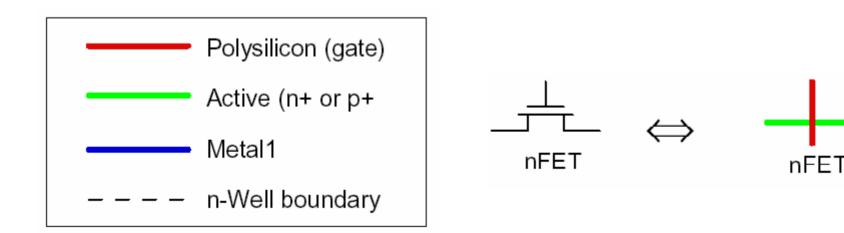

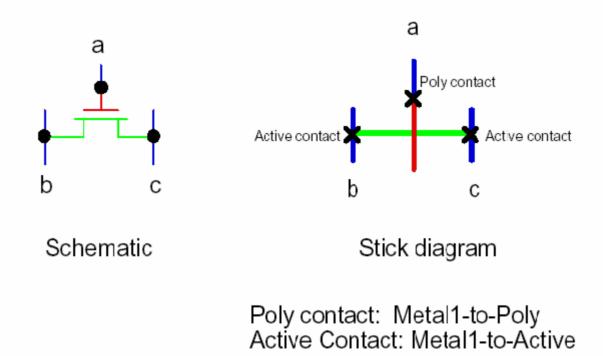

# **Stick Diagrams**

- •Introduced by Mead & Conway in the '80s

- •Every line of a conduction material layer is represented by a line of a distinct color

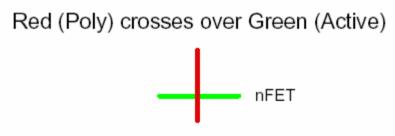

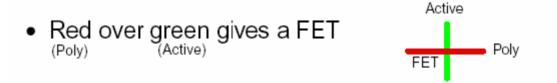

# nFET and pFET Representations

In terms of stick diagrams, we thus say that an nFET is formed whenever

This is consistent with a top view of the transistor.

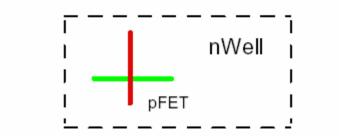

A pFET is described by the same "red over green" coding, but the crossing point is contained within an nWell boundary

# Basic Rules (1)

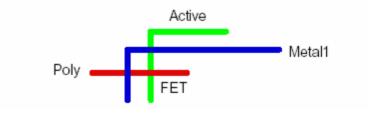

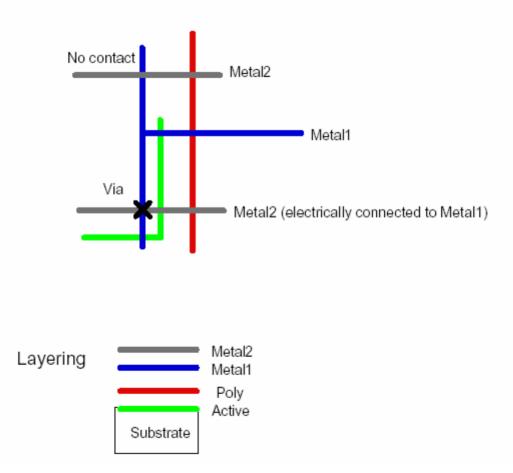

The rules for constructing stick diagrams are based on the characteristics of the conducting layers.

• Only the routing is important, not the line widths

Blue may cross over green or red without a connection

(Metal1)

(Metal1)

# Basic Rules (2)

Connections between layers are specified by  $igstar{\mathbf{X}}$

# Basic Rules (3)

Metal lines on different layers can cross one another. Contacting two metal lines requires a via

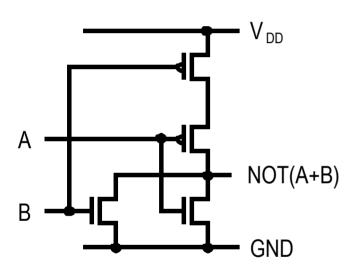

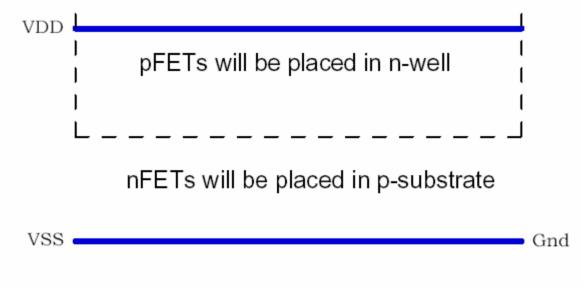

# Logic Gates Design

To create CMOS logic gates, we start with the VDD and VSS (ground) lines. We will use a horizontal orientation for the lines. Remember that stick diagrams only deal with the routing. Widths and spacings are not important.

We have included an n-well region around VDD

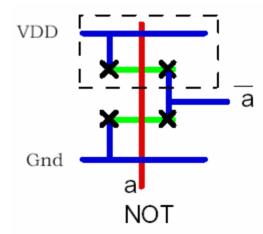

# Examples

NOT

#### **Complex Functions**

$OUT = \overline{ABC + D}$

- Discussed

Design rules

Basic gates layout

Stick diagrams

- Need more practice on

Stick diagrams

Layout (mostly in the lab)

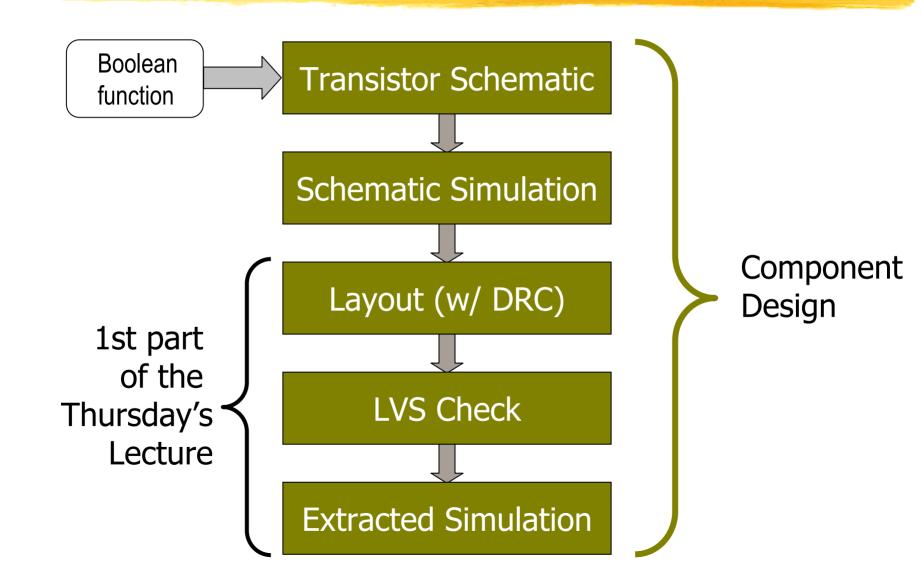

### Preview: The 18-322 Flow

# Preview: Modern ASIC Design

- Designer Productivity is a big problem

- In 1978, people could draw transistors, now there are 100s of millions per chip...

- New abstractions necessary: