Table of Contents

As FPGAs are changing in terms of their incorporation into the computing landscape, so have our views of the CoRAM architecture and abstraction. Recently we have added CoRAM++ to support data-structure-specific memory interfaces for FPGA computing and are actively working towards incorporating shared-memory processor-FPGA systems into the CoRAM abstraction. A new website is under construction to showcase our recent and ongoing CoRAM efforts. In the mean time, this site is still active for those who would like to explore our CoRAM “Classic” reconfigurable computing abstraction.

Overview

In the quest for energy-efficient computing, Field Programmable Gate Arrays (FPGAs) have emerged as a class of general-purpose accelerators with significant potential for addressing the increasing demands for performance while reducing energy consumption simultaneously. Despite their raw capabilities, today's commodity FPGAs are impractical as general-purpose computing devices. When developing an application for an FPGA, designers are often confronted by: (1) low-level, error-prone hardware description languages (HDL), (2) ``bare-bones'' fabric with nothing but a sea of logic and I/O pins, and (3) low-level, vendor-specific interfaces and gateware that the application must be made compatible with.

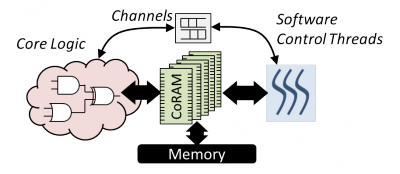

To address these limitations, the Connected RAM (CoRAM) memory architecture is an endeavor to standardize and simplify how FPGA computing applications interact with memory and I/O, which is a critical step towards a portable FPGA abstraction. CoRAM presents a programmable, customizable view of memory that can be retargeted to different devices and platforms (see Figure, right). The abstraction modifies the traditional FPGA's on-die SRAMs to act as in-fabric distributed portals to off-chip memory and I/O. A salient feature of CoRAM is the ability to program these customizable, on-die SRAMs using a software control thread that is portable and easy-to-use. Compared to the traditional approach where the FPGA memory hierarchy and I/O sub-system is hand-built at the RTL-level for each application, the CoRAM memory architecture can be used to efficiently support a broad range of applications.

People

Faculty: James C. Hoe, Ken Mai

Students: Eric S. Chung, Michael K. Papamichael, Gabriel Weisz, Cagla Cakir, Yu Wang, Marie Nguyen, Joseph Melber

Acknowledgments

Funding for this work is provided, in part, by the National Science Foundation (CCF-1012851) and by Altera. We thank Altera and Xilinx for their donation of tools and hardware.

Related

Convolutional Neural Network Demo using the GraphGen compiler and CoRAM back end

Workshop on the Intersections of Computer Architecture and Reconfigurable Logic (CARL 2013)

PyCoRAM - A Python-based Implementation of the CoRAM Memory Architecture.

Workshop on the Intersections of Computer Architecture and Reconfigurable Logic (CARL 2012)

Workshop on the Intersections of Computer Architecture and Reconfigurable Logic (CARL 2010)