# SIA Road Map and DESIGN&TEST

Wojciech Maly

Department of Electrical and Computer Engineering Carnegie Mellon University Pittsburgh, Pa. 15213.

Copyright © W. Maly

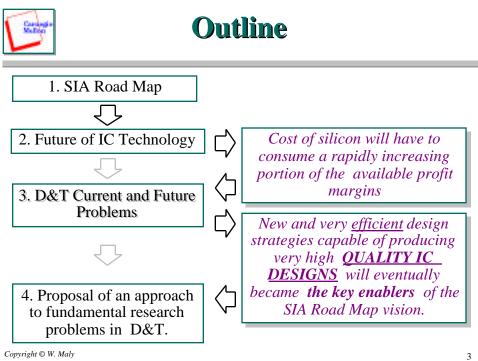

# **Objective**

To discuss fundamental research in Design and Test (D&T) of VLSI ICs

D&T Current and Future Problems Future of IC Technology

#### SIA Road Map

Copyright © W. Maly

#### **SIA Road Map**

| <b>1994 SIA Road Map Assumptions</b> |

|--------------------------------------|

|--------------------------------------|

| Year                                                   | 1995  | 1998  | 2001      | 2004      | 2007   | 2010   |

|--------------------------------------------------------|-------|-------|-----------|-----------|--------|--------|

| Feature size [µm]                                      | 0.35  | 0.25  | 0.18      | 0.12      | 0.1    | 0.08   |

| Wafer diameter [mm]                                    | 200   | 200   | 300       | 300       | 400    | 400    |

|                                                        |       | l I   | <br>M E N | <br>1 O R | Y      |        |

| Tr. per chip [10 6]                                    | 64    | 256   | 1024      | 4096      | 16384  | 65536  |

| Cost per tr. [millicents]                              | 0.017 | 0.007 | 0.003     | 0.001     | 0.0005 | 0.0002 |

| Chip size [mm <sup>2</sup> ]                           | 190   | 280   | 420       | 640       | 960    | 1400   |

| Tr. density [10 <sup>6</sup> # tr. / cm <sup>2</sup> ] | 34    | 91    | 244       | 640       | 1707   | 4681   |

|                                                        |       | μΡ    | RO        | <br>CSS   | O R    |        |

| Tr. per chip [10 6]                                    | 10    | 21    | 46.8      | 107.5     | 260    | 558    |

| Cost per tr. [millicents]                              | 1     | 0.5   | 0.2       | 0.1       | 0.05   | 0.02   |

| Chip size [mm <sup>2</sup> ]                           | 250   | 300   | 360       | 430       | 520    | 620    |

|                                                        |       |       |           |           |        |        |

#### **SIA Road Map**

- SIA Road Map is a collective view on the future of the microelectronics industry;

- The objective of the SIA Road Map was a consolidation of the vision for the entire semiconductor industry;

- Such a consolidation was a necessary step in focusing industry, governments and universities on the same technology development objectives;

- The SIA Road Map has a strong "technology/ manufacturing/ equipment" orientation;

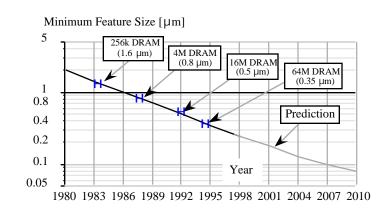

- The SIA Road Map is a "linear extrapolation" of the trends known from the past;

- The SIA Road Map is a "self-fulfilling prophecy" which facilitates continuation of the evolution of the semiconductor industry along Moore's Law;

# **SIA Road Map : MEMORY**

| Year                                                   | 1995  | 1998  | 2001  | 2004  | 2007   | 2010   |

|--------------------------------------------------------|-------|-------|-------|-------|--------|--------|

| Feature size [µm]                                      | 0.35  | 0.25  | 0.18  | 0.12  | 0.1    | 0.08   |

| Tr. per chip [10 6]                                    | 64    | 256   | 1024  | 4096  | 16384  | 65536  |

| Cost per tr. [millicents]                              | 0.017 | 0.007 | 0.003 | 0.001 | 0.0005 | 0.0002 |

| Chip size [mm <sup>2</sup> ]                           | 190   | 280   | 420   | 640   | 960    | 1400   |

| Wafer diameter [mm]                                    | 200   | 200   | 300   | 300   | 400    | 400    |

| Tr. density [10 <sup>6</sup> # tr. / cm <sup>2</sup> ] | 34    | 91    | 244   | 640   | 1707   | 4681   |

| Yield [%]                                              | 90    | 90    | 90    | 90    | 90     | 90     |

| Number of chips per wafer                              | 142   | 93    | 148   | 91    | 110    | 72     |

| Wafer area [cm <sup>2</sup> ]                          | 314   | 314   | 706.5 | 706.5 | 1256   | 1256   |

| Number of good chips                                   | 127   | 83    | 133   | 81    | 99     | 64     |

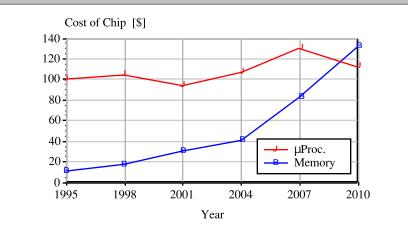

| Cost per chip [\$]                                     | 10.88 | 17.92 | 30.72 | 40.96 | 81.92  | 131.07 |

| Cost per wafer [\$]                                    | 1382  | 1487  | 4086  | 3318  | 8110   | 8389   |

| Number of masks                                        | 18    | 20    | 20    | 22    | 22     | 24     |

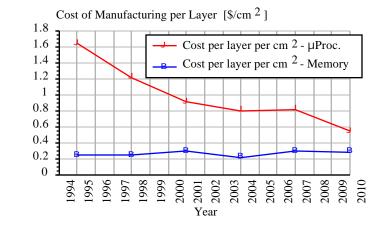

| Cost per mask per sq.[\$/cm 2]                         | 0.24  | 0.24  | 0.29  | 0.21  | 0.29   | 0.28   |

Cofylight @wlyngiyr the discussion

# SIA Road Map : µPROCESSOR

| Year                                                   | 1995 | 1998 | 2001  | 2004  | 2007  | 2010  |

|--------------------------------------------------------|------|------|-------|-------|-------|-------|

| Feature size [µm]                                      | 0.35 | 0.25 | 0.18  | 0.12  | 0.1   | 0.08  |

| Tr. per chip [10 6]                                    | 10   | 21   | 46.8  | 107.5 | 260   | 558   |

| Cost per tr. [millicents]                              | 1    | 0.5  | 0.2   | 0.1   | 0.05  | 0.02  |

| Chip size [mm <sup>2</sup> ]                           | 250  | 300  | 360   | 430   | 520   | 620   |

| Wafer diameter [mm]                                    | 200  | 200  | 300   | 300   | 400   | 400   |

| Tr. density [10 <sup>6</sup> # tr. / cm <sup>2</sup> ] | 4    | 7    | 13    | 25    | 50    | 90    |

| Yield [%]                                              | 90   | 90   | 90    | 90    | 90    | 90    |

| Number of chips per wafer                              | 104  | 89   | 168   | 140   | 211   | 177   |

| Wafer area [cm <sup>2</sup> ]                          | 314  | 314  | 706.5 | 706.5 | 1256  | 1256  |

| Number of good chips                                   | 93   | 80   | 151   | 126   | 189   | 159   |

| Cost per chip [\$]                                     | 100  | 105  | 93.6  | 107.5 | 130   | 111.6 |

| Cost per wafer [\$]                                    | 9300 | 8400 | 14134 | 13545 | 24570 | 17744 |

| Number of masks                                        | 18   | 22   | 22    | 24    | 24    | 26    |

| Cost per mask per sq.[\$/cm 2]                         | 1.65 | 1.22 | 0.91  | 0.80  | 0.82  | 0.54  |

Constitute @ WIMfor the discussion

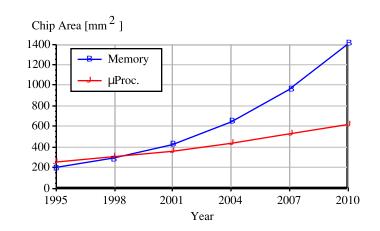

SIA Road Map Assumptions -Chip Size

Copyright © W. Maly

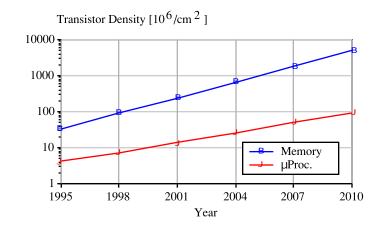

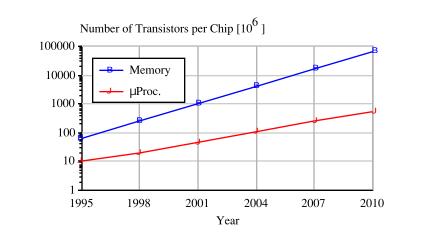

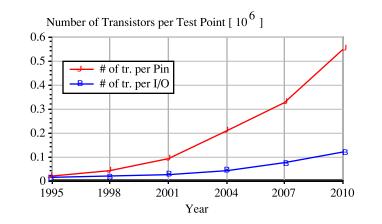

SIA Road Map Consequences -Number of Transistors

Copyright © W. Maly

13

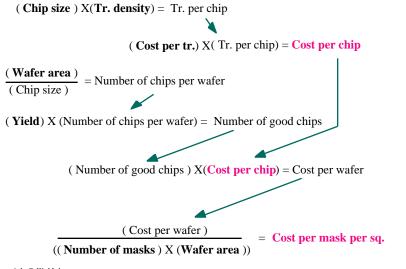

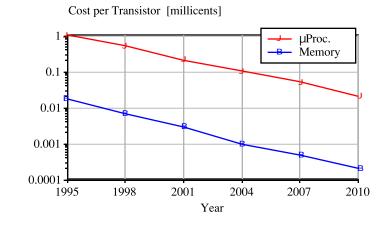

#### SIA Road Map Consequences -Manufacturing Costs

1994 SIA Road Map assumes that:

- exponential growth in die size,

- exponential growth in transistor density and

- exponential decrease in cost per transistor,

can be handled with unchanged (or even decreased) manufacturing cost per unit square.

### Is such a goal really feasible ?

| Year | Min.<br>Feature<br>Size<br>[µm] | Interconnect<br>Density<br>[m/cm <sup>2</sup> /level] | Interconnect<br>Length<br>[m] |

|------|---------------------------------|-------------------------------------------------------|-------------------------------|

| 1995 | 0.40                            | 35                                                    | 380                           |

| 1998 | 0.30                            | 50                                                    | 840                           |

| 2001 | 0.22                            | 70                                                    | 2100                          |

| 2004 | 0.15                            | 105                                                   | 4100                          |

| 2007 | 0.11                            | 125                                                   | 6300                          |

| 2010 | 0.08                            | 155                                                   | 10,000                        |

# Implications of SIA Road Map: Interconnect

Copyright © W. Maly

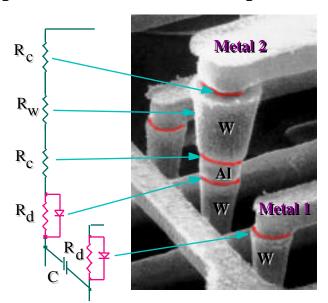

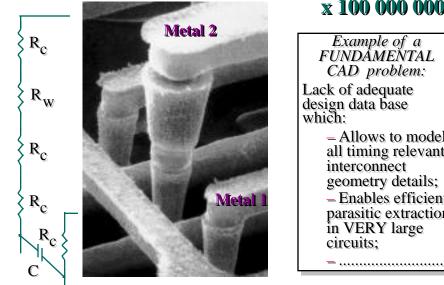

**Implications of SIA Road Map: Interconnect** R<sub>c</sub> Metal 2 Rw W R<sub>c</sub> AI Metal 1 R<sub>c</sub> W R C W С Copyright © W. Maly

x 100 000 000

17

### Implications of SIA Road Map: Interconnect

Complexity of the interconnect will strongly affect the methodology of DESIGN, MANUFACTURING and TEST.

# Interconnect may become a main show stopper of the SIA Road Map.

Copyright © W. Maly

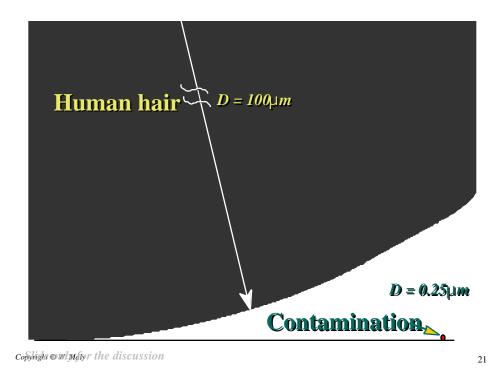

Silicon Wafer R = 15 cmLegislate of the discussion R = 15 cm D = 100 cmCross-sections of a human hair

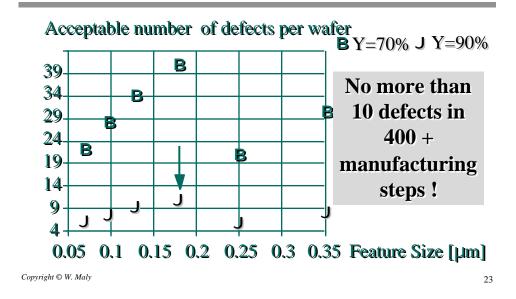

#### $Y = \frac{1}{1 + A_{ch} D_0}$ Die Area [cm <sup>2</sup>] 14 B $D_0 = \frac{1 - Y}{YA_{ch}}$ 13 12 11 10 For Y = 70% $D_0 = \frac{.43}{A_{ch}}$ 9 B 8 B 7 3 6 For Y = 90% $D_0 = \frac{.11}{A_{ch}}$ 5 4 0.2 0.15 0.25 0.3 0.35 0.05 0.1 Feature Size [µm] Copyright © W. Maly

# Implications of SIA Road Map: Manufacturing

#### Implications of SIA Road Map: Manufacturing

#### Implications of SIA Road Map: Manufacturing

Complexity of IC processes must cause rapid increase in cost of IC manufacturing.

# Cost of manufacturing may become a main show stopper on the SIA Road Map.

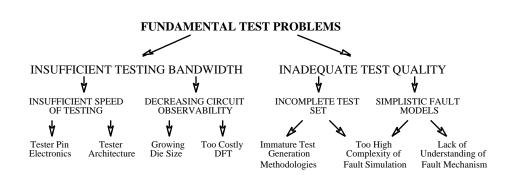

# Implications of SIA Road Map: Testing

Copyright © W. Maly

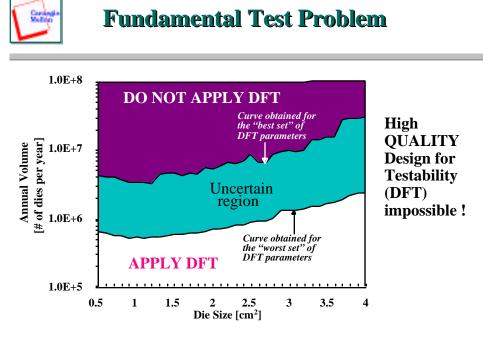

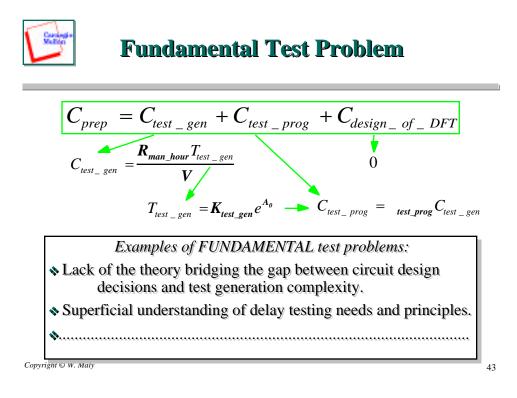

## Implications of SIA Road Map: Testing

- Testing will have to handle very large devices/ systems;

- New difficult-to-detect failures will have to be tested.

- Data dependent cross-talk failures;

- Power bus noise generated faults;

- R-F coupling generated faults.

- Solution Very high band-width testers will be required;

- Massive application of DFT will be a must.

Copyright © W. Maly

27

# Implications of SIA Road Map: Testing

Complexity of ICs to be tested will soon reach levels impossible to be handled with the testing paradigm as it is known today.

# Tester limitations may become a main show stopper on the SIA Road Map.

SEMATECH Copyright © W. Maly

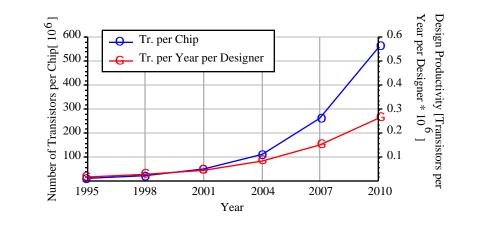

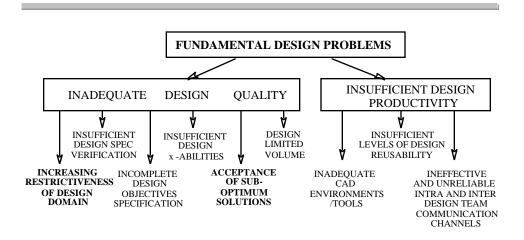

#### **Implications of SIA Road Map: Design**

- Design productivity will have to increase by orders of magnitude;

- Design verification (on all levels of design abstraction) will become an absolute necessity;

## Implications of SIA Road Map: Design

Size of ICs to be designed will soon reach levels impossible to be handled with the design paradigm as it is known today.

#### Design productivity and design verification may become key show stoppers on the SIA Road Map.

Copyright © W. Maly

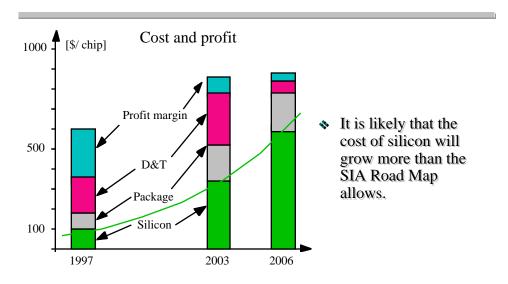

SIA Road Map Consequences -Manufacturing Costs

1994 SIA Road Map assumes that

the substantial increase in complexity of :

- manufacturing,

- test and

- design,

can be handled with unchanged (or even decreased) manufacturing cost per unit square.

#### Is such a goal really feasible ?

Copyright © W. Maly

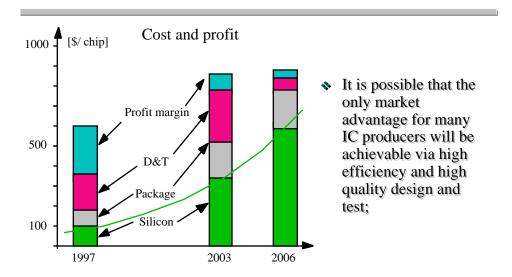

#### **SIA Road Map Consequences -Manufacturing** Costs

1994 SIA Road Map assumes that

the substantial increase in complexity of :

- manufacturing,

- test and

- design,

can be handled with unchanged (or even decreased) manufacturing cost per unit square.

#### Is such a goal really feasible ? 1997 Road Map says NO !

*Cost of silicon will have to consume a rapidly increasing* portion of the available profit margins. Copyright © W. Maly

33

# **SIA Road Map: Implications**

#### **SIA Road Map: Implications**

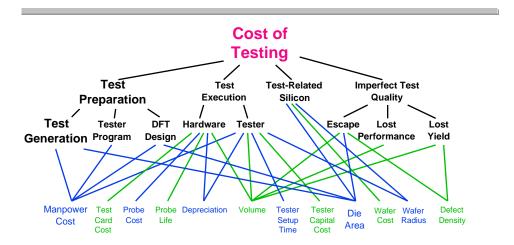

$$\mathbf{C}_{\mathrm{D\&T}} = \mathbf{C}_{\mathrm{TE}} + \frac{\mathbf{C}_{\mathrm{D}} + \mathbf{C}_{\mathrm{TG}}}{\mathbf{V}_{\mathrm{Ch}}} \longrightarrow \mathbf{C}_{\mathrm{TE}}$$

♦ Cost of D&T can be substantially reduced by increasing volume of sold chips.

$$\mathbf{C}_{\text{Silicon}} = \mathbf{C}_{\text{Material}} + \mathbf{C}_{\text{Own.}} + \frac{\mathbf{C}_{\text{TD}}}{\mathbf{V}_{\text{Ch}}}$$

Cost of silicon cannot be reduced beyond a certain level by increasing volume of sold chips.

Copyright © W. Maly

35

# **SIA Road Map: Implications**

#### **Design Quality**

|                 | Intel P6 ( Kalmath)       | Mitsubishi D30V         |

|-----------------|---------------------------|-------------------------|

| Type:           | CISC (32 bit data/instr.) | DSP LIW (64 bit instr.) |

| Applications:   | Universal (MPEG2,)        | M-Media (MPEG2, V-ph.)  |

| Load for DVD:   | 100 %                     | 90 %                    |

| Technology:     | 0.28 µm CMOS              | 0.3 µm CMOS             |

| Clock:          | 233 MHz;                  | 250 MHz;                |

| # Trans. Total: | 7.5 M (with 32K L1 cache) | 300 K + 64K SRAM        |

| Area:           | $203 \text{ mm}^2$        | $37 \text{ mm}^2$       |

| Price:          | TBA                       | TBA                     |

|                 | (PPro - 200 MHz = \$1072) | (Est. < \$50)           |

Compiled by **Pierre Paulin** of ST based on the data published in EE Times and µP Rep.

37

# **SIA Road Map Implications**

SIA Road Map will cause:

- Cost of silicon to go up;

- Price of chips to go up (but with well defined upper limit);

- Progress along Moore's curve to slow down;

- Design and test budgets to go down;

- Design efficiency and design quality to become the most important knobs in profit maximization.

New and very <u>efficient</u> design strategies capable of producing very high <u>OUALITY IC</u> <u>DESIGNS</u> will eventually became the key enablers of the SIA Road Map vision.

Copyright © W. Maly

# **Fundamental Problems: DESIGN**

#### **Limitations of Design Domain**

Copyright © W. Maly

x 100 000 000

Example of a FUNDAMENTAL CAD problem: Lack of adequate design data base which: Allows to model all timing relevant interconnect geometry details; - Enables efficient parasitic extraction in VERY large

# **Sub-optimum Designs**

| Intel P6 (Kalmath)        | Mitsubishi D30V         |

|---------------------------|-------------------------|

| CISC (32 bit data/instr.) | DSP LIW (64 bit instr.) |

| MPEG2                     | MPEG2                   |

| 7.5 M (with 32K L1 cache) | 300 K + 64K SRAM        |

| 203 mm <sup>2</sup>       | 37 mm <sup>2</sup>      |

Is Mitsubishi design close enough to optimum ?

Example of a FUNDAMENTAL design problem: Lack of adequate objective functions for hardwaresoftware co-design which : - Take into account cost and time of design process;

- Forecast volume to be sold;

- Predict true cost of manufacturing.

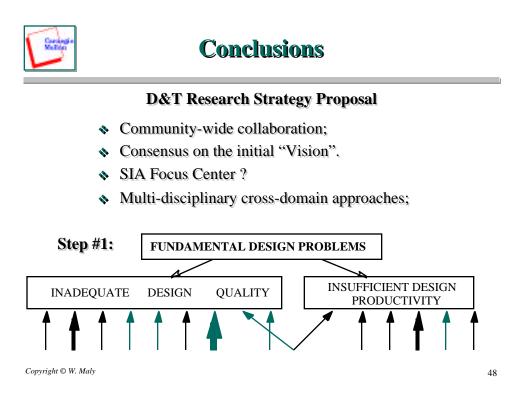

#### **Conclusions**

- Microelectronics industry may approach a highcost-of-manufacturing-based crisis;

- Design&Test may need to:

- operate with lower time and "\$" budgets;

- become a main and the only provider of market advantage;

47

- deliver much better designs.

- Design&Test community need to re-think the traditional view on its role and strategy;