HARRIS REAL TIME EXPRESS:

A NEW CONCEPT FOR REALTIME CONTROL

- SEMICONDUCTOR PRODUCTS DIVISION

#### HARRIS -

#### AGENDA - ROCHESTER RTX SEMINAR

| 0 | INTRODUCTION/<br>Technology overview  | AUDITORIUM |  |  |  |  |

|---|---------------------------------------|------------|--|--|--|--|

| 0 | RTX 2000 ARCHITECTURE                 | AUDITORIUM |  |  |  |  |

| 0 | RTX Applications<br>& interfacing     | AUDITORIUM |  |  |  |  |

| 0 | RTXDS BACKEROUND                      | AUDITORIUM |  |  |  |  |

| 0 | LUNCH                                 |            |  |  |  |  |

| 0 | GUEST SPEAKERS                        | AUDITORIUM |  |  |  |  |

| 0 | RTXDB                                 | MAY ROOM   |  |  |  |  |

| • | TFORTH COMPILER & UTILITIES           | MAY ROOM   |  |  |  |  |

| 0 | DEBUGGER                              | MAY ROOM   |  |  |  |  |

|   | · · · · · · · · · · · · · · · · · · · |            |  |  |  |  |

RTX 2000 ARCHITECTURE

- SEMICONDUCTOR PRODUCTS DIVISION .

#### RTX 2000 ARCHITECTURE

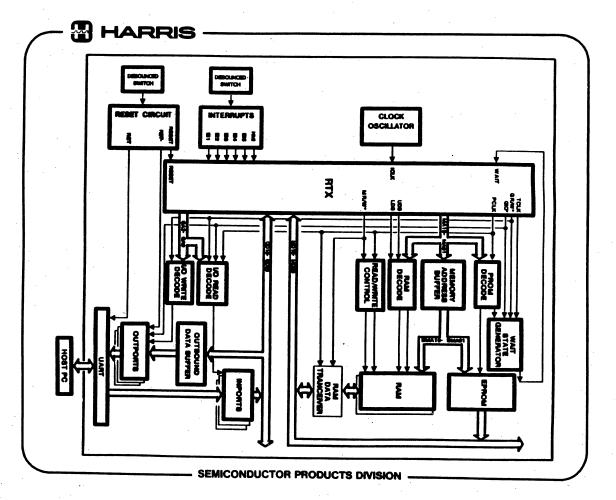

- O BASED ON NOVIX 4016/6016 ARCHITECTURE

- O ON-CHIP PARAMETER AND RETURN STACKS

- O ON-CHIP PERIPHERALS

MULTIPLIER

INTERRUPT CONTROLLER

COUNTER/TIMERS

- O ADDRESS 1 MEGABYTE OF MEMORY

Architecture - 1

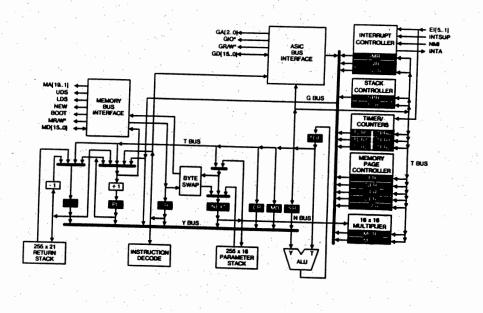

#### RTX 2000 BLOCK DIAGRAM

Architecture - 2

- SEMICONDUCTOR PRODUCTS DIVISION

#### STACKS

- O PARAMETER STACK

256 WORDS DEEP

16 BITS WIDE

TOP TWO ELEMENTS ARE AVAILABLE THROUGH ON-CHIP REGISTERS

- O RETURN STACK

256 WORDS DEEP

21 BITS WIDE

- 15 BITS PROGRAM COUNTER - 4 BITS CODE PAGE - 1 BIT INTERRUPT STATUS - 1 BIT DATA PAGE FLAG

TOP ELEMENT AVAILABLE THROUGH ON-CHIP REGISTER

#### REGISTERS

- O TOP TOP ELEMENT OF PARAMETER STACK

- O NEXT SECOND ELEMENT OF PARAMETER STACK

- O INDEX TOP ELEMENT OF RETURN STACK. LOOP COUNTER.

- O CONTROL/STATUS CONFIGURATION REGISTER (CR) INTERRUPT BASE/CONTROL REGISTER (IBC)

- O MULTISTEP DIVIDE (MD) USED FOR STEP MATH OR GENERAL PURPOSE

- O SQUARE ROOT (SR) USED FOR SQUARE ROOTS OR GENERAL PURPOSE

- O MEMORY PAGE REGISTERS

CODE PAGE INSTRUCTION FETCHES

DATA PAGE MEMORY ACCESS (0 ! ETC)

USER PAGE USER MEMORY ACCESS

- O I/O DEVICES

MULTIPLIER OUTPUT

COUNTER/TIMERS

INTERRUPT MASK

INTERRUPT VECTOR

STACK POINTERS

STACK LIMITS

Architecture - 4

- SEMICONDUCTOR PRODUCTS DIVISION

#### On-CHIP PERIPHERALS

- O STACK CONTROLLERS

PROGRAMMABLE LIMIT REGISTERS

GENERATE INTERRUPTS ON OVERFLOW AND UNDERFLOW CONDITIONS

- O INTERRUPT CONTROLLER

14 INTERRUPT SOURCES, INTERNAL AND EXTERNAL

13 MASKABLE, 1 NON-MASKABLE

SOFTWARE INTERRUPT

- O MULTIPLIER

SINGLE CYCLE 16 x 16 MULTIPLY WITH 32-BIT RESULT

FORTH \* IN 3 CYCLES

- O COUNTER/TIMERS (3)

16-BIT DOWN COUNTERS

CLOCKED INTERNALLY (TIMERS) OR EXTERNALLY (COUNTERS)

GENERATE INTERRUPTS ON O COUNT

Architecture - 5

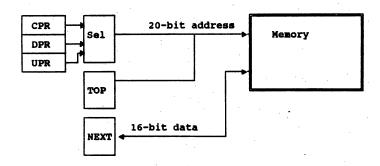

#### MEMORY INTERFACE

- O 1 MEGABYTE ADDRESS SPACE 16 32K PAGES

- O PAGE REGISTERS SELECT APPROPRIATE PAGE

- O BYTE AND WORD ACCESS

Architecture - 6

- SEMICONDUCTOR PRODUCTS DIVISION .

#### HARRIS -

#### MEMORY INTERFACE

Architecture - 7

#### ASIC Bus<sup>TM</sup>

- DATA PATH BETWEEN TOP AND OTHER REGISTERS AND I/O DEVICES 0

- INPUT DATA IS FED THROUGH ALU BEFORE GOING INTO TOP

- SIMPLE INTERFACE FOR MULTI-RTX APPLICATIONS ٥

Architecture - 8

- SEMICONDUCTOR PRODUCTS DIVISION

#### A HARRIS

#### RTX INSTRUCTION SET

ALL PROCESSOR INSTRUCTIONS ARE 16 BITS, WITH THE FOLLOWING GENERAL FIELDS:

| ٠. | 15 1  | 2 11 | 8 | 7 6 | 5 | 4    | 0 |

|----|-------|------|---|-----|---|------|---|

|    | Class | ALU  |   | sc  | ; | Data |   |

CLASS - GENERAL TYPE OF INSTRUCTION:

SUBROUTINE CALL

BRANCHES AND LOOPS

MATH/LOGIC FUNCTIONS

REGISTER AND 1/0 ACCESS

SHORT LITERAL

LONG LITERALS

MAIN MEMORY ACCESS

USER MEMORY ACCESS

ALU - ALU FUNCTION TO BE PERFORMED.

SC - SUBCLASS. FUNCTION DEPENDS ON CLASS FIELD.

- RETURN BIT. WHEN SET, CAUSES A RETURN-FROM-SUBROUTINE

DATA - DEPENDING ON CLASS, INDICATES SHIFT OPERATION, SHORT LITERAL DATA, G-SPACE ADDRESS, OR MEMORY ADDRESS.

Architecture - 9

#### RTX INSTRUCTION SET

SUBROUTINE CALLS

SUBROUTINE CALL TAKES PLACE IN ONE CLOCK CYCLE

RETURN-FROM-SUBROUTINE CAN BE PART OF ANOTHER INSTRUCTION

BRANCHING AND LOOPING

UNCONDITIONAL BRANCH

CONDITIONAL BRANCH BASED ON CONTENTS OF TOP REGISTER

CONDITIONAL BRANCH BASED ON CONTENTS OF INDEX REGISTER WITH

AUTO DECREMENT OF INDEX REGISTER

ALU OPERATIONS AND OR NAND NOR XOR XNOR NOT

SHIFT OPERATIONS

16 AND 32-BIT SHIFTS, EITHER DIRECTION SIGNED AND UNSIGNED SHIFTS CAN BE COMBINED WITH ALU OPERATIONS

STEP MATH DIVIDE SQUARE ROOT

REGISTER-I/O ACCESS

READ/WRITE PROCESSOR REGISTER OR I/O DEVICE

COMBINE ALU OPERATION WITH DATA FROM REGISTER

SHORT LITERALS

LOAD VALUE 0 - 31 INTO TOP REGISTER

COMBINE ALU OPERATION WITH DATA

LITERAL VALUE IS EMBEDDED IN INSTRUCTION

Architecture - 10

- SEMICONDUCTOR PRODUCTS DIVISION

RTX INSTRUCTION SET

LONG LITERALS

LOAD 10-BIT VALUE INTO TOP REGISTER

COMBINE ALU OPERATION WITH DATA

MEMORY ACCESS

ADDRESS IN TOP REGISTER, DATA IN NEXT REGISTER

ACCESS MEMORY BY BYTE OR BY WORD

ACCESS PROGRAM MEMORY, DATA MEMORY, OR USER MEMORY

ACCESS MEMORY IN EITHER MSB-LSB OR LSB-MSB BYTE ORDER

COMBINE ALU OPERATION WITH MEMORY DATA

MOVE BLOCKS OF MEMORY TO/FROM STACK WITH AUTO ADDRESS UPDATE

STREAMED INSTRUCTION MODE EXECUTE INSTRUCTION REPEATEDLY WITHOUT EXTRA FETCH CYCLES

HARRIS

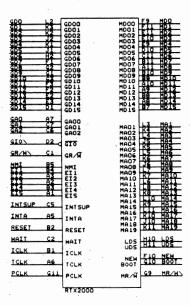

# HARRIS RTX2000 PROCESSOR PINOUT

# MEMORY INTERFACE PINS ASIC BUS INTERFACE PINS INTERRUPT/RESET PINS CLOCK/WAIT PINS

SEMICONDUCTOR PRODUCTS DIVISION

INTERFACING THE RTX2000: PROCESSOR PINOUT

# HARRIS RTX2000 MEMORY INTERFACE PINS

MD00 TO MD15: MEMORY DATA BUS

MA01 TO MA19: MEMORY ADDRESS BUS

LDS, UDS: LOWER / UPPER

DATA SELECT (NOT STROBED)

**NEW: INSTRUCTION FETCH**

**BOOT: GENERAL PURPOSE**

MR/W\: MEMORY READ / WRITE

SEMICONDUCTOR PRODUCTS DIVISION

# HARRIS RTX2000 ASIC BUS INTERFACE PINS

GD0-GD15: G-BUS DATA GA0-GA2: G-BUS ADDRESS GIO\: G-BUS STROBE

GR/W\: G-BUS READ/WRITE\

# HARRIS RTX2000 INTERRUPT/RESET PINS

NMI: NON-MASKABLE INTERRUPT EI1 - EI5: EXTERNAL INTERRUPTS EI3 - EI5: TIMER/COUNTER INPUTS INTSUP: INTERRUPT SUPPRESS INTA: INTERRUPTACKNOWLEDGE RESET: MASTER RESET

SEMICONDUCTOR PRODUCTS DIVISION

# HARRIS RTX2000 CLOCK/WAIT PINS

WAIT: WAIT STATE INPUT

ICLK: INPUT CLOCK

TCLK: TIMING CLOCK

FREE RUNNING

PCLK: PROCESSOR CLOCK

HELD LOW FOR WAIT STATES

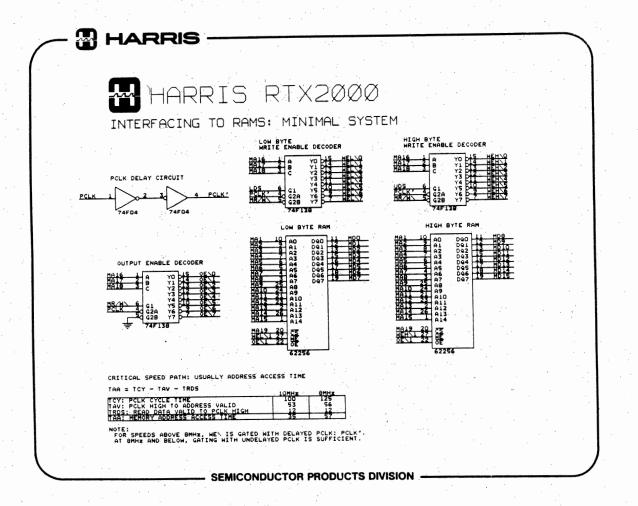

## HARRIS RTX2000

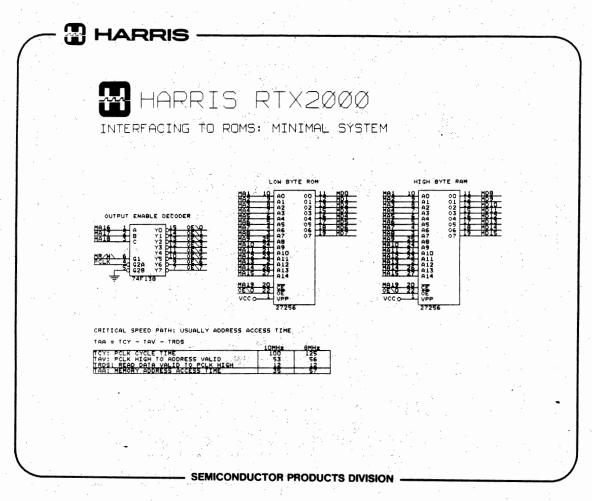

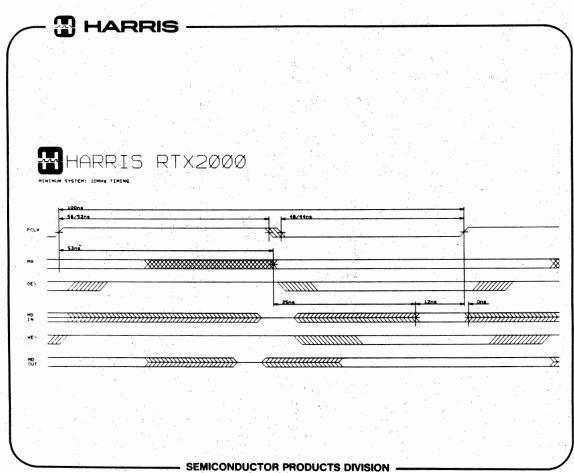

# MINIMAL SYSTEM TIMING ALLOWS THE USE OF THE SLOWEST MEMORIES NO DECODE OR BUFFERING IN ADDRESS OR CHIP ENABLE PATHS AT MAX SPEED: WE\ DELAYED TO ASSURE ADDRESS SETUP TIME TAA = TCY - TAV - TRDS

HARRIS

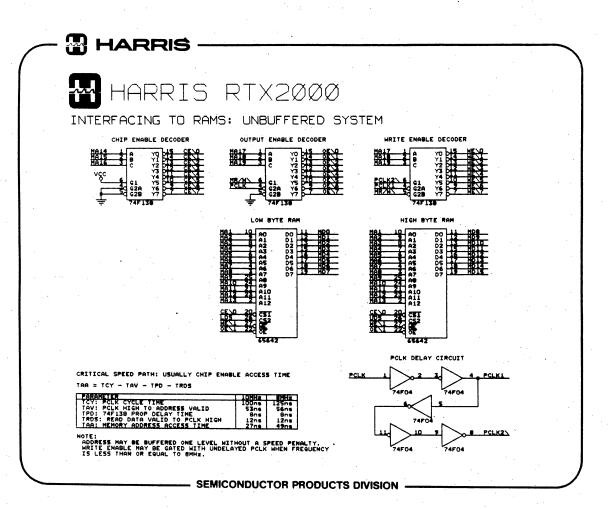

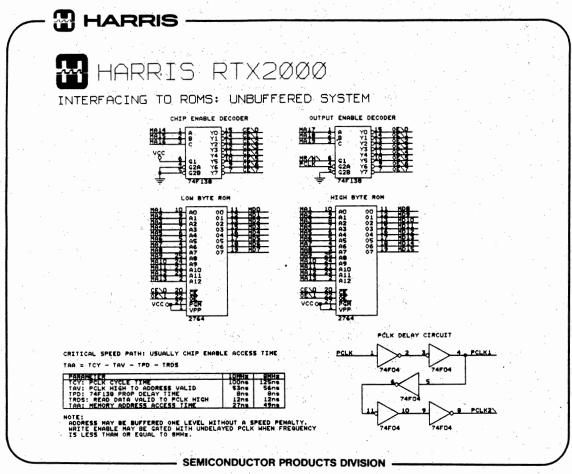

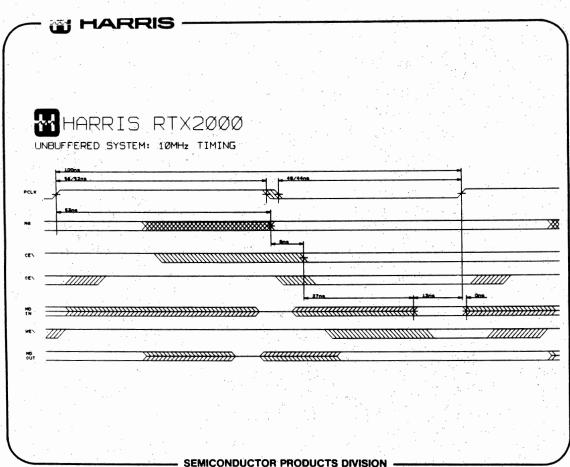

# HARRIS RTX2000 UNBUFFERED SYSTEM TIMING

ALLOWS GREATER

DECODING RANGE

LOWER SYSTEM POWER

ONLY ONE DECODER

IN CRITICAL PATH

TAA = TCY - TAV - TPD - TRDS

WE\REQUIRES GREATER

DELAY AT FULL SPEED

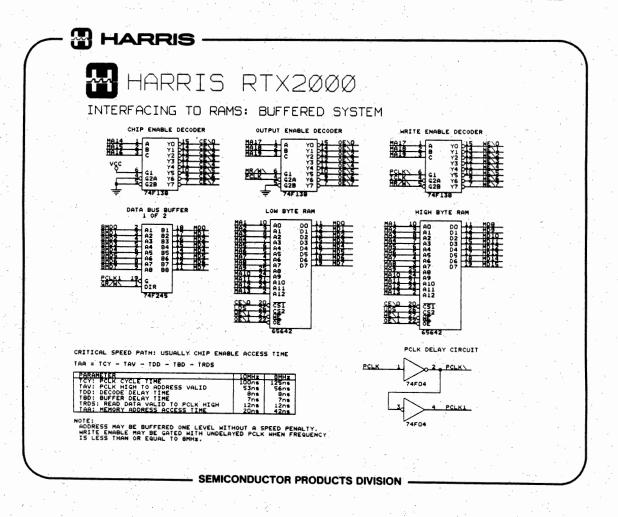

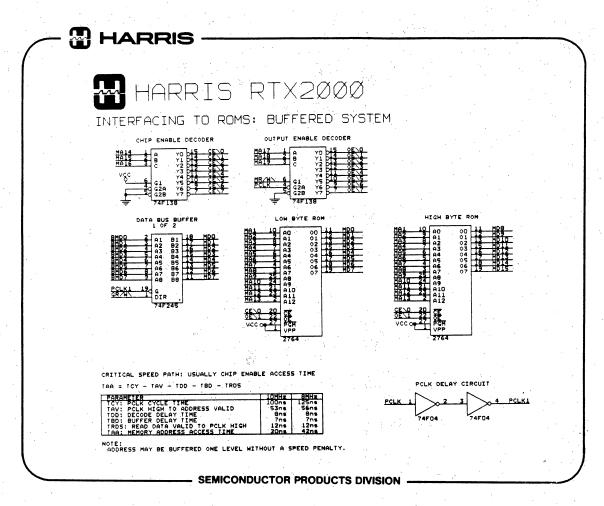

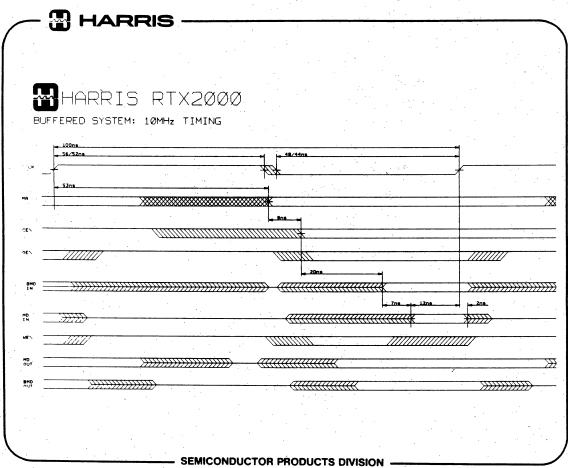

# HARRIS RTX2000 BUFFERED SYSTEM TIMING

FULLY BUFFERED FOR LARGE

MEMORY ARRAYS

DATA BUFFER DELAY IN

CRITICAL SPEED PATH

BOTH WE\ AND DATA BUFFER

ENABLE DELAYED FOR

WRITE CYCLE AT FULL SPEED

TAA = TCY-TAV-TDD-TBD-TRDS

A STATE OF THE STA

# HARRIS RTX2000 ASIC BUS INTERFACE

OUTPUT PORT STROBED WITH GIO\ TIMING NOT CRITICAL INPUT PORT TIMING CRITICAL STROBED EVERY READ CYCLE ON 74F540 OR 74AC540

SEMICONDUCTOR PRODUCTS DIVISION

TYPICAL ASIC BUS INTERFACES

OUTPUT PORT DECODING IS GATED WITH GIOW TO ASSURE THAT OUTPUT LATCHES ARE ONLY STROBED AT CORRECT TIME.

INPUT PORT DECODING IS GATED WITH PCLK TO ALLOW MAXIMUM DATA SET UP TIME.

THE RTXDS DEVELOPMENT SYSTEM

- SEMICONDUCTOR PRODUCTS DIVISION

#### **OVERVIEW**

- O THE ENVIRONMENT IN WHICH THE HARRIS RTX2000 WILL BE USED IS REAL-TIME EMBEDDED PROCESS CONTROL.

- O THE REQUIREMENTS FOR THESE SYSTEMS AS COMPARED TO CONVENTIONAL COMPUTER SYSTEMS ARE UNIQUE:

- O CUSTOM DESIGNED HARDWARE AND UNIQUE I/O DEVICES AND INTERFACES.

- O INTERRUPT DRIVEN, REAL-TIME AND TIME CRITICAL APPLICATIONS.

- O ROM BASED CODE AND LIMITED AVAILABILITY OF RAM AND ROM STORAGE.

RTXDS - 1

#### DEVELOPMENT SYSTEMS

- O EMBEDDED (OR TARGET) SYSTEMS ARE GENERALLY INAPPROPRIATE ENVIRONMENTS FOR THE DEVELOPMENT OF APPLICATIONS SOFTWARE.

- O THE TARGET SYSTEM MOST OFTEN LACKS SUPPORT FOR PROGRAM DEVELOPMENT AND TESTING:

NO AUXILARY STORAGE (DISK),

NO INTERFACE TO A HUMAN OPERATOR (CRT/KEYBOARD),

LIMITED MAIN STORAGE (RAM),

- O LACK OF MATURE SOFTWARE SUPPORT AND DEVELOPMENT TOOLS.

RTXDS - 2

- SEMICONDUCTOR PRODUCTS DIVISION

#### TESTING AND FAULT ISOLATION

- O EXCESSIVE COST, IN BOTH DOLLARS AND IN ELAPSED TIME, ASSOCIATED WITH THE IMPLEMENTATION OF SOFTWARE HAS BECOME OF OVERRIDING CONCERN IN THE DESIGN AND DEVELOPMENT OF COMPUTER SYSTEMS.

- O THE SOFTWARE DEVELOPMENT PHASE MOST OFTEN UNDERESTIMATED, LEADING TO COST AND TIME OVERRUNS, IS THAT OF SOFTWARE TESTING AND FAULT ISOLATION.

- O THESE PROBLEMS ARE COMPOUNDED IN THE TESTING OF COMPLEX REAL-TIME EMBEDDED SYSTEMS.

#### TESTING OF EMBEDDED SYSTEMS

- O DEVELOPMENT AND TESTING OF SOPHISTICATED EMBEDDED SYSTEMS IS OFTEN EXCEPTIONALLY COSTLY AND TIME CONSUMING.

- O BOTH THE HARDWARE AS WELL AS THE SOFTWARE IN SUCH SYSTEMS MAY BE UNIQUE AND UNDER DEVELOPMENT. THE SYSTEM IS BEING INTEGRATED AS TESTING IS CONDUCTED. AS A RESULT, FAULTS ARE DIFFICULT TO ISOLATE.

- THE DEMANDS OF A REAL-TIME, INTERRUPT DRIVEN SYSTEMS, OFTEN WITH MULTI-TASKING, MAY INTRODUCE RACE CONDITIONS THAT CAN BE EXCEPTIONALLY DIFFICULT TO REPRODUCE AND TO DEBUG.

RTXDS - 4

SEMICONDUCTOR PRODUCTS DIVISION

#### TESTING OF EMBEDDED SYSTEMS

- O THE PROGRAMMER OR OPERATOR HAS LITTLE VISIBILITY INTO THE SYSTEM UNDER TEST. UNLIKE MORE CONVENTIONAL COMPUTER SYSTEMS, THE RESPONSES OF AN EMBEDDED SYSTEM OFTEN REFLECT SECOND OR THIRD LEVEL EFFECTS THAT MAY BE NEAR USELESS IN ISOLATING PROGRAMMING ERRORS.

- O THERE ARE FEW PERIPHERAL DEVICES ON AN EMBEDDED SYSTEM THAT ARE USEFUL IN TESTING. THERE IS NO OPERATOR INTERFACE (CRT/KEYBOARD) AND LIMITED INTERNAL STORAGE.

- O A DIGITAL ANALYZER IS A USEFUL TOOL BUT IS SOMETIMES ANKWARD BECAUSE OF THE MICROSCOPIC LEVEL OF DETAIL PROVIDED.

- O LASTLY, THERE IS NO ON-BOARD SOFTWARE TO FACILITATE TESTING OF THE PROGRAMS.

RTXDS - 5

#### **RTXDS**

# A DEVELOPMENT ENVIRONMENT FOR EMBEDDED SYSTEMS GOALS

THE SYSTEM MUST PROVIDE A FORTH INTERACTIVE SUPPORT ENVIRONMENT.

THE TOOLS SHOULD BE INTEGRATED TO FORM A SEAMLESS DEVELOPMENT ENVIRONMENT.

THE PROGRAMMER SHOULD BE ABLE TO USE SYMBOLIC REFERENCES.

THE TARGET PROCESSOR MUST BE ABLE TO OPERATE AT FULL SPEED.

RTXDS - 6

SEMICONDUCTOR PRODUCTS DIVISION

#### **RTXDS**

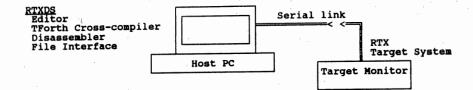

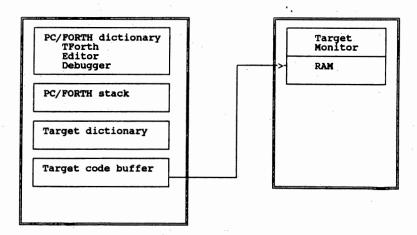

#### THE HOST

- O TO BUILD APPLICATIONS SOFTWARE IN A PRODUCTIVE AND COST EFFECTIVE MANNER, WE HAVE CHOSEN TO IMPLEMENT MUCH OF THE SOFTWARE SUPPORT ENVIRONMENT ON A HOST COMPUTER SYSTEM.

- O THE APPROACH IS AN ACCEPTED AND EFFECTIVE MEANS OF IMPLEMENTING EMBEDDED COMPUTER SYSTEMS.

- O THE HOST AND TARGET ARE CONNECTED THROUGH A SERIAL INTERFACE.

- O THE APPROACH ALLOWS A UNIQUE SOFTWARE DESIGN ENVIRONMENT; ONE THAT IS A RELIABLE COMBINATION OF HARDWARE AND SOFTWARE-AND ONE THAT IS RICH IN BOTH HARDWARE FACILITIES AND IN SOFTWARE SUPPORT TOOLS.

#### RTXDS DEVELOPMENT ENVIRONMENT

RTXDS - 8

- SEMICONDUCTOR PRODUCTS DIVISION

#### HARRIS

#### THE HOST

O WE SELECTED AS A HOST THE IBM (OR COMPATIBLE) PC WITH A FULL COMPLEMENT OF FACILITIES:

EXTENSIVE INTERNAL STORAGE,

HIGH VOLUME EXTERNAL (DISK) STORAGE,

CONVENIENT HUMAN INTERFACE (CRT/KEYBOARD),

A SOPHISTICATED SOFTWARE BUILD ENVIRONMENT AND MATURE SUPPORT TOOLS (LMI'S PC/FORTH).

#### THE TARGET

THE TARGET SYSTEM CAN BE ANY BOARD CONTAINING THE HARRIS RTX 2000 PROCESSOR ALONG WITH MINIMAL SUPPORT HARDWARE

RTXDS - 9

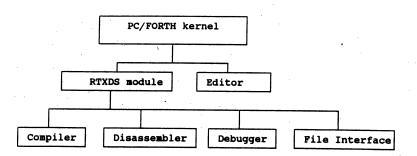

#### RTXDS STRUCTURE

RTXDS - 10

SEMICONDUCTOR PRODUCTS DIVISION

#### DEVELOPMENT TOOLS

O IN THE RTXDS DEVELOPMENT ENVIRONMENT, HARRIS PROVIDES A COMPLETE SET OF PROGRAMMING SUPPORT TOOLS TO AID THE PROGRAMMER.

#### **TFORTH**

THE TFORTH CROSS COMPILER PROVIDES THE SOFTWARE DEVELOPMENT ENGINEER WITH A SYSTEM TO CONVENIENTLY HANDLE SOURCE PROGRAMS AND TO GENERATE ROMABLE OBJECT CODE FOR THE PROCESSOR.

#### DISASSEMBLER

THE DISASSEMBLER IS A SOFTWARE DEBUG TOOL THAT CONVERTS BINARY OBJECT CODE INTO A SEQUENCE OF THE CORRESPONDING FORTH CODE.

#### FILE INTERFACE

THIS SET OF MODULES PROVIDE THE PROGRAMMER WITH CONVENIENT ACCESS TO DISK FILES.

#### HOST/TARGET SERIAL LINK

- O A DIRECT SERIAL LINK FROM THE HOST TO THE TARGET FACILITIES THE SOFTWARE BUILD PROCESS.

- O THE LINK PROVIDES A MEANS OF TRANSFERRING OBJECT CODE FROM THE HOST TO THE TARGET TO FACILITATE RAPID PROTOTYPING OF APPLICATIONS SOFTWARE.

- O IT ALSO ALLOWS US TO LINK THE TWO SUBSYSTEMS IN SUCH A WAY THAT WE NOT ONLY PROVIDE THE DESIGN ENGINEER WITH AN EFFECTIVE MEANS FOR BUILDING SOURCE PROGRAMS AND GENERATING TARGET CODE, BUT IN ADDITION THE LINK SUPPORTS A POWERFUL TESTING AND FAULT ISOLATION CAPABILITY.

RTXDS - 12

- SEMICONDUCTOR PRODUCTS DIVISION

#### RTXDS

#### VISIBILITY AND CONTROL

- O A MAJOR FUNCTION OF RTXDS IS TO PROVIDE A PROGRAMMER/OPERATOR WITH VISIBILITY INTO A CONTROL OF THE SYSTEM UNDER TEST. THE SYSTEM PROVIDES A POMERFUL SET OF UTILITIES TO SUPPORT THE APPLICATION DEVELOPER IN DEBUGGING SOFTWARE.

- O THE DEBUG FACILITIES ARE DESIGNED AND IMPLEMENTED USING THE HOST AND TARGET SUBSYSTEMS AS AN INTEGRATED SOFTWARE DEVELOPMENT FACILITY -TAKING ADVANTAGE OF THE CAPABILITIES OF EACH SUBSYSTEM IN THE DESIGN.

RTXDS - 13

#### RTXDS

#### TFORTH EMULATOR

- O THE TFORTH CROSS COMPILER IS AS CLOSE AS POSSIBLE TO A FORTH-83 SYSTEM.

- O THE TFORTH EMULATOR PROVIDES A METHOD OF TESTING APPLICATION SOURCE CODE WITH PC/FORTH ON THE HOST PC.

- O THE FACILITY IS USEFUL FOR PRELIMINARY TESTING OF AN APPLICATION.

- O THE EMULATOR MODELS THE BEHAVIOR OF THE RTX REGISTERS AND THE ASIC BUS.

RTXDS - 14

- SEMICONDUCTOR PRODUCTS DIVISION

#### **RTXDS**

- O THE SYSTEM PROVIDES HIGHLY INTERACTIVE CONTROL TO THE PROGRAMMER TESTING SOFTWARE ON THE TARGET SUBSYSTEM.

- O THE PROGRAMMER HAS THE CAPABILITY TO TEMPORARILY STOP THE EXECUTION OF PROGRAMS IN A UNIT TEST, AND TO EXAMINE AND CHANGE THE STATUS OF THE TARGET SYSTEM.

- O PROGRAMMER CONTROL IS AT THE CONSOLE OF THE HOST. THE PROGRAMMER IS ABLE TO SELECTIVELY TRACE THE ACTIONS OF PROGRAMS EXECUTING ON THE TARGET, TO EXAMINE AND TO CHANGE PROCESSOR REGISTERS AND STORAGE ON THE TARGET SUBSYSTEM.

- O REFERENCES TO THE VARIABLES AND DEFINITIONS WITHIN THE TARGET ARE SYMBOLIC. A DICTIONARY IS MAINTAINED IN THE HOST TO MAP THE SYMBOLS TO THE TARGET ADDRESSES.

>@ >C@

>! >C!

>.S >MOVE >CMOVE

>DROP >DUMP >EXECUTE

>FILL >. >U.

>.REG >.RR >PUSH >POP

>SET.BREAK >CLR.BREAK

>DOWNLOAD >UPLOAD

>60 >6! >60

>LOAD >:

RTXDS - 16

- SEMICONDUCTOR PRODUCTS DIVISION

#### RTXDS

#### VISIBILITY INTO THE TARGET

- O DISPLAY FACILITIES THROUGH THE HOST ALLOW THE PROGRAMMER TO VIEW THE PROGRESS OF EXECUTION OF A PROGRAM UNDER TEST ON THE TARGET SUBSYSTEM.

- O THESE FEATURES ARE INCORPORATED INTO THE TFORTH CROSS-COMPILER AS STANDARD FORTH FUNCTIONS.

- O THE FEATURES ARE IMPLEMENTED SUCH THAT THESE DEBUG UTILITIES GENERATE NEITHER EXECUTION OVERHEAD NOR STORAGE REQUIREMENTS IN THE FINAL TARGET SYSTEM.

RTXDS - 17

#### **RTXDS**

#### TFORTH DISPLAY UTILITIES

." EMIT

CR

.S .REG

DUMP

MEMORY REFERENCE TRACE

>RANGE

RTXDS - 18

- SEMICONDUCTOR PRODUCTS DIVISION

#### **RTXDS**

#### BREAKPOINT FACILITY

- O WE ASSUME THAT IN A TEST ENVIRONMENT, THAT CODE AS WELL AS DATA WILL RESIDE ON THE TARGET SUBSYSTEM IN RAM.

- O WE INCLUDE A CAPABILITY TO ALLOW THE PROGRAMMER TO INSERT A BREAKPOINT INTO THE CODE BEING TESTED.

- O WHEN A BREAKPOINT IS ENCOUNTERED DURING PROGRAM EXECUTION, A TRANSFER TO THE MONITOR IS INITIATED AUTOMATICALLY THAT ALLOWS THE OPERATOR TO GAIN CONTROL AT THE HOST CONSOLE.

- O THE OPERATOR HAS THE OPTION TO: Examine the target system status, Resume execution, or Cancel the breakpoint.

RTXDS - 19

#### RTXDS

#### SUMMARY

- O RTXDS PROVIDES THE PROGRAMMER WITH AN INTEGRATED FORTH ENVIRONMENT.

- O IT IS SPECIFICALLY DESIGNED TO SUPPORT THE DEVELOPMENT OF REAL-TIME EMBEDDED SYSTEMS.

- O OUR EXPERIENCE INDICATES THAT RTXDS OFFERS A FLEXIBLE AND PRODUCTIVE ENVIRONMENT FOR THE PROGRAMMER.

RTXDS - 20

#### HARRIS RTX SEMINAR

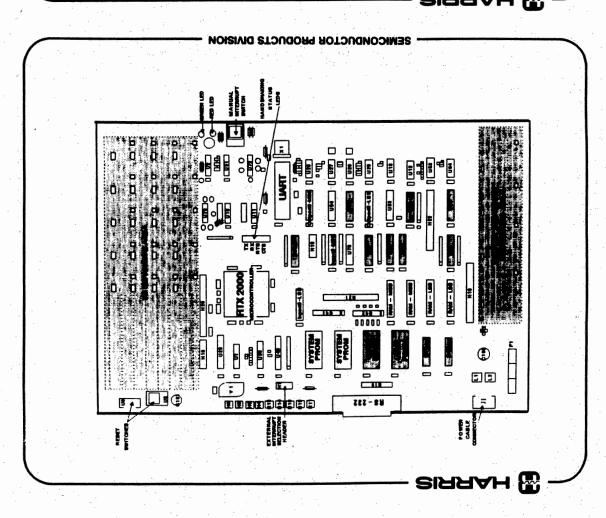

REAL TIME EXPRESS DEVELOPMENT BOARD

( RTXDB )

TIM DWYER LEAD ENGINEER HARDWARE SUPPORT DEVELOPMENT

SEMICONDUCTOR PRODUCTS DIVISION

#### OVERVIEW

- O FEATURES

- O BLOCK DIAGRAM

- O HEMORY HAP

- o I/O PORTS

- O SERIAL PORT

- O PROTOTYPE AREAS

- O BOARD OPERATION

#### FEATURES

- O BASED ON THE HARRIS RTX2000 PROCESSOR

- O FLEXIBLE AND EXPANDABLE

- O 16K BY 16 ZERO WAIT STATE STATIC RAM

- O 8K BY 16 SYSTEM PROM

- O UP TO 8K BY 16 USER PROM

- O 16-BIT INPUT AND OUTPUT PORTS

- O HIGH SPEED SERIAL PORT

- O PROTOTYPE AREAS

Real Time Express Development Board

3 of 11

MEMORY MAP

| . i        | QUADRANT 1 |        |                 | QUADRANT 2 |        |        |            | Q      | UADF   | ANT    | 3 _     | Q            | 4 512K  |         |         |         |

|------------|------------|--------|-----------------|------------|--------|--------|------------|--------|--------|--------|---------|--------------|---------|---------|---------|---------|

|            | FIR        |        | UR PA<br>DECODI |            |        | i      | <b>i</b> . | i      |        | i      | ļ ·     | PAGE - JEK W |         | i       |         | WORDS   |

|            |            |        |                 |            |        |        |            |        | !      |        |         | 0908         |         |         | 1       |         |

| - K BITS → | PAGE •     | PAGE 1 | PAGE 2          | PAGE 1     | PAGE 4 | PAGE 6 | PAGE •     | PAGE 7 | PAGE 8 | PAGE 1 | PAGE 10 | PAGE 11      | PAGE 12 | PAGE 13 | PAGE 14 | PAGE 15 |

Real Time Express Development Board

5 of 11

- SEMICONDUCTOR PRODUCTS DIVISION -

### HARRIS

MEMORY MAP, PAGE ZERO

| OFFFE  |                                         |

|--------|-----------------------------------------|

|        | INSTALLED RAM                           |

|        | ( 16K WORDS )                           |

|        | PROVIDED FOR<br>APPLICATION<br>SOFTWARE |

| 08300- | RESERVED FOR                            |

| 08000  | SYSTEM USE                              |

| 07FFE  |                                         |

|        | RESERVED FOR                            |

|        | USER PROM                               |

| 04000  | ( SK WORDS )                            |

| 03FFE  | SYSTEM PROM                             |

|        | ( 8K WORDS )                            |

| 00000  | (TARGET MONITOR)                        |

Real Time Express Development Board

6 of 11

#### I/O PORTS

- O THREE 16 BIT OUTPUT PORTS (LATCHED)

- O THREE 16 BIT INPUT PORTS (SAMPLED)

Real Time Express Development Board

7 of 13

- SEMICONDUCTOR PRODUCTS DIVISION -

#### SERIAL PORT

- O STANDARD BAUDRATES UP THRU 19,200 BAUD

- O STATUS LEDS FOR DATA AND HANDSHAKE SIGNALS

- O HEADER ALLOWS CONNECTOR PINOUT TO BE CHANGED

Real Time Express Development Board

8 of 11

#### PROTOTYPE AREAS

- O ALLOWS RTXDB TO BE USED AS FOUNDATION FOR USERS PROTOTYPE

- O ALLOWS EXPANSION OF RTXDB

- O 20% OF TOTAL BOARD AREA

- O MEMORY AREA

- O HEADER WITH MEMORY ADDRESS, DATA, AND CONTROL SIGNALS

- O UP TO FOUR 28-PIN DEVICES

- O ASIC BUS AREA

- O HEADER WITH G ADDRESS, DATA AND CONTROL SIGNALS

- O 24 BY 28 ARRAY OF PLATED HOLES FOR PIN GRID ARRAY AND OTHER PACKAGE TYPES

- O DUAL INLINE PACKAGE (DIP) AREA FOR STANDARD LOGIC IN DIPS

Real Time Express Development Board

9 of 1

- SEMICONDUCTOR PRODUCTS DIVISION

#### BOARD OPERATION

- O GREEN LED

- O POWER ON, FUSE INTACT

- O RESET SWITCH

- O RTX2000, 82C50A, PARALLEL OUTPUT PORTS

- O RED LED

- O BLINKING AFTER RESET, RTXDB WAITING FOR HOST TO ESTABLISH COMMUNICATION

- O OM RTXDB WAITING FOR A COMMAND FROM THE HOST

- O OFF RTXDB IS EXECUTING INSTRUCTIONS

- O RS232 CONNECTOR

- O POWER CONNECTOR

TFORTH COMPILER

- SEMICONDUCTOR PRODUCTS DIVISION -

#### TFORTH COMPILER

- O FORTH-83 COMPATIBLE

- O CROSS-COMPILES TO RTX MACHINE CODE

- O OPTIMIZES FOR RTX ARCHITECTURE

- O DESIGNED TO SUPPORT EMBEDDED CONTROL SYSTEMS

HEADERLESS CODE

DEBUGGING SUPPORT

TForth - 1

#### TFORTH FEATURES

- O DIRECTIVES CONTROL COMPILER ENVIRONMENT

- O COMPILES IN SEPARATE BLOCKS TO SUPPORT INTERRUPTS, VECTOR TABLES, ETC.

- O PROVISIONS FOR GENERATING CUSTOM RTX INSTRUCTIONS

E842 UCODE @2+ => DUP @ SWAP 2+

- O CAN BE USED INTERACTIVELY FROM HOST MONITOR

TF: : - 2

- SEMICONDUCTOR PRODUCTS DIVISION -

#### TFORTH MEMORY STRUCTURE

- O COMPILES CODE INTO PC MEMORY SEGMENT

- O MAINTAINS HEADERS IN SEPARATE TARGET DICTIONARY

#### TFORTH MEMORY MAP

PC Memory

Target memory

TForth - 4

- SEMICONDUCTOR PRODUCTS DIVISION

#### COMPILER DIRECTIVES

- O ALL DIRECTIVES HAVE DEFAULTS, SOME CONFIGURABLE

- O COMPILER INVOCATION

START-TFORTH TURNS COMPILER ON END-TFORTH TURNS COMPILER OFF

- O MEMORY CONFIGURATION

RAM-ONLY ALL RAM

RAM/ROM SEPARATE MEMORY SPACES

- O MEMORY ADDRESSING

ROMORG SET CODE ADDRESS

RAMORG SET DATA ADDRESS

TForth - 5

#### TFORTH EXAMPLE

```

\ TFORTH Example 1

\ Calculates 2a + b - c

START-TFORTH

HEX 0000 ROMORG

: WORD1 (abc -- res)

- SWAP DUP + +;

: WORD2 2 3 4 WORD1;

END-TFORTH

```

TForth - 6

- SEMICONDUCTOR PRODUCTS DIVISION

#### DISASSEMBLER

- O DECOMPILES RTX CODE TO FORTH PRIMITIVES

- O USEFUL FOR INSTRUCTION SEQUENCING AND TIMING

TForth - 7

#### DISASSEMBLER INVOCATION

- ADDR COUNT DASM

- Ö ADDR DASM; DISASSEMBLES ONE WORD

- **FULL DASM** DISASSEMBLES ALL COMPILED CODE

TForth - 8

- SEMICONDUCTOR PRODUCTS DIVISION

#### DISASSEMBLER EXAMPLE

Harris Semiconductor RTXDS Disassembler V1.0 06/10/88 07:38 class.scr Page 1 Address Opcode Operations : WORD1 AC40 AE80 AOC0 A840 A860 0000 0002 SWAP 0004 0006 0008 DUP : WORD2 BE42 BE43 BE44 0000 000A LIT 02 LIT 03 LIT 04 WORD1 000C

Call 0000

1...

TForth - 9

000E 0010 0012

A020

#### RTX EXTENSIONS

- O REGISTERS AND PERIPHERALS

IBCO READS INTERRUPT BASE/CONTROL REGISTER

TC1! WRITES VALUE TO TIMER/COUNTER 1

- O INTERRUPTS

DIRECTIVES FOR GENERATING VECTOR TABLES

SOFTINT SOFTWARE INTERRUPT

- O ASIC BUS

G G0 READS DATA FROM PORT G

N G G! WRITES DATA TO PORT G

TForth - 10

- SEMICONDUCTOR PRODUCTS DIVISION

#### **OPTIMIZATION**

- O COMBINES SUBROUTINE RETURN WITH LAST WORD OF DEFINTION

- O COMBINES ALU AND SHIFT OPERATIONS WITH PREVIOUS INSTRUCTION

3 +

O COMBINES STACK OPERATIONS

SWAP DROP => NIP

#### OPTIMIZATION EXAMPLE

\ Optimization example

START-TFORTH

HEX 0000 ROMORG

: WORD3 2 SWAP - SWAP DROP DUP;

: WORD4 18 G@ +;

END-TFORTH

0000 : WORD3

BCC2 LIT 02 SWAP 0002 A0A0 SWAP DROP DUP ;

0004 : WORD4

B8B8 18 G@ + ;

TForth - 12

- SEMICONDUCTOR PRODUCTS DIVISION .

#### DEBUG SUPPORT

- O TERMINAL I/O SUPPORTED THROUGH TARGET MONITOR

." EMIT KEY

- O CONDITIONAL COMPILATION

SMAP {{ ." Executing READ-DATA. Stack: " .S }} 2\*

- O MEMORY ACCESS TRACE

ALL MEMORY REFERENCES (0 ! C0 C!) ARE ROUTED THROUGH THE MONITOR

TForth - 13

#### A HARRIS

#### FILE INTERFACE

- WRITE-HEX FILENAME GENERATES INTEL HEX FILE

- WRITE-IMAGE FILENAME GENERATES OBJECT FILE

- READ-IMAGE FILENAME READS IMAGE FILE

- READ-HEX FILENAME READS HEX FILE

- FTYPE FILENAME SIMILAR TO DOS TYPE COMMAND

- FDUMP FILENAME HEX/ASCII DUMP

TForth - 14

SEMICONDUCTOR PRODUCTS DIVISION

#### HARRIS

#### EXERCISE

Write a program which flashes "SOS" in Morse code on the LED on the front of the Box. OBJECT:

THE LED is turned on by writing 8000H to port 18H:  $8000\ 18\ Gl$ HINTS:

> THE LED IS TURNED OFF BY WRITING OOOOH TO THE PORT. SOS IS 3 SHORT FLASHES, FOLLOWED BY 3 LONG FLASHES, FOLLOWED BY 3 SHORT FLASHES

GENTLEMEN, START YOUR CODE AT 8300H:

#### IF YOU HAVE TIME

WRITE THE FOLLOWING SO THAT THEY MAY BE COMPILED WITH EITHER PC/FORTH on TFORTH.

- 2. WRITE A PROGRAM TO CALCULATE N! FOR ANY N, 0 <= N <= 8