#### TABLE OF CONTENTS

| 1.0 |     | oductio      |              |                                         | . 3 |

|-----|-----|--------------|--------------|-----------------------------------------|-----|

|     | 1.1 | The <b>R</b> | RTX 2000,    | 2001A, And 2010 Microcontrollers        | . 3 |

|     | 1.2 | The R        | RTX 2000 H   | Family Programmer's Reference Manual    | . 5 |

|     |     |              |              |                                         |     |

| 2.0 | RTX | K Archi      | itecture     |                                         | . 9 |

|     | 2.1 | On-Cl        | hip Stacks   |                                         | 11  |

|     |     | 2.1.1        | The Para     | meter Stack                             | 11  |

|     |     | 2.1.2        | The Retu     | rn Stack                                | 11  |

|     | 2.2 | RTX :        | 2000 Series  | s Bus Architecture                      | 12  |

|     |     | 2.2.1        | Data Buse    | es                                      | 12  |

|     |     | 2.2.2        | Address I    | Buses                                   | 13  |

|     | 2.3 | Regist       | ers          | · · · · · · · · · · · · · · · · · · ·   | 14  |

|     |     | 2.3.1        | Stack Rel    | lated Registers                         | 14  |

|     |     | 2.3.2        | Status/Co    | ontrol Registers                        | 14  |

|     |     | 2.3.3        | Internal P   | Processor Registers                     | 14  |

|     | 2.4 | Memo         | ory          |                                         | 15  |

|     |     |              |              |                                         |     |

| 3.0 |     | rations      | • • • • • •  | • • • • • • • • • • • • • • • • • • • • | 19  |

|     |     |              |              | ution                                   | 19  |

|     |     | Stack        | Operation    |                                         | 21  |

|     | 3.3 | Subro        | utine Calls  | and Returns                             | 22  |

|     | 3.4 | Brancl       | hing And L   | .ooping                                 | 23  |

|     | 3.5 | Stream       | ned Instruct | tions                                   | 24  |

|     | 3.6 | Math/        | Logic Oper   | rations                                 | 25  |

|     |     | 3.6.1        | Registers    | And I/O Devices                         | 26  |

|     |     | 3.6.2        |              | • • • • • • • • • • • • • • • • • • • • | 26  |

|     |     | 3.6.3        | Literals     | • • • • • • • • • • • • • • • • • • • • | 26  |

|     | 3.7 | Stack        | Operations   | ••••••••••••••••••••••••••••••••••••••• | 27  |

|     |     | 3.7.1        | DUP          |                                         | 27  |

|     |     | 3.7.2        | SWAP .       | • • • • • • • • • • • • • • • • • • • • | 28  |

|     |     | 3.7.3        | DROP .       |                                         | 28  |

|     |     | 3.7.4        | OVER .       | • • • • • • • • • • • • • • • • • • • • | 29  |

|     |     | 3.7.5        | >R           | • • • • • • • • • • • • • • • • • • • • | 29  |

|     |     | 3.7.6        | R>           | • • • • • • • • • • • • • • • • • • • • | 30  |

|     |     | 3.7.7        | RØ           | • • • • • • • • • • • • • • • • • • • • | 30  |

|     | 3.8 | Interru      | pts          | • • • • • • • • • • • • • • • • • • • • | 31  |

|     |     | 3.8.1        | Maskable     | Interrupts                              | 31  |

|     |     | 3.8.2        | Non-Mask     | cable Interrupts (NMI)                  | 31  |

|     |     |              | 3.8.2.1      | On the RTX 2000                         | 31  |

|     |     |              | 3.8.2.2      | On the RTX 2001A                        | 32  |

|     |     |              | 3.8.2.3      | On the RTX 2010                         | 32  |

| RTX Registers                                         | . 35         |

|-------------------------------------------------------|--------------|

| 4.1 Stack Related Registers                           | . 39         |

| 4.1.1 TOP Register (Parameter Stack)                  | . 39         |

| 4.1.2 NEXT Register (Parameter Stack)                 | . 39         |

| 4.1.3 I Register (Return Stack)                       | . 40         |

| 4.1.3.1 I At Address 00H                              | . 41         |

| 4.1.3.2 I At Address 01H                              | . 41         |

| 4.1.3.3 I At Address 02H (Stream Count/Loop Count)    | . 42         |

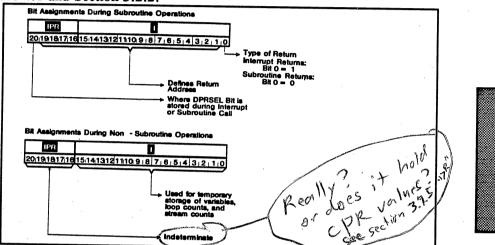

| 4.1.4 IPR Register (Return Stack)                     | . 43         |

| 4.2 Internal Processor Registers                      | . 44         |

| 4.3 Control/Status Registers                          | 45           |

| 4.3.1 The Configuration Register - Address 03H        | . 46         |

| 4.3.2 The MD Register - Address 04H                   | . 47         |

| 4.3.2.1 MD On The RTX 2000 and RTX 2010               | . 48         |

| 4.3.2.2 MD On The RTX 2001A                           | . 48         |

| 4.3.3 The SQ Register - Address 05H                   | . 40<br>. 49 |

| 4.3.4 The SR Register - Address 06H                   | . 49<br>. 49 |

| 4.3.5 The PC Register - Address 07H                   | . 49         |

| 4.3.6 The Interrupt Mask Register, IMR - Address 08H  | . 50         |

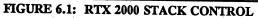

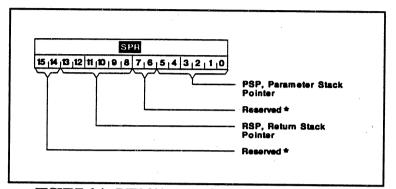

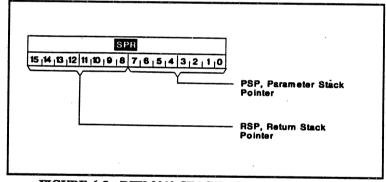

| 4.3.7 The Stack Pointer Register, SPR - Address 09H   | . 51         |

| 4.3.8 Address OAH                                     | . 52         |

| 4.3.8.1 On The RTX 2000                               | 52           |

| 4.3.8.2 On The RTX 2001 A and RTX 2010                | 52           |

| 4.3.9 Address 0BH: IVR, SVR, And SLR                  | . 52         |

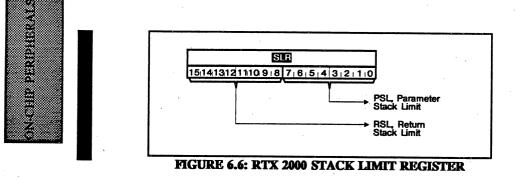

| 4.3.9.1 Write-only On The RTX 2000: SLR               | 53           |

| 4.3.9.2 Write-only On The RTX 2000: SLR               | . 53         |

|                                                       | 53           |

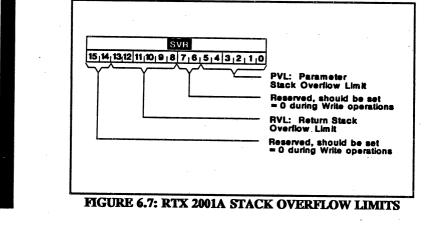

| 4.3.9.3 Write-only On The RTX 2010: SVR               | . 54         |

| 4 3 11 Data Dage Pagister DDD Address ODI             | 55           |

| 4.3.11 Data Page Register, DPR - Address ODH          | 56           |

| 4.3.12 User Page Register, UPR - Address OEH          | 56           |

| 4.3.13 Code Page Register, CPR - Address OFH          | 56           |

| 4.3.14 Interrupt Base/Control Register - Address 10H  | 57           |

| 4.3.15 Oser Dase Register, ODR - Address 11H          | 57           |

| 4.3.16 Address 12H                                    | 58           |

|                                                       | 58           |

| 4.3.16.2 On The RTX 2010: MXR                         | 58           |

| 4.3.18 Timer/Counter 1 - Address 13H                  |              |

| $4.3.10$ Timer/Counter 2 Address 14 $\Pi$             | 59           |

| 4.3.19 Timer/Counter 2 - Address 15H                  | 59           |

| 4.3.20 Address 16H                                    | 60           |

|                                                       | 60           |

| 4.3.20.2 RTX 2001A - RX, Scratchpad/Counting Register |              |

| 4.3.20.3 RTX 2010 - MLR                               | 60           |

| 4.3.21 Address 17H                                    | 61           |

| 4.3.21.1 RTX 2000 - MHR                               | 61           |

| 4.3.21.2 RTX 2001A - RH                               | 61           |

| 4.3.21.3 RTX 2010 - MHR                               | 61           |

4.0

|          |     |                    | •                                                                                       |                                   |                       |      |   |   |       |

|----------|-----|--------------------|-----------------------------------------------------------------------------------------|-----------------------------------|-----------------------|------|---|---|-------|

|          |     | •                  |                                                                                         |                                   |                       |      |   |   |       |

|          | •   |                    |                                                                                         |                                   |                       |      | · |   |       |

|          | 5.0 | TA ID TA           | •                                                                                       |                                   |                       |      |   |   | •     |

| <u>.</u> | 5.0 | External Bus Int   |                                                                                         |                                   | • • • • • • • • • •   | 65   |   |   |       |

|          |     | 5.1 ASIC Bus       | Interface                                                                               |                                   | • • • • • • • • • •   | 66   |   |   |       |

| 1        |     | 5.1.1 RT           | K 2000 and RTX 2001A                                                                    | A Extended Cycle Operation        | ation                 | 67   |   |   |       |

|          |     | 5.1.2 RT           | X 2010 Extended Cycle                                                                   | Operation                         |                       | 68   |   |   |       |

|          |     | 5.2 Memory In      | terface                                                                                 |                                   |                       | 69   |   |   |       |

|          |     | 5.2.1 Cod          | e Memory Space                                                                          |                                   |                       | 71   |   |   |       |

|          |     | 5.2.               | 1.1 Subroutine Calls                                                                    | s and Returns                     |                       | 71   |   |   | · · · |

|          |     | 5.2.               |                                                                                         | • • • • • • • • • • • • • • • •   |                       | 73   |   |   |       |

|          |     | 5.2.2 Data         | Memory Space                                                                            |                                   |                       | 74   |   |   |       |

|          |     | 5.2.               | 2.1 Memory Page S                                                                       | election                          | •••••                 | 74   |   |   |       |

|          |     | 5.2.               | 2.2 Memory Access                                                                       | Mode Selection                    | •••••••••             |      |   |   |       |

|          |     | 5.2.               |                                                                                         | Examples                          | ••••••••••            |      |   |   |       |

|          |     |                    | Memory Space                                                                            | Drampies                          | •••••                 | 76   |   |   |       |

|          |     | 51215 060          | Wembry Space                                                                            | • • • • • • • • • • • • • • • •   | • • • • • • • • • •   | 80   |   |   |       |

|          | 6.0 | On-Chin Perinhe    | rale                                                                                    |                                   |                       |      |   |   |       |

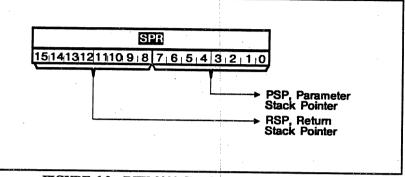

|          | 0.0 | 6 1 Stock Contr    | rals                                                                                    | • • • • • • • • • • • • • • • •   | •••••                 | 85   |   |   |       |

|          |     | 6 1 1 Stack Collin | ollers                                                                                  | • • • • • • • • • • • • • • • • • | ••••                  | 85   |   |   |       |

|          |     | 6.1.1 Stac         | k Pointer Operation                                                                     |                                   | ••••                  | 86   |   |   |       |

|          |     | 6.1.               | 1.1 Stack Pointers F                                                                    | or the RTX 2000                   | • • • • • • • • • • • | 87   |   |   |       |

|          |     | 6.1.               | 1.2 RTX 2001A and                                                                       | RTX 2010 Stack Point              | ters                  | 89   |   |   |       |

|          |     | 6.1.2 Stac         | k Limit Operation                                                                       | • • • • • • • • • • • • • • • •   | • • • • • • • • • •   | 91   |   |   |       |

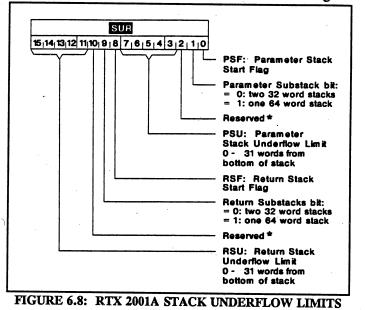

|          |     | 6.1.               | 2.1 Stack Limits For                                                                    | the RTX 2000                      | • • • • • • • • • • • | 91   |   |   |       |

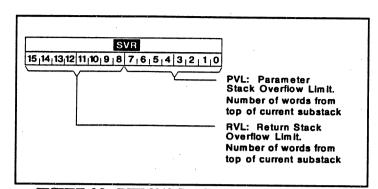

|          |     | 6.1.               |                                                                                         | the RTX 2001A                     | • • • • • • • • • •   | 92   |   |   |       |

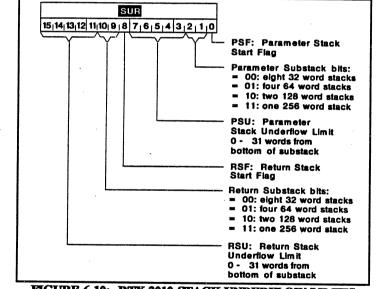

|          |     | 6.1.               | 2.3 Stack Limits For                                                                    | the RTX 2010                      | • • • • • • • • • •   | 93   |   |   |       |

|          |     | 6.1.3 Con          | figuration Of Substacks                                                                 | • • • • • • • • • • • • • • •     | •••••                 | 95   |   |   |       |

|          |     | 6.1.               | 3.1 Substack Config                                                                     | uration On The RTX 20             | 001A                  | 95   |   |   |       |

|          |     | 6.1.               | 3.2 Substack Configu                                                                    | uration On The RTX 20             | 010                   | 98   |   |   |       |

|          |     | 6.1.4 Stac         | k Error Conditions                                                                      |                                   |                       | 102  |   |   |       |

|          |     | 6.1.4              | 4.1 RTX 2001A and                                                                       | RTX 2010 Fatal Stack              | Errors                | 102  |   |   |       |

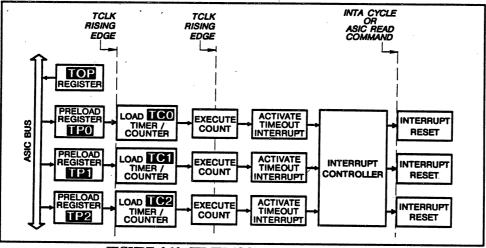

|          |     | 6.2 Interrupt Co   | ntroller                                                                                |                                   |                       | 102  |   |   |       |

| ļ        |     | 6.2.1 Inter        | rupt Acknowledgement                                                                    |                                   | •••••                 | 105  |   |   |       |

| .'       |     | 6.2.2 Disa         | bling Interrupts                                                                        |                                   | • • • • • • • • •     | 107  |   |   |       |

|          |     | 6.2.3 Soft         | vare Interrupt                                                                          | ••••••                            | •••••                 |      |   |   |       |

|          | 1   | 6.3 On-Chin Ha     | rdware Math Support .                                                                   | ••••••                            | ••••                  | 109  |   |   |       |

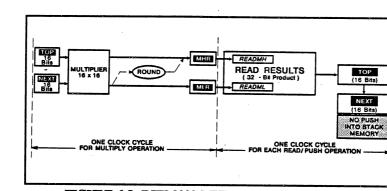

|          |     | 6.3.1 RTX          | 2000 Multiplier Opera                                                                   | ••••••••••••••••                  | • • • • • • • • •     | 110  |   |   |       |

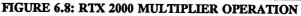

|          | · · | 6.3.2 RTX          | 2010 Hardware Moth                                                                      |                                   | • • • • • • • • •     | 110  |   |   |       |

|          |     | 6.3.2              | 2010 Hardware Math                                                                      |                                   | •••••                 | 113  |   |   |       |

|          |     | 6.3.2              | $\begin{array}{ccc} 1 & \text{KIA 2010 Multi} \\ 1 & \text{DTV 2010 Deces} \end{array}$ | plier/Accumulator Oper            | ration                | 113  |   |   |       |

|          |     | 6.4 Counter/Tim    |                                                                                         | 1 Shifter and LZD Open            | ration                | 115  |   |   |       |

|          |     |                    |                                                                                         | ••••••                            | • • • • • • • • • •   | 116  |   |   |       |

|          |     | 0.4.1 Cour         | ter/Timer Operation .                                                                   | • • • • • • • • • • • • • •       | •••••                 | 116  |   |   |       |

|          |     | 0.4.2 Cour         | ter/Timer Interrupts .                                                                  | •••••                             | • • • • • • • • • •   | 117  |   |   |       |

|          |     | 0.4.3 Cloc         | k Selection                                                                             |                                   | • • • • • • • • • •   | 118  |   |   |       |

|          |     |                    |                                                                                         |                                   |                       |      |   |   |       |

|          |     |                    |                                                                                         |                                   |                       | - A. |   |   |       |

|          |     |                    |                                                                                         |                                   | · · ·                 |      |   | 1 |       |

|          |     |                    |                                                                                         | ·                                 |                       |      |   |   |       |

|          |     | ·<br>•             |                                                                                         |                                   |                       |      |   |   |       |

|          |     |                    |                                                                                         |                                   |                       |      |   |   |       |

|          |     | -                  |                                                                                         |                                   |                       |      |   |   |       |

|     | •           |                                              |                    |   |     |

|-----|-------------|----------------------------------------------|--------------------|---|-----|

|     |             |                                              | ,                  |   |     |

| 7.0 | Instruction | Sat                                          |                    |   |     |

| 1.0 | 7 1 Gama    | Set                                          | 121                |   | e.  |

|     | 7.1 Gener   | ral Information                              | 121                |   | - ( |

|     | 7.1.2       |                                              | 122                |   |     |

|     | 7.2 Form    |                                              | 122                |   |     |

|     |             | utine Call                                   | 123<br>127         |   |     |

|     | 7.4 Subro   | utine Return                                 | 127                |   |     |

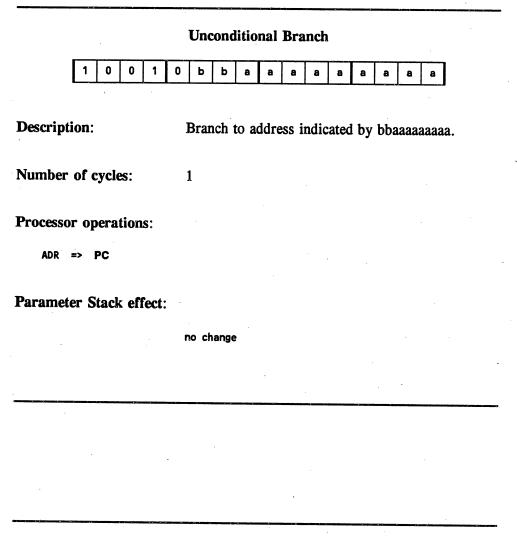

|     | 7.5 Class   | es 8 and 9: Branches and Loops               | 128<br>1 <b>29</b> |   |     |

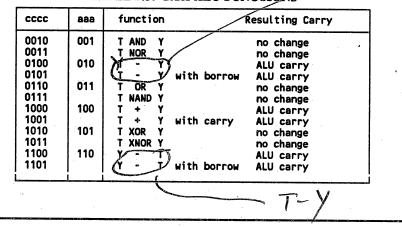

|     | 7.6 Class   | 10: ALU Operations                           | 129                |   |     |

|     | 7.6.1       |                                              | 130                |   |     |

|     | 7.6.2       | Shift Operations                             | 137                |   |     |

|     |             | ceed Processor-Specific Operations           | 158                |   |     |

|     | 7.7.1       | Streamed MAC Instructions On The RTX 2010    | 182                |   |     |

|     | =           | 11-a : ASIC Bus Access                       | 182                |   |     |

|     | 7.8.1       |                                              | 184                |   |     |

|     |             | Predefined ASIC Bus Instructions             | 191                |   |     |

|     | 7.9 Class   | 11b - Short Literals                         | 196                |   |     |

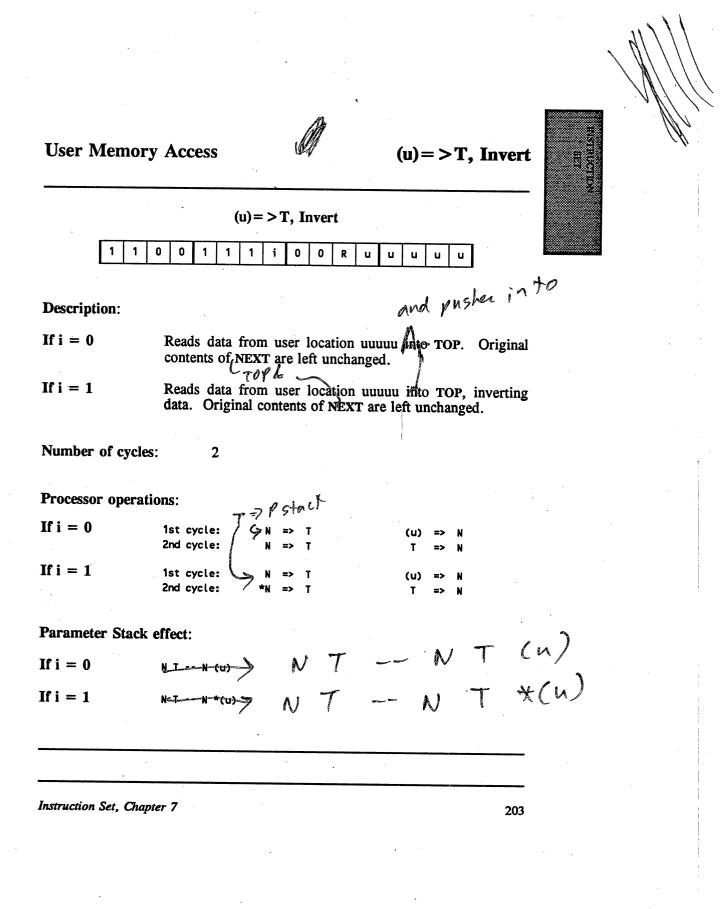

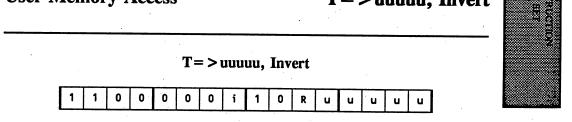

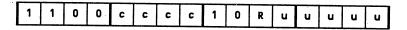

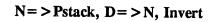

|     | 7.10        | Class 12: User Memory Access                 | 201                |   |     |

|     | 7.11        | Class 13: Long Literals                      | 208                |   |     |

| ,   | 7.12        | Classes 14 and 15: Data Memory Access        | 214                |   |     |

|     | 7.13        | Undefined Opcodes                            | 227                |   |     |

|     |             |                                              |                    |   |     |

| 8.0 |             | Functions                                    | 225                |   |     |

|     |             | uction                                       | 225                |   |     |

|     | 8.1.1       | Step Math Using The RTX 2000                 | 225                |   |     |

|     | 8.1.2       | Step Math Using The RTX 2001A                | 226                |   |     |

|     | 8.1.3       | Step Math Using The RTX 2010                 | 226                |   |     |

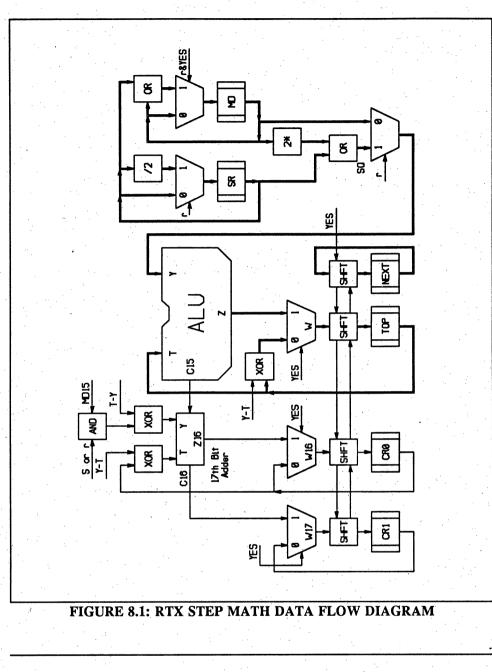

|     | 8.2 Data I  | Flow in Step Math                            | 227                |   |     |

|     | 8.3 17-Bit  | Math                                         | 229                |   | 1 P |

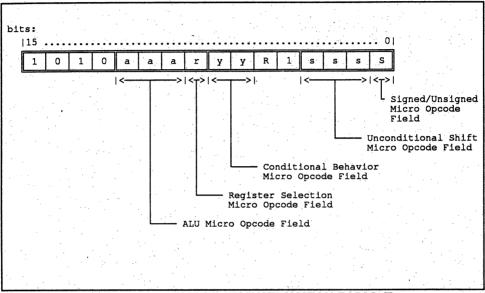

|     |             | tep Math Instruction Format                  | 230                |   | { . |

|     | 8.4.1       | ALU Micro Opcode Field (aaa)                 | 231                |   |     |

|     | 8.4.2       | Register Selection Micro Opcode Field (r)    | 232                |   |     |

|     | 8.4.3       | Conditional Behavior Micro Opcode Field (yy) | 233                |   |     |

|     | 8.4.4       |                                              | 234                |   |     |

|     | 846         | Unconditional Shift Micro Opcode Field (sss) | 235                |   |     |

|     | 8.5 Operat  | Signed/Unsigned Micro Opcode Field (S)       | 236                |   |     |

|     | 8.6 Interru | apting Step Math Operations                  | 237                |   |     |

|     | 8.7 Some    | Useful Opcodes                               | 238                |   |     |

|     | 8.8 Sten M  | fultiplication                               | 239                | • | ć   |

|     | 8.8.1       | Signed Step Multiplication                   | 240<br>240         |   |     |

|     | 8.8.2       | Mixed Sign Multiplication Type A             | 240                |   |     |

|     | 8.8.3       | Unsigned Multiplication                      | 242                |   |     |

|     | 8.8.4       | Mixed Sign Multiplication Type B             | 243                |   |     |

|     |             | vivision                                     | 244<br>245         |   |     |

|     | 8.9.1       | Standard Division Program                    | 245<br>248         |   |     |

|     | 8.9.2       | Alternate Division Program                   | 248                |   |     |

|     |             |                                              | 270                |   |     |

| 8.10 | Step Square Root                   |

|------|------------------------------------|

| 8.11 | Step Bit Reversal                  |

| 8.12 | Step Cyclic Redundancy Check (CRC) |

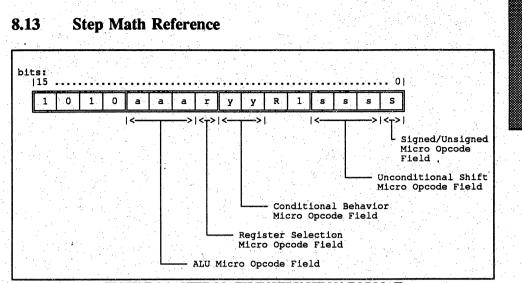

| 8.13 | Step Math Reference                |

•

. 1 ŀ,

. ب

## CHAPTER 1

INTRODUCITO

1

## INTRODUCTION

Introduction, Chapter 1

RTX 2000 Family Programmer's Reference Manual

#### **1** Introduction

The Harris Real Time Express (RTX) 2000 Family of microcontrollers is a highly integrated family of 16-bit CMOS microcontrollers designed for real-time control systems requiring high performance with low power consumption.

### 1.1 The RTX 2000, 2001A, And 2010 Microcontrollers

The architecture of the RTX 2000 Series of products results in high instruction execution rates. The highly parallel architecture allows the RTX to perform several functions in one instruction cycle, and all instructions execute in either one or two clock cycles. Instructions are fetched from memory and executed immediately; there are no instruction "pipelines" or caches to flush when performing branches or calls.

The RTX 2000, 2001A and 2010 Microcontrollers have on-chip support hardware for performing many of the functions typically needed in a real-time system, including an interrupt controller, a memory page controller, two stack controllers, and three 16-bit counter/timers. In addition to these "on-chip peripherals", the RTX 2000 provides a 16-by-16 hardware multiplier, while the RTX 2010 provides a 16-by-16 hardware multiplier-accumulator along with a 32bit Barrel Shifter and a 32-bit Leading Zero Detector for Floating Point support. Table 1.1 shows a break-out of the features of each of these products.

The RTX 2000 Class architecture was designed to execute the high-level language Forth as its "assembly language". The instruction set provides the features necessary for implementing much of the Forth language directly. Instructions are available for manipulating stacks, performing memory access, controlling program flow, and basic math and logic operations.

One RTX instruction may combine the functions of two or three high level Forth instructions, resulting in an effective processor throughput which is faster than the processor clock speed.

Introduction, Chapter 1

The stack oriented architecture of the RTX also makes it well suited for running such computer languages as C.

| <u>RTX 2000</u> | <u>RTX 2001A</u> | <u>RTX 2010</u> |

|-----------------|------------------|-----------------|

| Interrupt       | Interrupt        | Interrupt       |

| Controller      | Controller       | Controller      |

| Stack           | Stack            | Stack           |

| Controller      | Controller       | Controller      |

| Two 256-Word    | Two 64-Word      | Two 256-Word    |

| Stacks          | Stacks           | Stacks          |

| Three 16-Bit    | Three 16-Bit     | Three 16-Bit    |

| Timer/Counters  | Timer/Counters   | Timer/Counters  |

| 1-Cycle 16-Bit  |                  | 1-Cycle 16-Bit  |

| Multiplier      |                  | Mult./Accum.    |

|                 |                  | 1-Cycle 32-Bit  |

|                 |                  | Barrel Shifter; |

|                 |                  | Floating Point  |

| <b>.</b>        | ,                | Support         |

RTX 2000 Family Programmer's Reference Manual

### 1.2 The RTX 2000 Family Programmer's Reference Manual

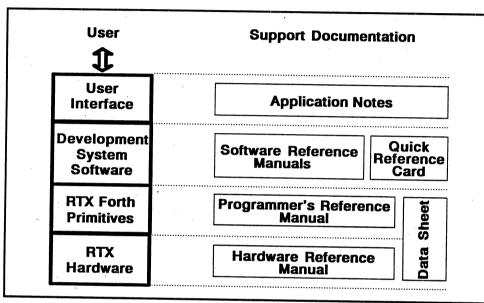

Figure 1.1 offers an overview of the interface between a user and an RTX Microcontroller. The documentation which supports each layer of this interface is also shown.

FIGURE 1.1: USER/RTX INTERFACE

Introduction, Chapter 1

The Programmer's Reference Manual describes the RTX 2000, RTX 2001A, and RTX 2010 Microcontrollers from a programmer's point of view, including architecture, registers, data paths, hardware interfaces, and primitive instructions. Topics described in various sections of this manual include:

Chapter 2 Overall architecture of RTX microcontrollers

Chapter 3 General operation of RTX microcontrollers

- Chapter 4 The RTX register set

- Chapter 5 Memory Interface

Chapter 6 On-chip Peripheral Devices

Chapter 7 RTX Instruction Set

Chapter 8 Implementation of Multi-step Math Functions

Chapter 9 Implementing Forth on the RTX

Chapter 10 Code Optimization Techniques

Some functional differences exist between the different members of this family of microcontrollers. When such differences exist, the applicable sections of this manual describe those differences. Where major differences exist, they are broken into separate paragraphs, and are offset with a side bar for clarification.

For additional information specific to your microcontroller, please refer to the appropriate data sheet.

RTX 2000 Family Programmer's Reference Manual

# ARCHITECTURE

## CHAPTER 2

## **RTX ARCHITECTURE**

RTX Architecture, Chapter 2

RTX 2000 Family Programmer's Reference Manual

#### 2 RTX Architecture

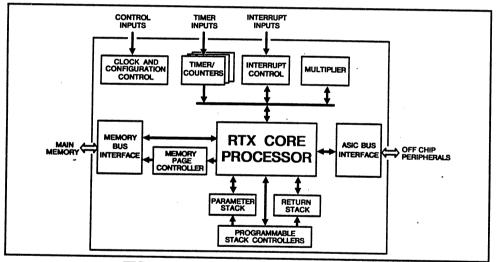

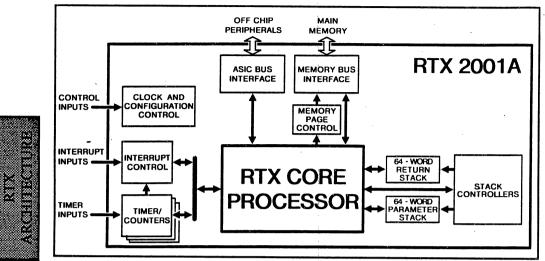

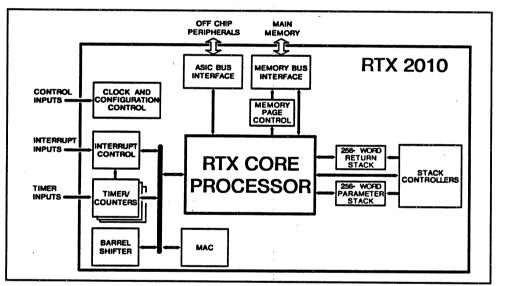

This chapter provides an overview of the programmer's model of the RTX Microcontroller architecture. Figures 2.1, 2.2 and 2.3 show block diagrams for the RTX 2000, RTX 2001A, and RTX 2010 Microcontrollers respectively.

The RTX microcontroller is a stack based machine with two on-chip stacks. Most math, I/O and memory reference operations take their operands from the Parameter Stack, and leave their results on the Parameter Stack. Subroutine calls use the Return Stack for saving their return addresses.

There are twenty-three registers on the RTX 2000, twenty-four registers on the RTX 2001A, and twenty-five registers on the RTX 2010. These registers control processor configuration and status, hold intermediate results during computations, and provide an interface between the processor and its on-chip peripheral devices.

RTY ARCHITECTURE

The RTX registers and stacks are interconnected through a series of 16-bit data buses which transfer data within the processor and with the outside world.

FIGURE 2.1: RTX 2000 BLOCK DIAGRAM

RTX Architecture, Chapter 2

FIGURE 2.2: RTX 2001A BLOCK DIAGRAM

FIGURE 2.3: RTX 2010 BLOCK DIAGRAM

RTX 2000 Family Programmer's Reference Manual

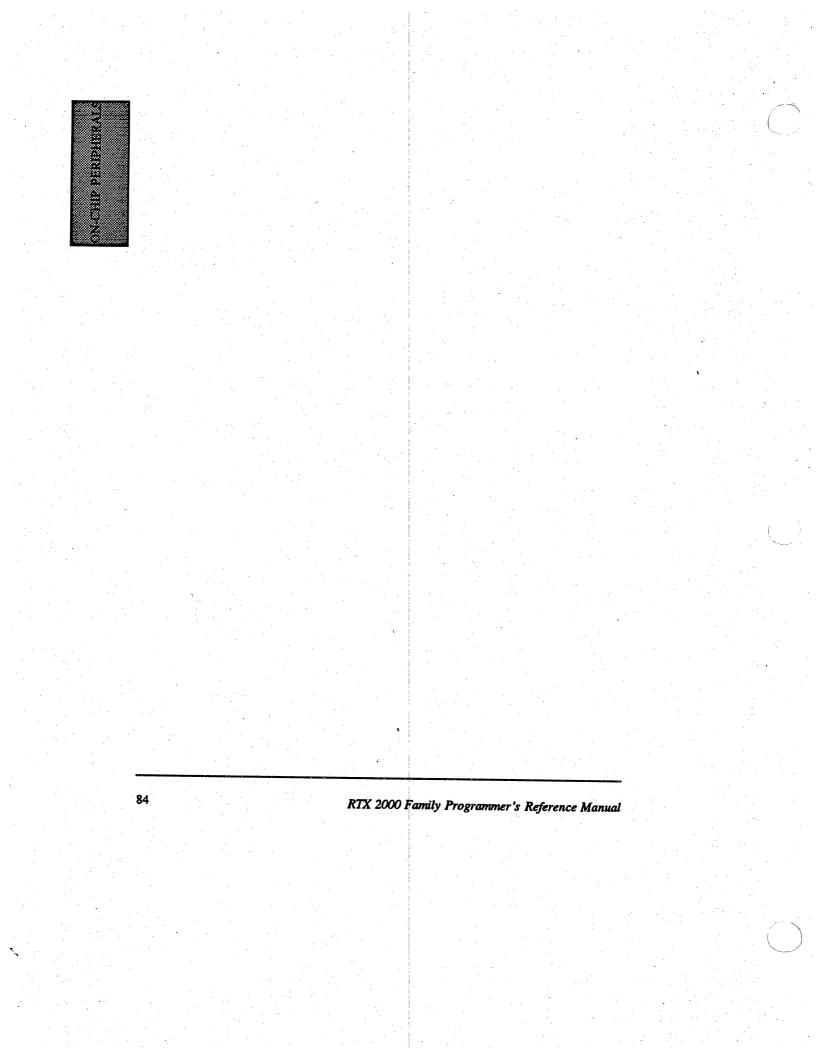

#### 2.1 On-Chip Stacks

The RTX microcontroller contains two on-chip last-in-first-out (LIFO) stack memories. The top elements of each stack are immediately accessible through registers. The remainder of each stack is located in on-chip RAM arrays. The control logic associated with each stack determines which stack locations are to be read or written, and monitors the stacks for overflow and underflow conditions. See Section 3.1 for a description of stack operations.

Stacks on the RTX 2000 and RTX 2010 are each 256 elements deep; stacks on the RTX 2001A are 64 elements deep.

#### 2.1.1 The Parameter Stack

The 16-bit wide Parameter Stack provides the operands for most math, logic, and memory reference instructions. It is used for passing parameters between subroutines, and as a scratchpad area for temporary storage of data.

The top two elements of the Parameter Stack are the TOP Register, which contains the top element, and the NEXT Register, which contains the second element. For certain instructions, TOP or NEXT are the implicit data source or destination, and the RTX can perform operations dealing with TOP and NEXT in one clock cycle. For more information about TOP and NEXT, see Chapter 4.

#### **2.1.2** The Return Stack

The 21-bit wide Return Stack is used for storing subroutine return addresses and for holding index counts for loops and repeated instructions, and can also be used as a temporary storage area. The top element of the Return Stack is comprised of the 16-bit wide I register and the 5-bit wide IPR Register. The RTX can move data between the top elements of the Parameter and Return Stacks in a single clock cycle. For more information about I and IPR, see Chapter 4.

RTX Architecture, Chapter 2

#### 2.2 RTX 2000 Series Bus Architecture

The RTX 2000 Series bus architecture provides for unidirectional data paths and simultaneous operation of some data buses. This parallelism allows for maximum efficiency of data flow. External data is transferred via the ASIC Data Bus and the Memory Data Bus. Addresses for external access are output via the Memory Address Bus and the ASIC Address Bus.

#### **2.2.1** Data Buses

The RTX QUAD  $Bus^{TM}$  architecture consists of 4 independent 16-bit data buses, all of which may be active simultaneously.

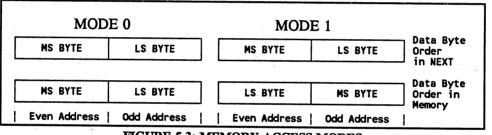

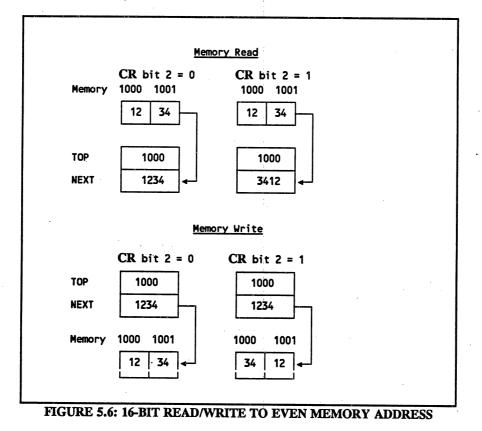

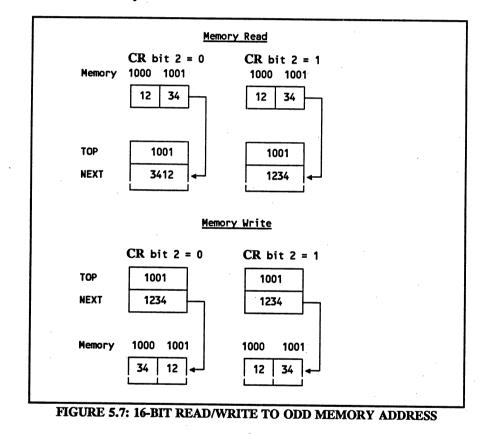

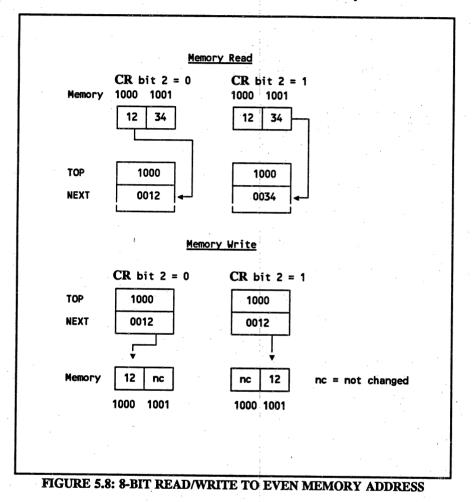

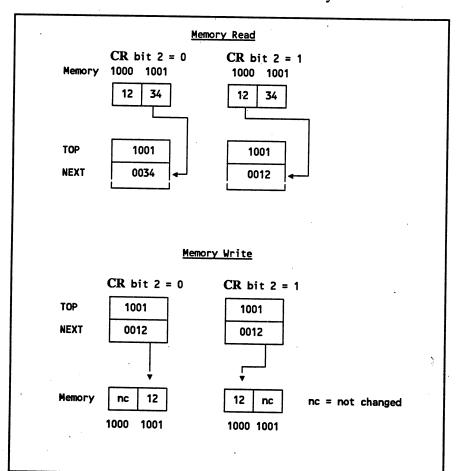

- The Memory Data Bus carries program instructions and program data to and from Main Memory. 16-bit data words (but not program instructions) are passed through byte-swapping hardware which allows the processor to control the order of storage in memory for the low and high bytes of the word.

- The ASIC Bus<sup>™</sup> is the I/O and register interface bus. This bus provides the interface between the Parameter Stack and the processor registers and external I/O devices. The ASIC Bus passes input data through the on-chip Arithmetic/Logic Unit (ALU) before pushing the data onto the Parameter Stack. This allows the RTX to perform math (adding, subtracting), logic (masking), and shifting operations on the data as it is being read.

- The **Parameter Stack Bus** carries data between the top-of-stack registers and the Parameter Stack RAM.

- The **Return Stack Bus** carries data between the top-of-stack registers and the Return Stack RAM.

RTX 2000 Family Programmer's Reference Manual

#### 2.2.2 Address Buses

For off-chip communications, the RTX microprocessor has two address buses: the 19-bit Memory Address Bus, and the 3-bit ASIC Address Bus.

- The Memory Address Bus (MA19-MA01) carries the address of the Main memory location to be accessed, either for instruction fetches or memory read/write operations. This is a 19-bit bus, along with Upper Data Strobe (UDS) and Lower Data Strobe (LDS), which allows the RTX to address 1 megabyte of memory.

- The ASIC Address Bus (GA02-GA00) carries address information for external ASIC devices.

See Chapter 5 for information about RTX External Bus Interfaces.

RTX Architecture, Chapter 2

#### 2.3 Registers

The RTX 2000 Series microcontrollers contain three types of registers. Stack related registers, Status/Control registers, and Internal Processor registers.

#### 2.3.1 Stack Related Registers

Stack related registers contain the top elements of the Parameter and Return Stacks. These registers are the implicit source and destination for many of the processor operations, and are described in detail in Chapter 4.

#### 2.3.2 Status/Control Registers

Status/Control registers are accessed through the ASIC Bus, and determine the operating environment for the processor by controlling the processor configuration and on-chip peripheral devices. These registers are described in detail in Chapter 4.

#### 2.3.3 Internal Processor Registers

Internal Processor registers are not directly accessible to the programmer, and are described in Chapter 4.

RTX 2000 Family Programmer's Reference Manual

#### 2.4 Memory

The RTX 2000, RTX 2001A, and RTX 2010 Microcontrollers directly address 1 Megabyte (512K 16-bit words) of memory. This memory is divided into 16 pages of 64K bytes (32K words) each, and may be made up of any combination of ROM, RAM, or memory mapped I/O devices.

The RTX memory interface is described in detail in Chapter 5.

RTX Architecture, Chapter 2

RTX 2000 Family Programmer's Reference Manual

## OPERATIONS

## CHAPTER 3 OPERATIONS

**Operations**, Chapter 3

RTX 2000 Family Programmer's Reference Manual

#### **3 Operations**

This chapter provides an overview of the internal processor operations. The operations are described in greater detail in Chapter 7, "Instruction Set".

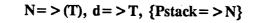

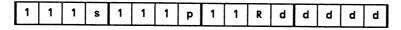

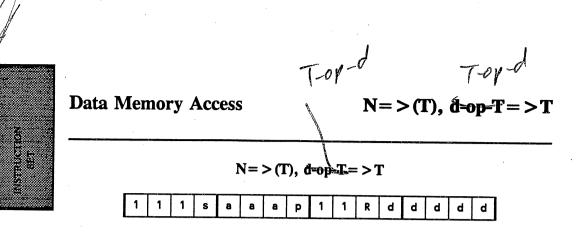

#### **3.1** Instruction Execution

The RTX Microcontrollers have an Instruction Decoder which provides control of all data paths and the Program Counter Register (PC). This hardware determines what function is to be performed by looking at the contents of the Instruction Register (IR), and subsequently determines the sequence of operations through data path control.

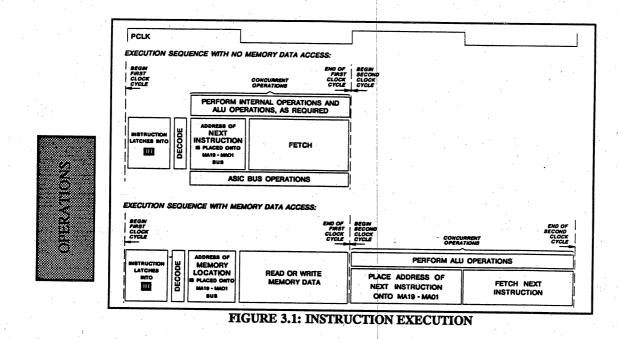

In one-cycle operations, the instruction which is to be executed is latched into IR at the beginning of a clock cycle, then is decoded. All necessary internal operations are performed simultaneously with fetching the next instruction. See Figure 3.1.

Instructions which perform memory access require two clock cycles to be executed. During the first cycle of a memory access instruction, the instruction is decoded, the address of the memory location to be accessed is placed on the Memory Address Bus (MA19-MA01), and the memory data (MD15-MD00) is read or written. During the second cycle, the address of the next instruction to be executed is placed on the Memory Address Bus, and the next instruction is fetched, as indicated in Figure 3.1.

**Operations**, Chapter 3

RTX 2000 Family Programmer's Reference Manual

#### **3.2** Stack Operation

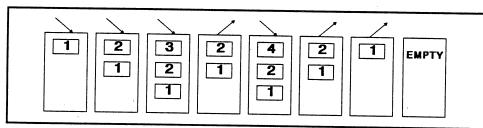

The RTX Microprocessors utilize a Last-in, First-out (LIFO) stack architecture. In this type of architecture, the last data element stored in the memory stack will be the first element retrieved from that region of memory. See Figure 3.2.

**FIGURE 3.2: STACK OPERATION**

This structure for information storage and retrieval provides the computer with one central location for temporary storage of information.

The RTX takes advantage of this architecture, utilizing two separate on-chip stacks. The first, the Parameter Stack, is used for temporary storage of data and for passing parameters between subroutines. The second, the Return Stack, is used to store return addresses during subroutine calls and returns. The Quad  $Bus^{TM}$  architecure of the RTX Microcontrollers allows both stacks to be accessed in parallel by a single instruction, this dual stack arrangement allows overhead to be minimized during subroutine operations. The Return Stack can also be used for temporary storage of values when it is not being used during a subroutine call or return.

For faster access, both the Parameter Stack and the Return Stack utilize registers for the top elements and on-chip memory (Stack Memory) for the remaining elements.

For more detailed information about RTX stack operation, see Section 6.1.

**Operations**, Chapter 3

OPERATIONS

#### **3.3** Subroutine Calls and Returns

An RTX subroutine call instruction has the address of the routine to be called embedded in the instruction. When the subroutine call is executed, the address of the instruction following the call instruction is pushed onto the Return Stack. When the subroutine is completed, a Return-from-Subroutine instruction will pop the return address from the stack, and execution will resume with the instruction following the call.

Subroutine returns take 0 clock cycles if performed as part of another instruction, and 1 cycle if executed as a separate instruction.

RTX 2000 Family Programmer's Reference Manual

#### 3.4 Branching And Looping

The RTX can perform unconditional branches or conditional branches, based on the contents of the top elements of the Parameter and Return Stacks. All branches take one clock cycle, regardless of whether or not the branch is performed.

Operations, Chapter 3

#### **3.5** Streamed Instructions

The RTX processor has a "streamed" instruction feature, in which an instruction is repeated a specified number of times without repeating the instruction fetch cycle. This feature is useful for doing fast data transfers, loops and some math functions.

See Chapter 7, "Instruction Set" for more details about the "streamed" instruction feature.

24

RTX 2000 Family Programmer's Reference Manual

#### 3.6 Math/Logic Operations

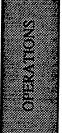

Math and logic operations are performed by the ALU circuitry of the RTX. The operations which may be performed include the simple math operators + and -, and the logic operators AND, OR, XOR, NOR, NAND, XNOR, and NOT.

See Section 6.3 for information about the on-chip hardware multiplier, multiplier/accumulator, barrel shifter, and Floating Point support features.

The TOP register is always one input to the ALU. The second, "Y", input may come from a variety of sources, as indicated in Figure 3.3.

**Operations**, Chapter 3

25

OPERATIONS

#### **3.6.1** Registers And I/O Devices

The contents of the TOP and NEXT registers are always available as operands to the ALU, and are the implicit operands for most of the RTX Math/Logic instructions.

The contents of the other registers and external I/O devices are addressable as devices on the ASIC Bus.

#### 3.6.2 Memory

Data may be fetched from, and stored to, Main Memory using the Word and Byte access instructions (Classes 14 and 15 in Chapter 7, the "Instruction Set") and User memory access instructions (Class 12).

#### 3.6.3 Literals

A literal is a constant value to be pushed onto the stack, or to be used as the second operand of an arithmetic or logic operation. The RTX processor recognizes two types of literals - short literals and long literals.

A short literal is a 5-bit value between 0 and 31 and is encoded as a field in a machine instruction.

A long literal may be any signed or unsigned 16-bit integer, and is stored in main memory immediately following the opcode that utilizes it.

RTX 2000 Family Programmer's Reference Manual

#### **3.7** Stack Operations

The top two locations of the Parameter Stack are TOP and NEXT, and the remainder of the stack memory is located in on-chip RAM. Because of this, the RTX Microcontrollers have the ability to manipulate stack elements to allow optimization of many instructions. Descriptions of these stack manipulation operations are given in the following sections. These primitives can be combined with other operations to allow one-cycle execution of multiple operations. See Chapter 7 for information about specific instructions.

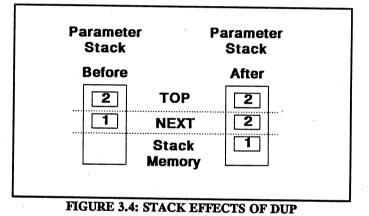

#### 3.7.1 DUP

DUP copies the top element of the Parameter Stack, and pushes the result onto the stack, leaving the stack with two identical elements in the top two stack locations.

**Operations**, Chapter 3

27

**PERATIONS**

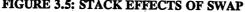

#### 3.7.2 SWAP

SWAP flips the top two elements of the Parameter Stack, causing the top element to move to the second location, and the second element to move to the top location.

| BeforeAfter3TOP2NEXT3        | Parameter<br>Stack |      | Parameter<br>Stack |  |

|------------------------------|--------------------|------|--------------------|--|

|                              | Before             |      | After              |  |

| 2 NEXT 3                     | 3                  | ТОР  | 2                  |  |

|                              | 2                  | NEXT | 3                  |  |

| 1   Stack   1     Memory   1 | 1                  |      | 1                  |  |

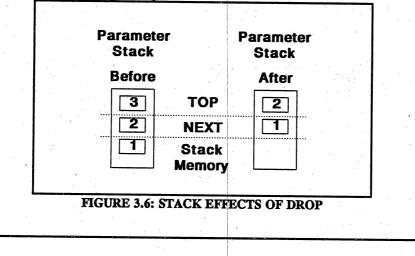

#### 3.7.3 DROP

prop pops the Parameter Stack, dropping the top element. That element is lost, and is not used in subsequent operations.

RTX 2000 Family Programmer's Reference Manual

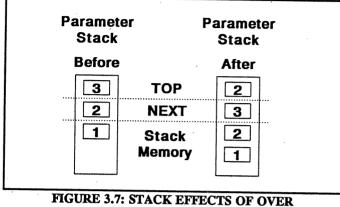

#### 3.7.4 OVER

OVER copies and pushes the third Parameter Stack element into the top location.

#### 3.7.5 >R

>R (called "to R") takes the information in TOP and stores it in the least significant 16 bits (I) of the top location of the Return Stack. This causes the current Code page value to be written to IPR, the most significant 5 bits of the top location of the Return Stack.

But, isn't CPR only 4 bits? what about the 5th IPR bit?

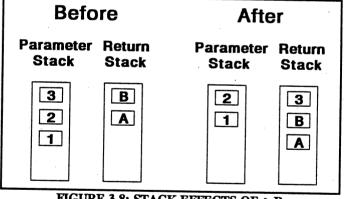

FIGURE 3.8: STACK EFFECTS OF >R

**Operations**, Chapter 3

#### 3.7.6 R>

R> (called "R from") retrieves the information in the least significant 16 bits of the top element of the Return Stack and pushes it into TOP.

| Before             |                 | After              |        |  |

|--------------------|-----------------|--------------------|--------|--|

| Parameter<br>Stack | Return<br>Stack | Parameter<br>Stack | -      |  |

| 2                  | C<br>B<br>A     | C<br>2<br>1        | B<br>A |  |

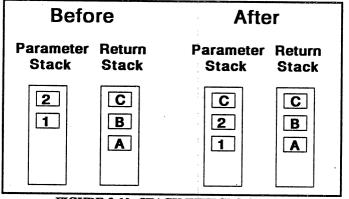

FIGURE 3.9: STACK EFFECTS OF R>

#### 3.7.7 R@

Ra (called "R fetch") copies the top of the Return Stack to the top of the Parameter Stack.

FIGURE 3.10: STACK EFFECTS OF R@

30

RTX 2000 Family Programmer's Reference Manual

#### 3.8 Interrupts

The RTX processor may be interrupted from several sources, both from internal devices and from external inputs.

The on-chip Interrupt Controller has fourteen interrupt request inputs. Thirteen of these interrupt request inputs are maskable interrupts, and one is a Non-Maskable Interrupt (NMI) request.

#### **3.8.1** Maskable Interrupts

The Interrupt Controller samples the request inputs during each instruction, prioritizes any active interrupt requests, and signals the processor when an interrupt request is present.

For more information about interrupt acknowledgement, disabling interrupts, and software interrupts, see Section 6.2.

#### **3.8.2** Non-Maskable Interrupts (NMI)

The NMI is an external, edge-sensitive input which requires a rising edge to request an interrupt.

#### 3.8.2.1 On the RTX 2000

The NMI can cause the processor to perform an Interrupt Acknowledge cycle in the middle of such operations as Step Math instructions, Streamed instructions, and other operations that could result in the loss of data or misoperation of the hardware if interrupted. For this reason, a "Return From Subroutine" should not be performed from the NMI service routine. Instead, the NMI handler should re-initialize the system.

**Operations**, Chapter 3

# 3.8.2.2 On the RTX 2001A

On the RTX 2001A, the NMI input has a glitch filter circuit which requires that the signal that initiates the NMI must last at least two cycles of ICLK.

The NMI can cause the processor to perform an Interrupt Acknowledge cycle in the middle of such operations as Step Math instructions, Streamed instructions, and other operations that could result in the loss of data or misoperation of the hardware if interrupted. For this reason, a "Return From Subroutine" should not be performed from the NMI service routine. Instead, the NMI handler should re-initialize the system.

# **3.8.2.3** On the RTX 2010

On the RTX 2010, the NMI has two modes of operation which are controlled by the NMI\_MODE Flag (bit 11 of the CR).

When CR bit 11 is cleared (=0), the NMI cannot be masked and can interrupt any cycle. This allows a fast response to the NMI, but does not guarantee that a Return From Interrupt will always provide correct operation. The NMI\_MODE Flag is cleared at Reset.

When the NMI\_MODE bit is set (=1), the NMI may be inhibited by the processor during certain critical operations, and further NMIs and maskable interrupts are disabled until the NMI Interrupt Service Routine has been completed and a return has been executed. In this mode, a return from the NMI Interrupt Service Routine will allow the processor to resume correct execution at the point where it was interrupted.

RTX 2000 Family Programmer's Reference Manual

OFFRATIONS

# **CHAPTER 4**

# **RTX REGISTERS**

.

RTX 2000 Family Programmer's Reference Manual

# 4 RTX Registers

The three types of registers which the RTX microcontrollers use are: Stack Related Registers, Internal Processor Registers, and Status/Control Registers.

At power up or Reset, the RTX registers are initialized. The reset states for the RTX 2000 are shown in Table 4.1. The reset states for the RTX 2001A are shown in Table 4.2. The reset states for the RTX 2010 are shown in Table 4.3. In each of these tables, the read and write capabilities of each register are indicated in the  $\mathbf{R}/\mathbf{W}$  column, where:

R-W Indicates that the register can be either read from or written to.

- R Indicates a read-only register.

- W Indicates a write-only register.

- R/W Indicates that the first register is read-only and the second register is write-only (as in the case of the Timer/Counter and Timer Preload Registers).

- \* Indicates that individual bits in the register may be read-only or write-only and that the bit map for that register should be consulted.

- N Indicates that the register cannot be read from or written to.

Register addresses are given in hexadecimal, denoted by "H" here and elsewhere in this manual.

The sections which follow describe each of the registers in more detail.

RTX Registers, Chapter 4

| REGISTER                      | ASIC<br>ADDR      | INITIALIZATION<br>VALUES | R/W               | COMMENTS                                                                                    |

|-------------------------------|-------------------|--------------------------|-------------------|---------------------------------------------------------------------------------------------|

| TOP                           |                   | 0000 0000 0000 0000      | R-W               |                                                                                             |

| NEXT                          |                   | 1111 1111 1111 1111      | R-W               | · · · · · · · · · · · · · · · · · · ·                                                       |

| IR                            |                   | 0000 0000 0000 0000      | N                 |                                                                                             |

| I                             | 00H<br>01H<br>02H | 1111 1111 1111 1111      | R-W               |                                                                                             |

| CR                            | 03H               | 0100 0000 0000 1000      | •                 | Interrupts disabled, BOOT=1, Byte<br>Order=0                                                |

| MD                            | 04H               | 1111 1111 1111 1111      | R-W               |                                                                                             |

| SR                            | 06H               | 0000 0000 0000 0000      | R-W               |                                                                                             |

| PC                            | 07H               | 0000 0000 0000 0000      | R-W               |                                                                                             |

| IMR                           | 08H               | 0000 0000 0000 0000      | R-W               | All interrupts unmasked                                                                     |

| SPR                           | 09H               | 0000 0000 0000 0000      | R-W               | First stack location                                                                        |

| SLR                           | ОВН               | 1111 1111 1111 1111      | W.                | Limit for each stack set to 255                                                             |

| IVR                           | OBH               | 0000 0010 0000 0000      | R                 | Read only; initialized to<br>"No Interrupt Value"                                           |

| IPR                           | ОСН               | 0000 0000 0000 0000      | R-W               | Initialize for Code Page 0                                                                  |

| DPR                           | ODH               | 0000 0000 0000 0000      | R-W               | Initialize for Data Page O                                                                  |

| UPR                           | OEH               | 0000 0000 0000 0000      | R-W               | Initialize for User Page O                                                                  |

| CPR                           | OFH               | 0000 0000 0000 0000      | R-V               | Initialize for Code Page 0                                                                  |

| IBC                           | 10H               | 0000 0000 0000 0000      | •                 | Interrupt Base=0, Counters on<br>internal clocks, no rounding,<br>use CPR for data accesses |

| UBR                           | 11H               | 0000 0000 0000 0000      | R-W               | User Base Address = 0                                                                       |

| TC0/TP0<br>TC1/TP1<br>TC2/TP2 | 13H<br>14H<br>15H | 0000 0000 0000 0000      | R/W<br>R/W<br>R/W | All Timer/Counters set to<br>time-out after 65536 counts                                    |

| MLR                           | 16H               | 1111 1111 0000 0000      | R                 | Read only; Mult. Low Product                                                                |

| MHR                           | 17H               | 1111 1111 1111 1111      | R                 | Read only; Mult. High Product                                                               |

# TABLE 4.1: RTX 2000 REGISTER INITIALIZATION

RIX REGISTERS

36

RTX 2000 Family Programmer's Reference Manual

| REGISTER                      | ASIC              | INITIALIZATION<br>VALUES | R/W               | COMMENTS                                                                                    |

|-------------------------------|-------------------|--------------------------|-------------------|---------------------------------------------------------------------------------------------|

| TOP                           |                   | 0000 0000 0000 0000      | R-W               |                                                                                             |

| NEXT                          |                   | 1111 1111 1111 1111      | R-W               |                                                                                             |

| IR                            |                   | 0000 0000 0000 0000      | N                 |                                                                                             |

| I                             | 00H<br>01H<br>02H | 1111 1111 1111 1111      | R-W               |                                                                                             |

| CR                            | 03H               | 0100 0000 0000 1000      | •                 | Interrupts disabled, BOOT=1,<br>Byte Order=0                                                |

| MD                            | 04H               | 1111 1111 1111 1111      | R-W               |                                                                                             |

| SR                            | 06H               | 0000 0000 0000 0000      | R-W               |                                                                                             |

| PC                            | 07H               | 0000 0000 0000 0000      | R-W               |                                                                                             |

| IMR                           | 08H               | 0000 0000 0000 0000      | R-W               | All interrupts unmasked                                                                     |

| SPR                           | 09H               | 0000 0000 0000 0000      | R-W               | Stack start addresses set to 0                                                              |

| SUR                           | OAH               | 0000 0011 0000 0011      | R-W               | Stack underflow limits set                                                                  |

| SVR                           | ОВН               | 1111 1111 1111 1111      | W                 | Write only; each stack overflow<br>limit set for max. stack size                            |

| IVR                           | OBH               | 0000 0010 0000 0000      | R                 | Read only; Interrupt Vector init-<br>ialized to "No Interrupt" value                        |

| IPR                           | OCH               | 0000 0000 0000 0000      | R-W               | Initialized for Code Page 0                                                                 |

| DPR                           | ODH               | 0000 0000 0000 0000      | R-W               | Initialized for Data Page 0                                                                 |

| UPR                           | OEH               | 0000 0000 0000 0000      | R-W               | Initialized for User Page 0                                                                 |

| CPR                           | OFH               | 0000 0000 0000 0000      | R-W               | Initialized for Code Page 0                                                                 |

| BC                            | 10H               | 0000 0000 0000 0000      | *                 | Interrupt Base=0, Counters on<br>internal clocks, no rounding,<br>use CPR for data accesses |

| UBR                           | 118               | 0000 0000 0000 0000      | R-W               | User Base address set to O                                                                  |

| TC0/TP0<br>TC1/TP1<br>TC2/TP2 | 13H<br>14H<br>15H | 0000 0000 0000 0000      | R/W<br>R/W<br>R/W | All Timer/Counters set to<br>time-out after 65536 counts                                    |

| x                             | 16H               | 0000 0000 0000 0000      | R-W               | Scratchpad/Counting Register                                                                |

| н                             | 17H               | 0000 0000 0000 0000      | R-W               | Scratchpad Register                                                                         |

# TABLE 4.2: RTX 2001A REGISTER INITIALIZATION

**RTX REGISTERS**

RTX Registers, Chapter 4

| REGISTER                      | ASIC<br>ADDR      | INITIALIZATION<br>VALUES | R/W               | COMMENTS                                                                                    |

|-------------------------------|-------------------|--------------------------|-------------------|---------------------------------------------------------------------------------------------|

| тор                           |                   | 0000 0000 0000 0000      | R-W               |                                                                                             |

| NEXT                          |                   | 1111 1111 1111 1111      | R-W               | ·                                                                                           |

| IR                            |                   | 0000 0000 0000 0000      | - N               |                                                                                             |

| I                             | 00H<br>01H<br>02H | 1111 1111 1111 1111      | R-W               |                                                                                             |

| CR                            | 03H               | 0100 0000 0000 1000      | *                 | Interrupts disabled, BOOT=1,<br>Byte Order=0                                                |

| MD                            | 04H               | 1111 1111 1111 1111      | R-W               |                                                                                             |

| SR                            | 06H               | 0000 0010 0000 0000      | R-W               |                                                                                             |

| PC                            | 07H               | 0000 0000 0000 0000      | R-W               |                                                                                             |

| IMR                           | 08H               | 0000 0000 0000 0000      | R-W               | All interrupts unmasked                                                                     |

| SPR                           | 09H               | 0000 0000 0000 0000      | R-W               | Stack start addresses set to O                                                              |

| SUR                           | OAH               | 0000 0111 0000 0111      | R-W               | Stack underflow limits set                                                                  |

| SVR                           | ОВН               | 1111 1111 1111 1111      | W                 | Write only; each stack overflow<br>limit set for max. stack size                            |

| IVR                           | OBH               | 0000 0010 0000 0000      | R                 | Read only; Interrupt Vector init-<br>ialized to "No Interrupt" value                        |

| IPR                           | OCH               | 0000 0000 0000 0000      | R-W               | Initialized for Code Page 0                                                                 |

| DPR                           | ODH               | 0000 0000 0000 0000      | R-W               | Initialized for Data Page 0                                                                 |

| UPR                           | OEH               | 0000 0000 0000 0000      | R-W               | Initialized for User Page 0                                                                 |

| CPR                           | OFH               | 0000 0000 0000 0000      | R-W               | Initialized for Code Page 0                                                                 |

| IBC                           | 10H               | 0000 0000 0000 0000      | *                 | Interrupt Base=0, Counters on<br>internal clocks, no rounding,<br>use CPR for data accesses |

| UBR                           | 118               | 0000 0000 0000 0000      | R-W               | User Base address set to 0                                                                  |

| MXR                           | 12H               | 0000 0000 0000 0000      | R-W               | MAC Extension Register; LZD 0 Count;<br>Barrel Shifter Count                                |

| TC0/TP0<br>TC1/TP1<br>TC2/TP2 | 13H<br>14H<br>15H | 0000 0000 0000 0000      | R/W<br>R/W<br>R/W | All Timer/Counters set to<br>time-out after 65536 counts                                    |

| MLR                           | 16H               | 0000 0000 0000 0000      | R-W               | Multiplier and MAC Low Register                                                             |

| MHR                           | 17H               | 0000 0000 0000 0000      | R-W               | Multiplier, Barrel Shifter, and LZD<br>High Register; MAC Middle Register                   |

# TABLE 4.3: RTX 2010 REGISTER INITIALIZATION

RTX REGISTERS

38

RTX 2000 Family Programmer's Reference Manual

# 4.1 Stack Related Registers

These registers contain the top elements of the Parameter and Return Stacks, and are the implicit source and destination for many of the processor operations.

#### 4.1.1 TOP Register

#### (Parameter Stack)

The TOP Register contains the top element of the Parameter Stack, and has no ASIC address assignment.

This is the primary working register for the processor, and is the implicit data source or destination for certain instructions.

All ALU results are loaded into TOP. The output from TOP may be written to any ASIC Bus register and to external I/O devices.

#### 4.1.2 NEXT Register

## (Parameter Stack)

The NEXT Register contains the second element of the Parameter Stack, and has no ASIC address assignment.

During arithmetic operations, this register holds the lower 16 bits of a 32-bit operand. NEXT is also the source of data for all memory writes.

RTX Registers, Chapter 4

KIX REGISTERS

#### 4.1.3 I Register

**RTX REGISTERS**

40

#### (Return Stack)

The Index Register, I, can be accessed at three different ASIC addresses, and the choice of ASIC address determines the type of operation to be performed.

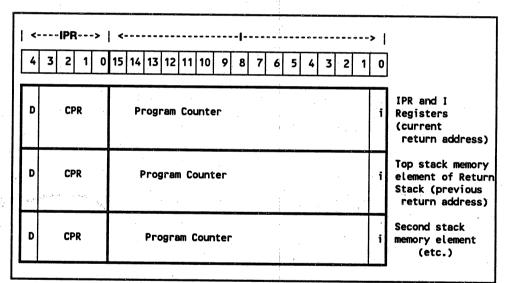

As a Stack Related Register at ASIC addresses 00H (Hex) and 01H, I contains the lower 16 bits of the top element of the 21-bit wide Return Stack. IPR contains the other 5 bits. See Section 4.1.4 for more details about IPR.

The contents of I may be accessed in either push/pop mode, in which values are moved to/from Return Stack memory as required, or in read/write mode in which the Return Stack is not affected.

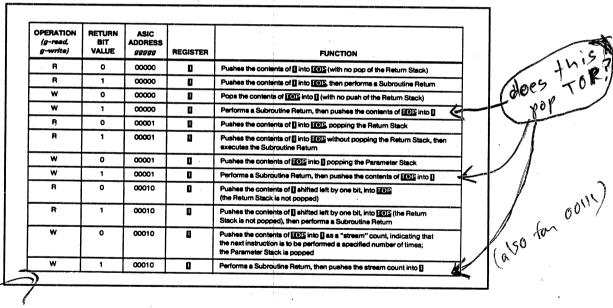

In addition to its use in holding return address bits, at ASIC address 02H, this register is also used to hold the count for streamed (repeated) instructions and loop instructions. Operation of I at this ASIC address is described in more detail in Section 4.1.3.3. I access operations and the associated addresses are shown in Table 4.4.

#### TABLE 4.4: I ACCESS OPERATIONS

#### **4.1.3.1** I

#### At Address 00H

Location 00H is used to access I without causing any <u>net</u> pushes or pops of the Return Stack.

Reading from this location pushes the contents of I onto the Parameter Stack.

Reading from this location as part of a subroutine return pushes the contents of I onto the Parameter Stack, then performs a Return-From-Subroutine.

Writing to this location during normal operation pops the top item on the Parameter Stack into I; the original contents of I are lost.

Writing to this location as part of a subroutine return operation first executes the return, then pushes the top item of the Parameter Stack onto the Return Stack.

#### **4.1.3.2** I

At Address 01H

I at address 01H is used to push and pop the Return Stack.

Reading this location during normal operation pushes the contents of I onto the Parameter Stack and pops the Return Stack.

Reading this location as part of a subroutine return operation pushes the contents of I onto the Parameter Stack without popping the Return Stack, then executes the subroutine return. See Section 5.1.1 for more information about operation during subroutine returns.

Writing to this location during normal operation pushes the top item from the Parameter Stack onto the Return Stack, popping the Parameter Stack.

Writing to this location as part of a subroutine return operation first executes the subroutine return, then pushes the top Parameter Stack item onto the Return Stack. See Section 5.1.1 for more information about subroutine return operation.

RTX Registers, Chapter 4

# 4.1.3.3 I At Address 02H (Stream Count/Loop Count)

Reading this location pushes the contents of I shifted left by one bit onto the Parameter Stack. The Return Stack is not popped.

Reading this location as part of a subroutine return pushes the contents of I shifted left by one bit into TOP (the Return Stack is not popped), and then performs a Return-From-Subroutine.

Writing to this location during normal operation pushes the top Parameter Stack item into I as a "stream" count, indicating that the next instruction is to be performed a specified number of times, the Parameter Stack is popped.

Writing to this location as part of a subroutine return operation executes the subroutine return first, then pushes the stream count onto the Return Stack.

See Section 7.1.1 for more information on streamed instructions.

RTX 2000 Family Programmer's Reference Manual

42

RTX REGISTERS

#### 4.1.4 IPR Register

(Return Stack)

The IPR Register, at ASIC Address 0CH (Hex), can be described as both a Stack Related Register and as a Control/Status Register. See Section 4.3.10 for more information. This register contains the 5 most significant bits of the top element of the Return Stack (the I Register contains the other 16 bits).

Reading from or writing directly to IPR does not push or pop the Return Stack, but pushes or pops of the Return Stack (when reading or writing to I) do cause the contents of IPR to be overwritten. Writing to I during non-subroutine operations causes the current Code Page value to be written to IPR.

G what about bit 4? Is this loaded with PPRSEL?

RTX Registers, Chapter 4

# 4.2 Internal Processor Registers

Internal Processor Registers are not directly accessible to the programmer.

The Instruction Register, IR, is actually a latch which contains the instruction currently being executed. This register is loaded directly from main memory via an instruction fetch, and is not accessible under program control.

The bits of the instruction in IR are decoded to determine which operations to perform, to determine the location of the next instruction to be executed, and to provide data for immediate operations.

57 VC W

RTX 2000 Family Programmer's Reference Manual

44

RTX REGISTERS

# 4.3 Control/Status Registers

The contents of the RTX microcontroller's Control/Status Registers determine the operating environment for the processor, and allow the processor to monitor and control the various I/O devices on the chip.

All internal registers are accessed through the ASIC Bus. ASIC addresses  $\emptyset'$  through 23 (17 hexadecimal) are assigned to on-chip registers and devices, and are described in this section. Section 7.7 describes the RTX instructions which access the ASIC Bus.

addresses 0, 1,2 ave in previous sections yes, this is a nit.

RTX REGISTERS

RTX Registers, Chapter 4

# 4.3.1 The Configuration Register - Address 03H

The Configuration Register, CR, controls the setup/status of the RTX processor.

Reading this location pushes the current contents of the register onto the Parameter Stack.

Writing to this location pops the top Parameter Stack item into CR, updating the control bits. The Interrupt Base/Control Register contains additional processor control bits.

The bits in CR are assigned as shown in Table 4.5.

RTX 2000 Family Programmer's Reference Manual

# TABLE 4.5: CONFIGURATION REGISTER BIT ASSIGNMENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MSB | IL  | RID | †R<br>AR | ES RES<br>CE   | TRES           | RES                    | RES                   | RES                 | RES                                       | RES          | RES                | SID                      | BOOT                    | BYTE            | = C       | CY           | CY                | LSB                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----------|----------------|----------------|------------------------|-----------------------|---------------------|-------------------------------------------|--------------|--------------------|--------------------------|-------------------------|-----------------|-----------|--------------|-------------------|-----------------------------------------------------------------------------------------------------------------|

| 8000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | II  | _   | + -      | it 15<br>(MSB) | 1              | ndica                  | ates                  | that                | terru<br>t an<br>Sect                     | inte         | erru               | pt r                     | hen s<br>eques          | et to<br>t is   | o 1       | ,            |                   | 3                                                                                                               |

| 4.020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | RI  | ID  | В        | it 14          | o<br>i<br>R    | f Int<br>ndica         | terru<br>ates<br>5 to | upt [<br>that<br>1. | ad In<br>Disabl<br>t into<br>Use S<br>.2. | le b<br>erru | pit.<br>pts        | Wheare                   | en se<br>disa           | t to<br>bled.   | 1,        |              |                   | ~ 3,8.2.3                                                                                                       |

| 2.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 4 ' | RES | В        | it 13          | OI<br>P(       | n the<br>CLK c         | e RT)<br>:ycle        | ( 201<br>e for      | ne RT)<br>10: V<br>ever<br>e Sect         | ihen<br>'y A | thi<br>SIC         | is b <sup>.</sup><br>bus | it is<br>read           | set,<br>is      | t         |              |                   |                                                                                                                 |

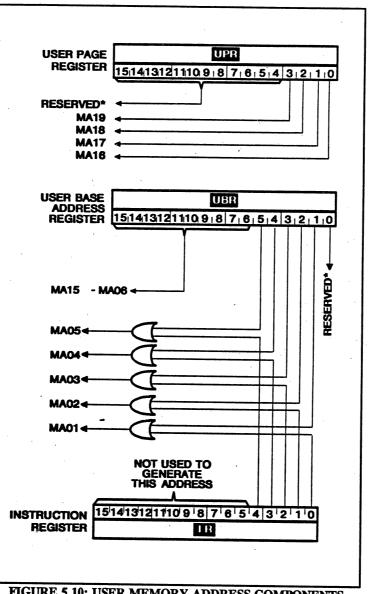

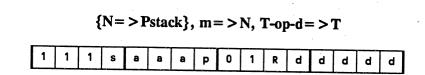

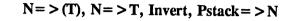

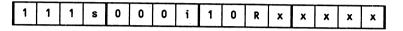

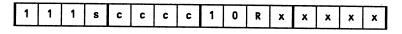

| 1300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2   | RE  | S   | В        | it 12          | Re             | eserv                  | red                   |                     |                                           |              |                    |                          |                         |                 |           |              |                   | Ž                                                                                                               |